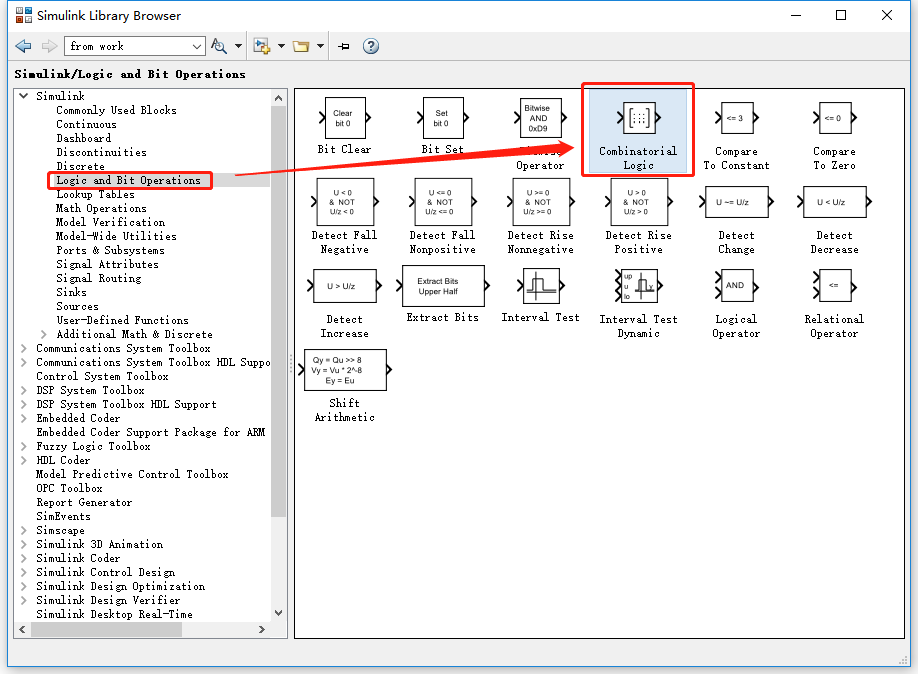

模块概要

模块名称:Combinatorial Logic

所在库:Logic and Bit Operations

模块功能:

实现真值表。

模块外形:

默认参数:

模块分析:

默认参数中的真值表为3路输入,2路输出。

由于有3路输入,因此真值表中有2^3 = 8行。

每一行的输出元素有2个。

实例分析

1,加法电路

假设现在要实现一个带进位的加法电路。参考:

https://blog.csdn.net/booksyhay/article/details/80704522

【需求】

输入:3路,分别为A、B、C

输出:2路,分别为HI、LO

要求:对A、B、C这三个一位的二进制相加,计算结果为一个两位的二进制数,分别为高位HI和低位LO。

真值表为:

| A | B | C | HI | LO |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

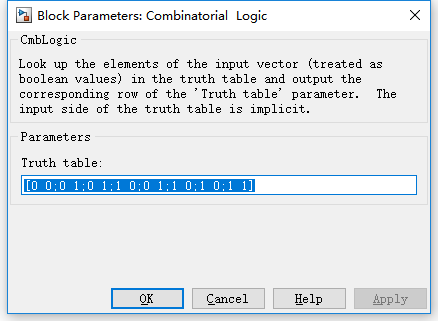

Combinatorial Logic模块的参数为HI和LO对应的矩阵,即:

0 0;

0 1;

0 1;

1 0;

0 1;

1 0;

1 0;

1 1;

刚好就是默认参数 [0 0;0 1;0 1;1 0;0 1;1 0;1 0;1 1] !!

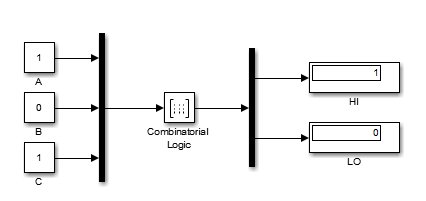

【验证】

搭建以下模型,可以验证结果。

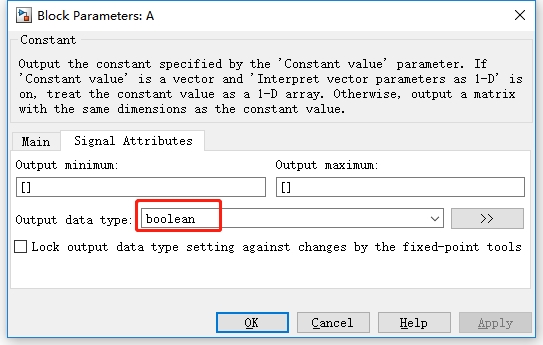

注意:A、B、C这三个constant模块的输出类型要改为boolean型。

2,RS触发器电路

假设现在要实现一个RS触发器。

参考电路:https://blog.csdn.net/booksyhay/article/details/82492913

【需求】

输入:2路信号,R和S

输出:2路信号,Q和!Q

要求:

- 当R和S不相同时,输出Q取决于R和S的值。当R为1,则Q=1;当S为1,则Q=0;

- 当R和S相同时,输出Q保持不变。

- Q和!Q为互补的值。

分析

先整理出RS触发的真值表:

| R | S | Q |

| 0 | 0 | Q0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | Q0 |

由于输出需要“保持”上一次的结果,因此需要一个memory模块。

Combinatorial Logic模块有3个输入,2个输出。

完整的真值表为:

| Q0 | S | R | Q | !Q |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 |

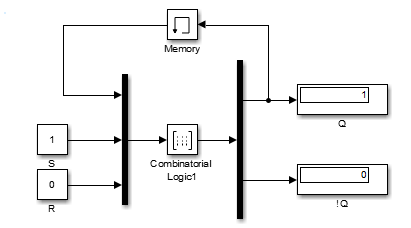

搭建模型

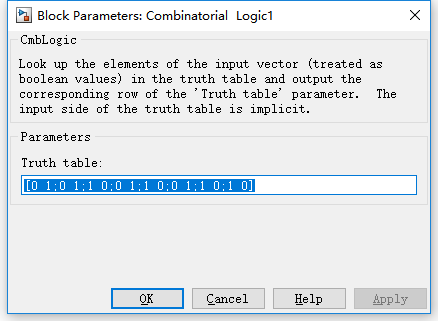

模块参数为:

[0 1;0 1;1 0;0 1;1 0;0 1;1 0;1 0]

参考资料

Combinatorial Logic

https://ww2.mathworks.cn/help/simulink/slref/combinatoriallogic.html

最后

以上就是典雅大神最近收集整理的关于Simulink建模与仿真学习笔记之组合逻辑(Combinatorial Logic)模块概要实例分析参考资料Combinatorial Logic的全部内容,更多相关Simulink建模与仿真学习笔记之组合逻辑(Combinatorial内容请搜索靠谱客的其他文章。

![[数据库] Navicat for MySQL触发器更新和插入操作](https://www.shuijiaxian.com/files_image/reation/bcimg25.png)

发表评论 取消回复