一、引言

采用逻辑门和MSI模块来进行组合逻辑电路的设计,需要我们根据实验的需求和电路的功能要求,明确输出量与输入量之间的关系,即得到一张真值表(或者是功能表)。根据这张真值表,我们还需要将其转化成逻辑函数,即用逻辑语言来描述输出量与输入量之间的关系,替代这一张庞大的真值表。只有明确地表示出输出量与输入量之间对应的函数关系或者功能模块的逻辑关系,才有办法搭建逻辑门或者MSI模块使不同的输入量实现对应的输出。

要想根据电路的功能需求得到一张真值表并不困难,只需要将每种输入和其对应的输出情况排列出来即可。而从真值表转化到逻辑函数,需要我们掌握一些方法和技巧,常见的方法有两种:①卡诺图法:先根据真值表写出逻辑函数的最小项和最大项表达式,再根据卡诺图来进行化简,得到最简与或式和最简或与式。②观察法:直接在真值表中,观察输出与输入之间的关系,就可以写出与或式和或与式,但这样得到的与或式和或与式不一定是逻辑函数的最简形式,可能需要我们通过卡诺图进行检验和化简。

我们今天的重点是教大家使用第②种方法,即如何在真值表中通过观察法描述输出量与输入量之间的关系,得到逻辑函数的与或表达式和或与表达式。

二、与或表达式

要想从真值表中得到一个与或表达式,我们需要根据或运算的特点:等号右边的每一项只要有一项为1,那么或运算表达式的结果一定为1。也就是说,我们用不同的乘积项组合表示出真值表中所有输出结果为1的情况即可。

具体的实现方法是:我们需要在真值表中找到输出为1的行,观察该行对应的输入项有什么特点,能够使得输出一定为1而不是为0。这个特点可以表示成输入项之间的乘积形式(&),成为与或式的其中一项。

我们可以来看这样一个例子:要求用4位全加法器芯片7483实现1位8421BCD码加法器。我们都知道,7483是4位二进制加法器,其进位规则是逢16进1,而8421BCD码表示的是十进制数,进位规则是逢10进1,所以直接用7483加法器让两个8421BCD码相加时,如果和≤9,结果正确,如果和≥10,结果将出现误差。用7483实现BCD码相加时,关键在于确定何时对结果进行修正,以及如何修正。

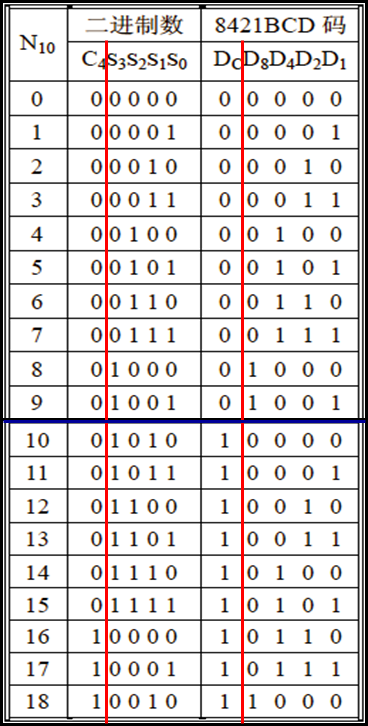

显然,我们需要先通过7483全加器芯片来实现两个BCD码的相加,但此时得到的结果是一个二进制数,并不是8421BCD码,所以我们还需要一个校正电路,来实现7483相加后的结果(二进制数)到8421BCD码(十进制数)的一个转化。要设计这个校正电路,我们需要先分析校正电路需要实现的输出与输入之间的关系,列出真值表如下图所示:

真值表中的N10为两个BCD码相加用十进制数表达的结果(范围只可能从0 - 18)。比较表中的输出和输入可以发现,当N10≤9时,8421BCD码的进位DC为0,二进制数与8421BCD码相同;当N10≥10时,8421BCD码的进位DC为1,8421BCD码就比相应的二进制数大6。那么我们如何知道N10什么时候≤9,什么时候≥10呢?不难发现,只需要根据DC是否为1来判断。

当DC = 0时,校正电路的输出也就是7483输出的结果;当DC = 1时,将7483的输出值与(0110)2相加,就可以实现输出值的修正。也就是说,校正电路也需要一个全加器来实现,相加的两个数分别为上一级7483全加器输出的结果和(0DCDC0)2。所以问题分析的关键变成:如何从真值表中得到输出DC与输入(C4S3S2S1S0)之间的关系?那这个问题就是我们今天的重点了,我们可以通过观察,用与或式将DC的逻辑函数给表达出来。

我们将上面提到的重点重复一遍!“我们需要在真值表中找到输出为1的行,观察该行对应的输入项有什么特点,能够使得输出一定为1而不是为0。这个特点可以表示成输入项之间的乘积形式(&),成为与或式的其中一项”

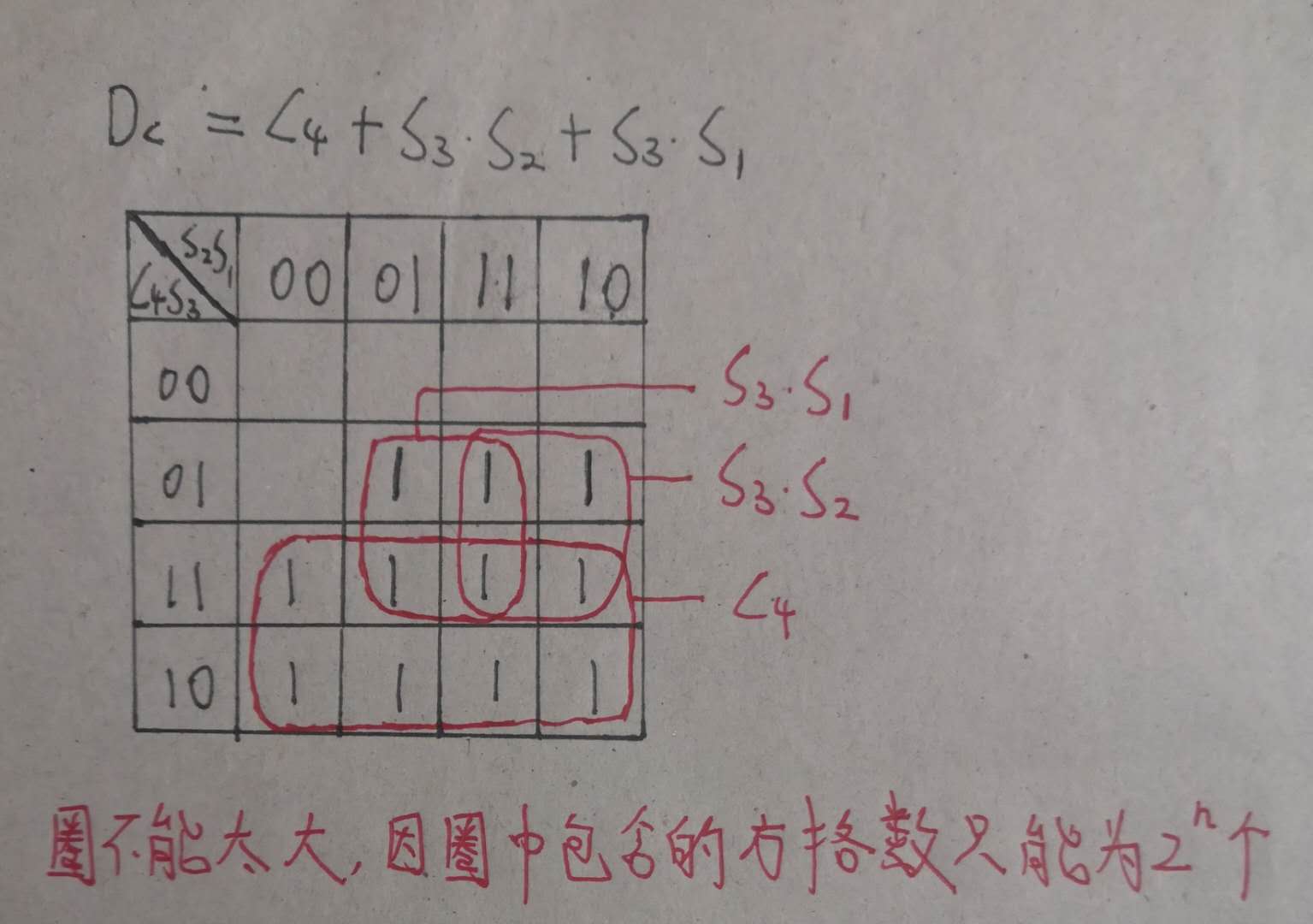

对应到这个例子中,我们观察输出DC为1的行,不难发现如果输入C4为1,那么DC一定为1,那么C4就是这个与或式的其中一项。但是还有C4不为1的输入项能够使得输出DC也为1,那么这些输入项具有什么特点呢?我们又可以发现,如果输入S3和S2同时为1,那么输出DC也一定为1,故可将这一特点表示成输入项之间乘积的形式,即S3·S2,这又可以成为与或式中的其中一项(意思是:只有S3和S2同时取1,才能使得这个与运算的结果为1,进而使得DC与或表达式的结果为1)。同理,我们可以发现如果输入S3和S1同时为1,那么输出DC也一定为1,所以可以表示为S3·S1。

至此,我们已经找到了能使且仅能使输出DC = 1的所有可能特点,故可以写出DC的与或式:DC = C4 + S3·S2 + S3·S1。

三、或与表达式

我们当然也可以将DC表示成或与式的形式,依据的原理就是与运算的特点:等号右边的每一项只要有一项为0,那么与运算表达式的结果一定为0。也就是说,我们用不同的加和项(或运算)组合表示出真值表中所有输出结果为0的情况即可。

具体的实现方法是:我们需要在真值表中找到输出为0的行,观察该行对应的输入项有什么特点,能够使得输出一定为0而不是为1。这个特点可以表示成输入项之间的加和形式(+),成为或与式的其中一项。

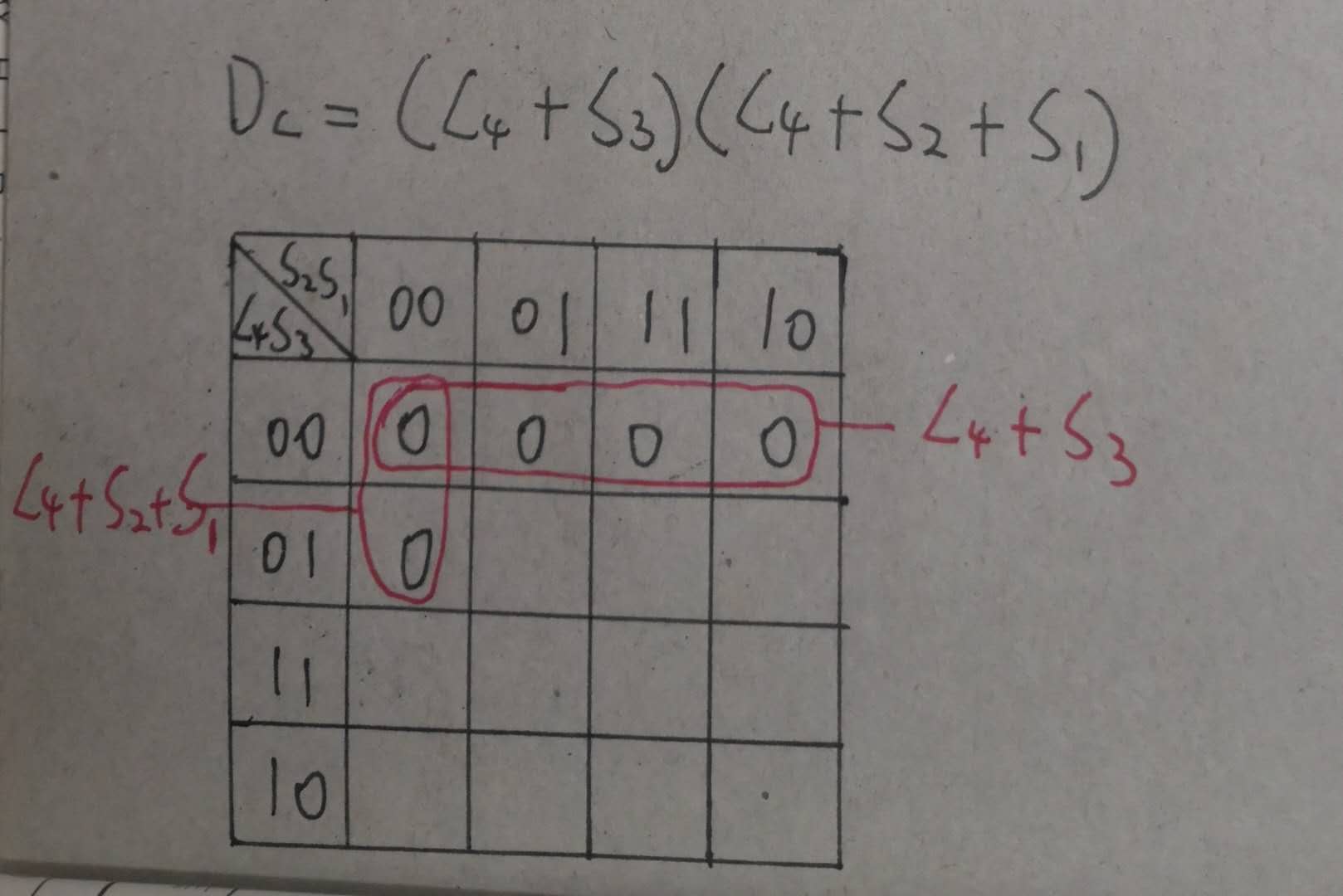

对应到这个例子中,我们观察输出DC为0的行,不难发现如果输入C4和S3全都为0,那么输出DC一定为0,故可将这一特点表示成输入项之间加和的形式,即(C4 + S3),这可以成为或与表达式中的一项(意思是:只有C4和S3同时取0,才能使得这个或运算的结果为0,进而使得DC或与表达式的结果为0)。为了对应完DC为0的所有情况,我们还要寻找其他的特征,又可以发现如果输入C4和S2以及S1同时为0,那么输出DC也一定为0,所以可以将这一特点表示成(C4 + S2 + S1),这是或与表达式的另外一项。

至此,我们已经找到了能使且仅能使输出DC = 0的所有可能特点,故可以写出DC的或与式:DC = (C4 + S3)(C4 + S2 + S1)。

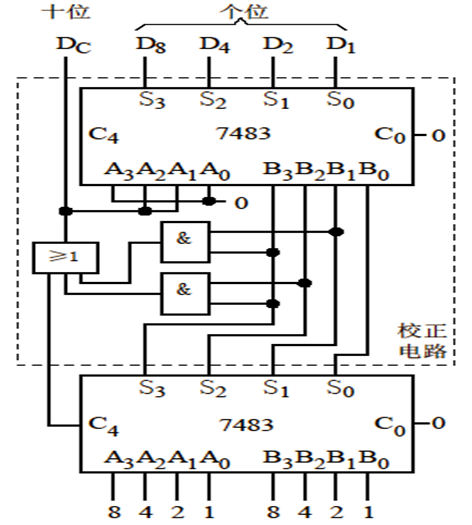

四、电路的实现

根据DC的与或式或者或与式,我们自然地就可以设计出上述例题对应的校正电路了,这里以DC的与或式:DC = C4 + S3·S2 + S3·S1 为例,用两片4位全加器芯片7483设计出一位BCD码的加法运算电路,如下图所示:

五、表达式的化简

用观察法从真值表中得到的与或式和或与式不一定是最简的形式,我们可以通过代数法或者卡诺图来进行检验和化简。当然,如开篇引言所说,我们也可以直接从真值表转化到卡诺图中进行最简与或式和最简或与式的求解。但先在真值表中观察写出表达式的方法,可能消去了一些输入量,在某种程度上比直接使用卡诺图更为快速。下图展示了将上述例题通过观察法得到的两个表达式进行卡诺图检验的结果,结果表明该与或式和或与式已经是最简的形式。而且,该卡诺图只含有4个输入量,若直接根据最小项或最大项表达式画卡诺图,将会含有5个输入量。

最后

以上就是甜美便当最近收集整理的关于【组合逻辑电路】如何从真值表中求解逻辑函数?的全部内容,更多相关【组合逻辑电路】如何从真值表中求解逻辑函数内容请搜索靠谱客的其他文章。

发表评论 取消回复