一、实验预习要求

1、复习触发器的相关内容,掌握触发器的各种表示方法及逻辑功能。

2、理解各触发器之间的相互转换原理。

3、掌握由JK 触发器转换成D 触发器、T 触发器、T’触发器的基本方法。

二、实验目的

1、掌握本RS、JK、D和T触发器的逻辑功能及测试方法,了解它们的触发方法。

2、熟悉常用集成触发器的型号及外引脚排列。

3、熟悉触发器之间相互转换的方法。

4、掌握和熟练应用各种集成触发器。

5、学会用JK 和D触发器构成简单时序逻辑电路的方法。

三、实验原理

触发器是一个具有记忆功能的二进制信息存储器件,是组成时序电路的最基本单元,也是数字电路中另一种重要的单元电路,它在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。触发器有集成触发器和门电路组成的触发器。按其逻辑功能分,有RS触发器,JK触发器,D触发器,T触发器,T’触发器等。

1、基本SR触发器

图5.1为由两个与非门交叉耦合构成的基本SR触发器,这是无时钟控制低电平直接触的触发器。它有两个输出端、和两个输入端、,输入信号名称的小标“D”,表示输入信号直接(Direct)控制触发器的输出。通常称为置“1”端,因为()时触发器被置“1”; 为置“0”端,因为()时触发器被置“0”,当时状态保持;当时,触发器状态不定,应避免此种情况发生。

2、集成JK触发器

集成JK触发器有主从结构和边沿结构两种类型,本实验采用的是TTL型中速边沿结构的双下降沿JK触发器74LS112,其引脚排列及逻辑符号如图5.2。在图5.2逻辑符号图中,CP输入端加小圆圈代表低电平有效、小三角代表边沿触发,即在时钟脉冲CP的后沿(负跳变)发生翻转,它具有置0、置1、计数和保持功能。

3、集成D触发器

本实验采用的是集成双D触发器74LS74,其引脚排列及逻辑符号如图5.3。在图5.3中,D为输入端,、为输出端,为时钟脉冲输入端。为异步置位端,低电平有效。为异步复位端,低电平有效。和的优先权高于D和CP,当不使用时,必须接高电平(或接到电源+5V上),不允许悬空,否则容易引入干扰信号,使触发器误动作,GND为接地端。这种D触发器的输出状态更新发生在脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前输入端D的状态。

4、T触发器和T’触发器

T触发器具有计数和保持功能,T’触发器具有计数功能,它们可以通过D触发器或JK触发器转换来实现。D触发器的D端与Q’端相连即构成T’触发器,在时钟脉冲CP的前沿(正跳变)发生翻转。利用下降沿JK触发器在其JK两端都接1时即成为T’触发器,在时钟脉冲CP的后沿(负跳变)发生翻转。

四、实验设备与器件

1、TH-SZ型数字系统设计实验箱;

2、74LS00 四2输入与非门,74LS112 双下降沿JK触发器,74LS74 双上升沿D触发器,74LS08 四2输入与门;

3、导线/插接线若干。

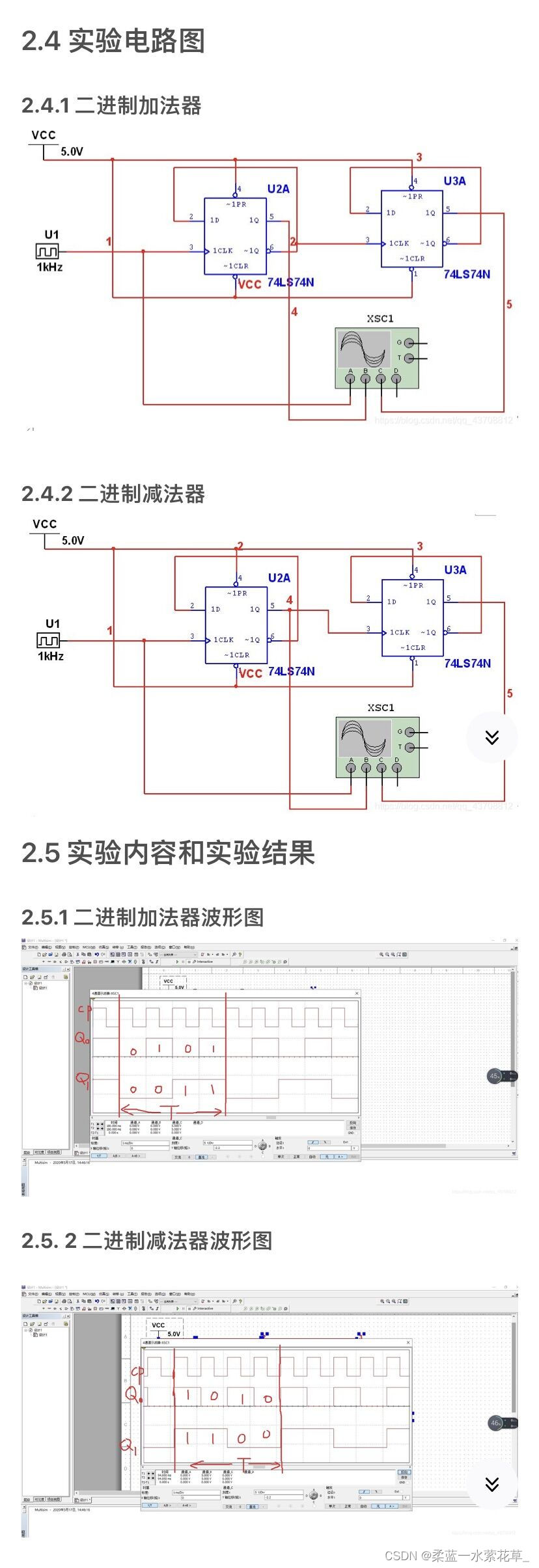

五、实验内容:用74LS74设计2位二进制加法和减法计数器(Multisim仿真)

最后

以上就是想人陪泥猴桃最近收集整理的关于实验7.7 集成触发器及应用的全部内容,更多相关实验7.7内容请搜索靠谱客的其他文章。

发表评论 取消回复