用Verilog HDL设计曼切斯特编码器

曼切斯特码:为一种时钟同步的编码技术,被物理层用来同步一个位流的时钟和数据,编码的规则为用01两位码表示0码,用10两位码表示1,用一个周期的正负对称方波来表0,反相波形为1;

E.G.Thomas规定1为高跳变到底,0为底跳变到高。

IEEE802.4规定1为低跳变到高,0为高跳变到低。`

同时求助一道题:进行一个运算单元的电路设计,A[7:0]*11111011,请用最少的逻辑资源来实现,写出对应的RTL代码。能有比用两个寄存器一个为八位固定寄存器,一个为17位的右移位寄存器占用资源更少的解法码?

module Manche(rst,clk,data,out);

parameter integer half_clk=50;

input rst,clk;

input data;

output out;

reg out;

always@( posedge clk or negedge rst)

begin

if(!rst)

out=1'b0;

else

begin

if(data==1'b1)

begin

out=~clk;

#half_clk out=~out;

end

if(data==1'b0)

begin

out=clk;

#half_clk out=~out;

end

end

end

endmodule

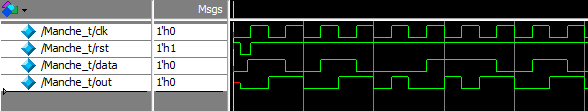

module Manche_t;

reg clk,rst;

reg data;

wire out;

initial

begin

clk=1'b0;

rst=1'b1;

#20 rst=1'b0;

#30 rst=1'b1;

end

always #50 clk=~clk;

initial

begin

data=1'b0;

#40 data=1'b1;

#110 data=1'b0;

#100 data=1'b1;

#100 data=1'b0;

#200 data=1'b1;

#200 data=1'b0;

#100 data=1'b1;

#100 data=1'b0;

end

Manche U1(.rst(rst),.clk(clk),.data(data),.out(out));

endmodule

最后

以上就是追寻苗条最近收集整理的关于一天一道Verilog编程题(五)的全部内容,更多相关一天一道Verilog编程题(五)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复