时序电路的一些元件

- 1. Latch (锁存器)

- 1.1 SR latch with NOR gates

- 1.2 SR latch with NAND gates

- 1.3 SR latch with control input (with NAND gates)

- 1.4 D latch with control input (with NAND gates)

- 2. Flip-Flop (触发器)

- 2.1 D Type Master-Slave Flip-Flop

- 2.2 JK Type Master-Slave Flip-Flop

- 2.3 Edge-Triggered JK Flip-Flop

- 2.4 Toggle Flip-Flop

- 2.5 为什么会有Master-slave和Edge-triggered之分呢?

- 3. 总结触发器的符号表示

- 4. Setup time & Holding time

1. Latch (锁存器)

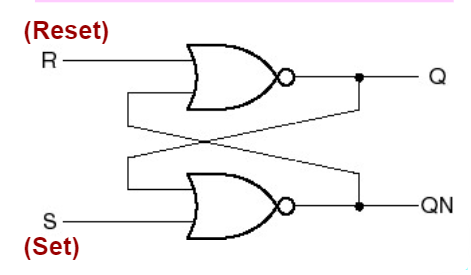

1.1 SR latch with NOR gates

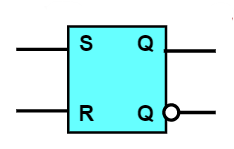

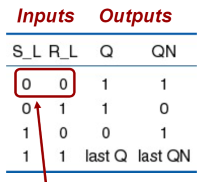

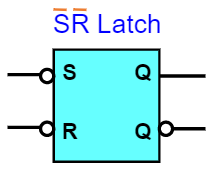

1.2 SR latch with NAND gates

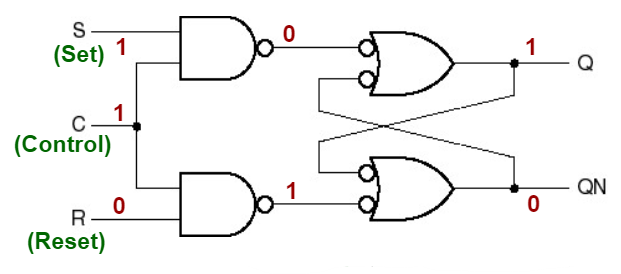

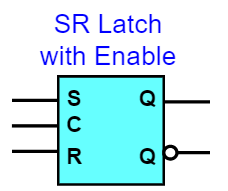

1.3 SR latch with control input (with NAND gates)

当C = 1时,输入为有效;当C = 0时,输入无效。

Q = 1, QN = 0是SET状态;Q = 0, QN = 1是RESET状态。

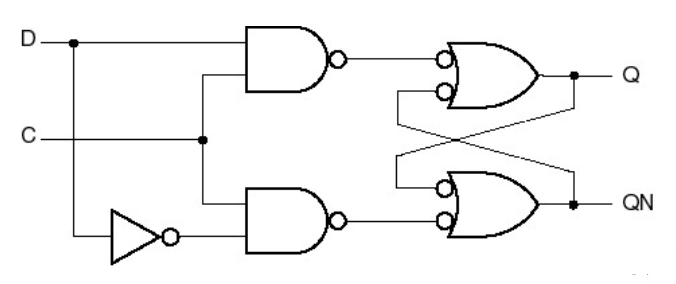

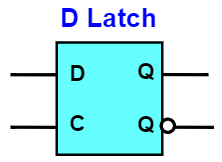

1.4 D latch with control input (with NAND gates)

D = 1是SET状态;D = 0是RESET状态。

2. Flip-Flop (触发器)

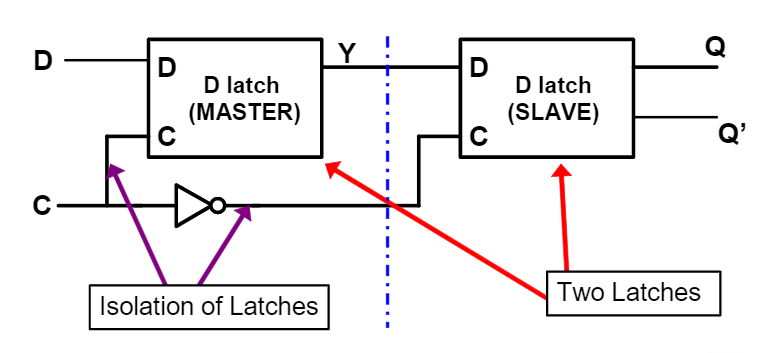

2.1 D Type Master-Slave Flip-Flop

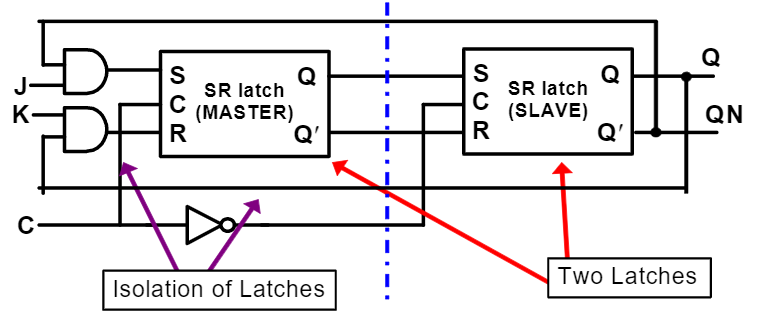

2.2 JK Type Master-Slave Flip-Flop

J相当于SET,K相当于RESET。但是与SR锁存器不同的地方在于,当J = 1,K = 1同时发生时,输出的结果是last结果的反转(complement)。

主从JK触发器的问题:请看这篇文章的第三部分,来解决0’s catching和1’s catching的问题。

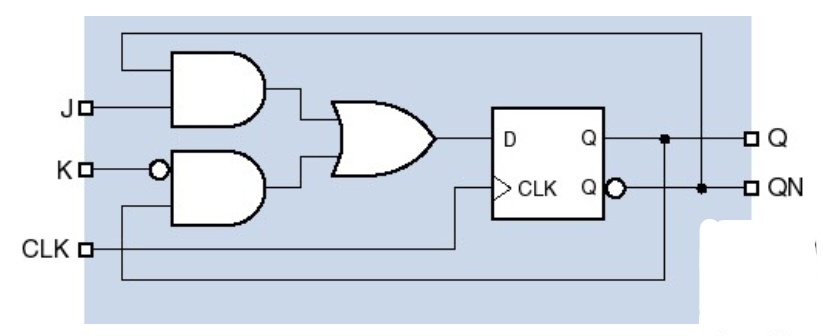

2.3 Edge-Triggered JK Flip-Flop

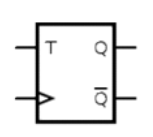

2.4 Toggle Flip-Flop

当T = 1时,在时钟信号有效的时候,输出结果会是last状态的翻转(toggle);当T = 0时,输出结果不会翻转,保持上一个状态。

2.5 为什么会有Master-slave和Edge-triggered之分呢?

推荐阅读:电平触发、脉冲触发、边沿触发的区别

边沿触发,意味着整个触发器元件,只有当时钟信号下降(或者上升)的那一时刻,整个元件才会读到输入信号,并做出相应的反应。

主从,它的输出也是在时钟信号下降(或者上升)的那一时刻才会发生改变,可是我们为什么不称之为边沿触发呢?我的理解是,当时钟信号为有效时,输入信号能够进入到触发器中。输入信号的改变,会使主锁存器的状态发生一定的改变,所以不能称之为edge triggered。

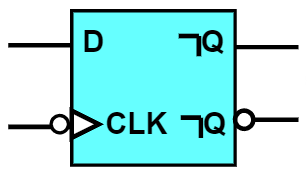

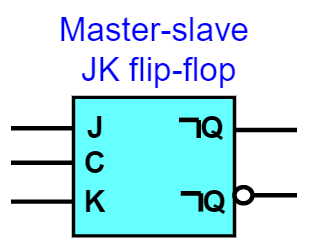

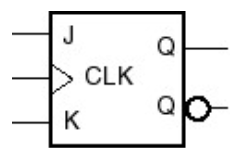

3. 总结触发器的符号表示

- 只有脉冲触发(主从JK触发器、主从D触发器),在Q和QN左边是有小直角的。

- CLK的小三角,是边沿触发独有的。

- 当负电平有效(对于电平触发来说),或者下降沿有效(对于边沿触发来说)的时候,CLK左边会有的小圆圈(inverter)。

4. Setup time & Holding time

相信这个文章已经说得够清楚了。:建立时间setup time/保持时间 hold time

最后

以上就是淡然豆芽最近收集整理的关于【数字电路】时序电路中一些元件的总结的全部内容,更多相关【数字电路】时序电路中一些元件内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复