本文实现的同步置数、同步清零的计数器,同样是基于王先生的书籍上的源代码实现。

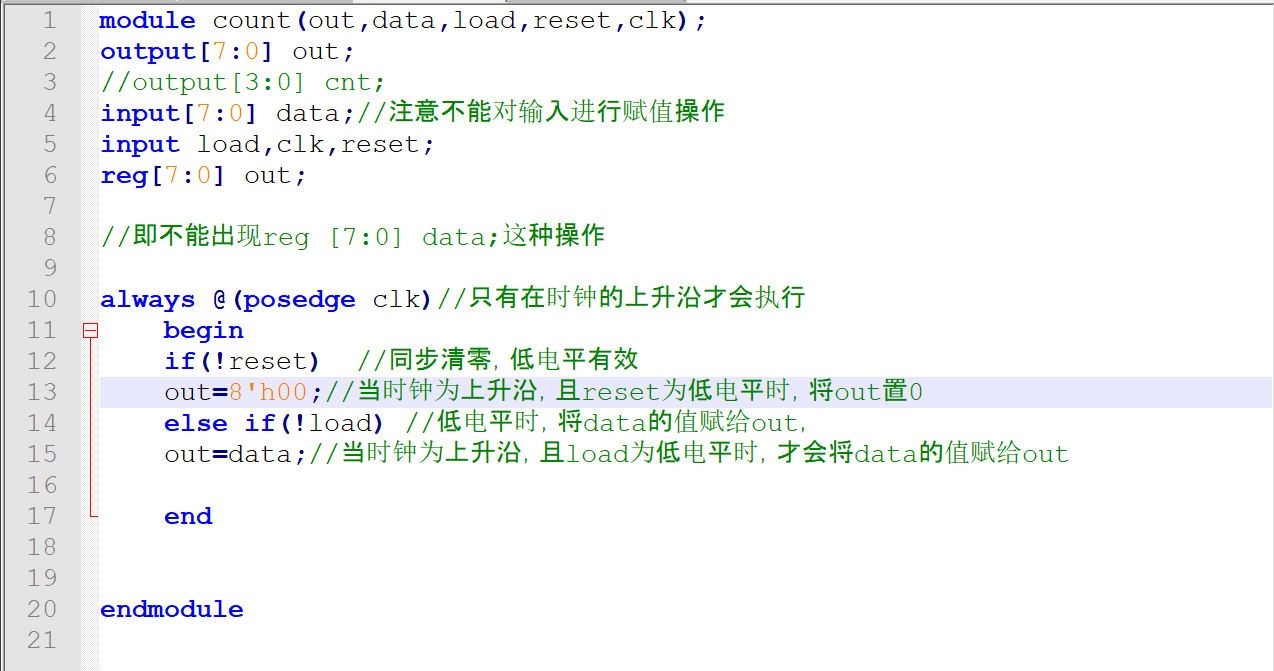

下面是计数器的源代码(暂时以图片的形式发出来) :

:

这个源代码被我修改了一部分,省去了原来的else语句,直接在load低电平时对输出out赋值,可以得到相同的结果,简化了程序。接下来时测试程序(同样以图片的形式上传):

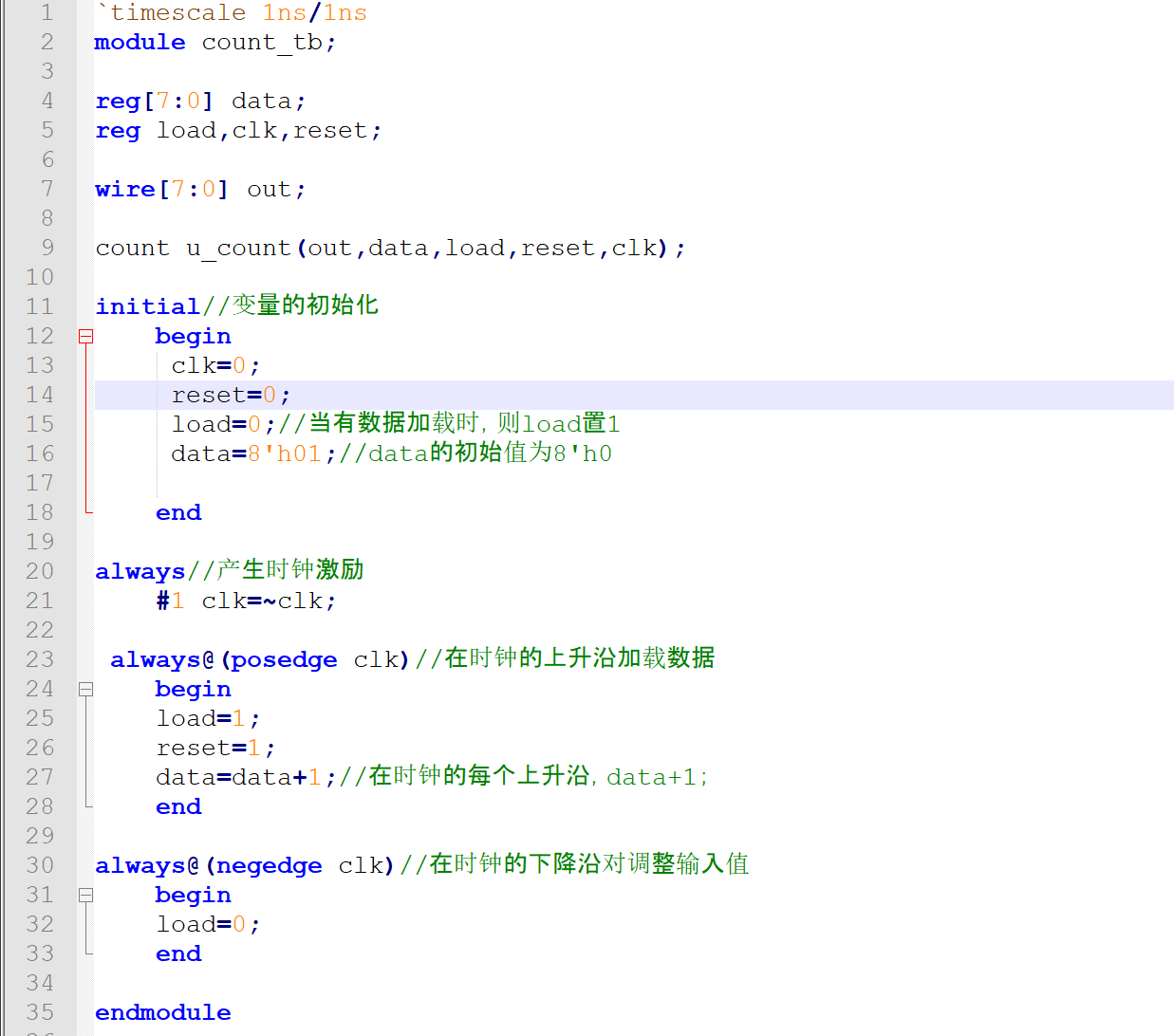

这是书籍中没有的测试文件,为了学习verilog,必须学会验证文件的编写,其实也就是激励源的产生。然后是最终得到的时序波形图:

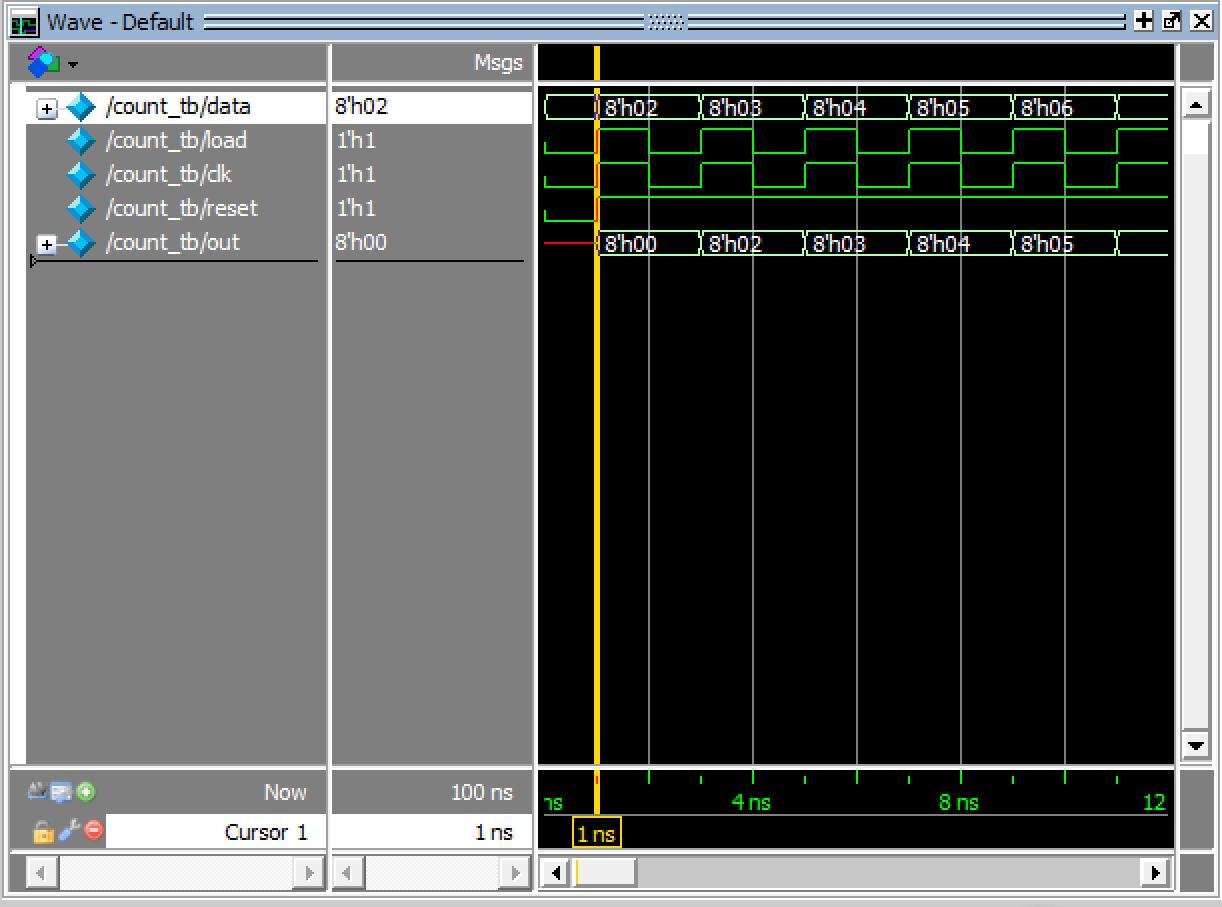

在验证文件中,我特意将data的初始值赋为8'h01,就是为了看出reset是在哪个时间进行复位的,同时,计数器的输入值也是一个变量, 在reset无效时,此时,data的值在下一个时钟的上升沿已经是8'h02了(注意,在时钟的上升沿虽然data的值也会发生改变,但是,赋给输出的依然是改变之前的那个值),所以在3ns时,输出的值仍然时8'h02.

最后

以上就是贪玩蚂蚁最近收集整理的关于同步置数、同步清零的计数器的全部内容,更多相关同步置数、同步清零内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复