// 将50MHZ四分频产生12.5MHZ时钟

1.Design-div_clk

创建Design文件夹

module div_clk(

input wire sclk,

input wire rst_n,

output wire po_div_clk

);

parameter DIV_END = 8'd3;

reg [7:0] div_cnt;

reg div_clk_o;

//div_cnt

always @ (posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

div_cnt <= 'd0;

else if(div_cnt == DIV_END)

div_cnt <= 'd0;

else

div_cnt <= div_cnt + 1'b1;

always @ (posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

div_clk_o <= 1'b0;

else if(div_cnt == 'd1)

div_clk_o <= 1'b1;

else if(div_cnt == 'd3)

div_clk_o <= 1'b0;

assign po_div_clk = div_clk_o;

endmodule2.TB-tb_div_clk

创建Sim文件夹

`timescale 1ns/1ns

module tb_div_clk;

reg sclk,rst_n;

wire po_div_clk;

initial begin

sclk = 0;

rst_n = 0;

#100

rst_n <= 1;

end

always # 10 sclk = ~sclk;

div_clk div_clk_inst(

.sclk (sclk),

.rst_n (rst_n),

.po_div_clk (po_div_clk)

);

endmodule

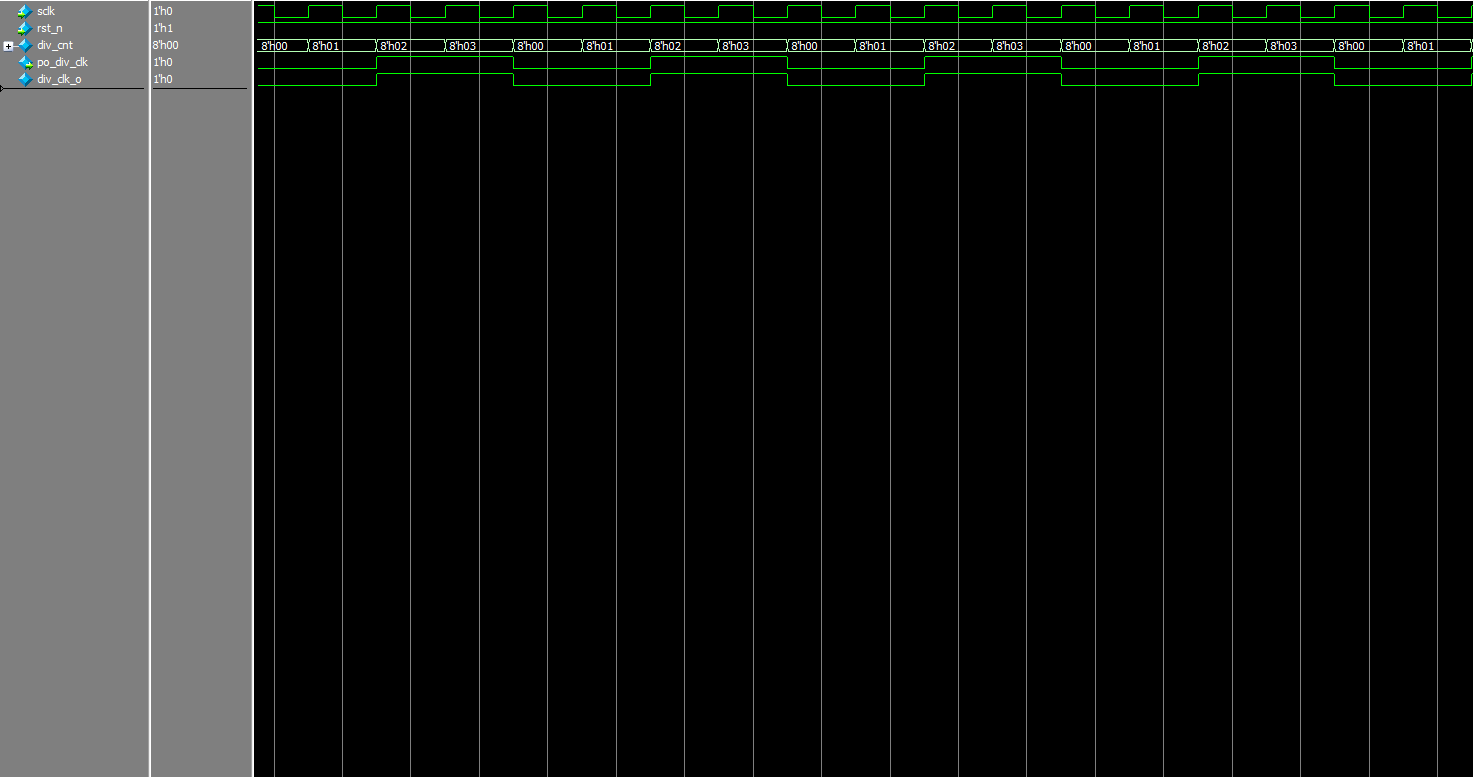

3.利用ModelSim产生仿真(前仿真)

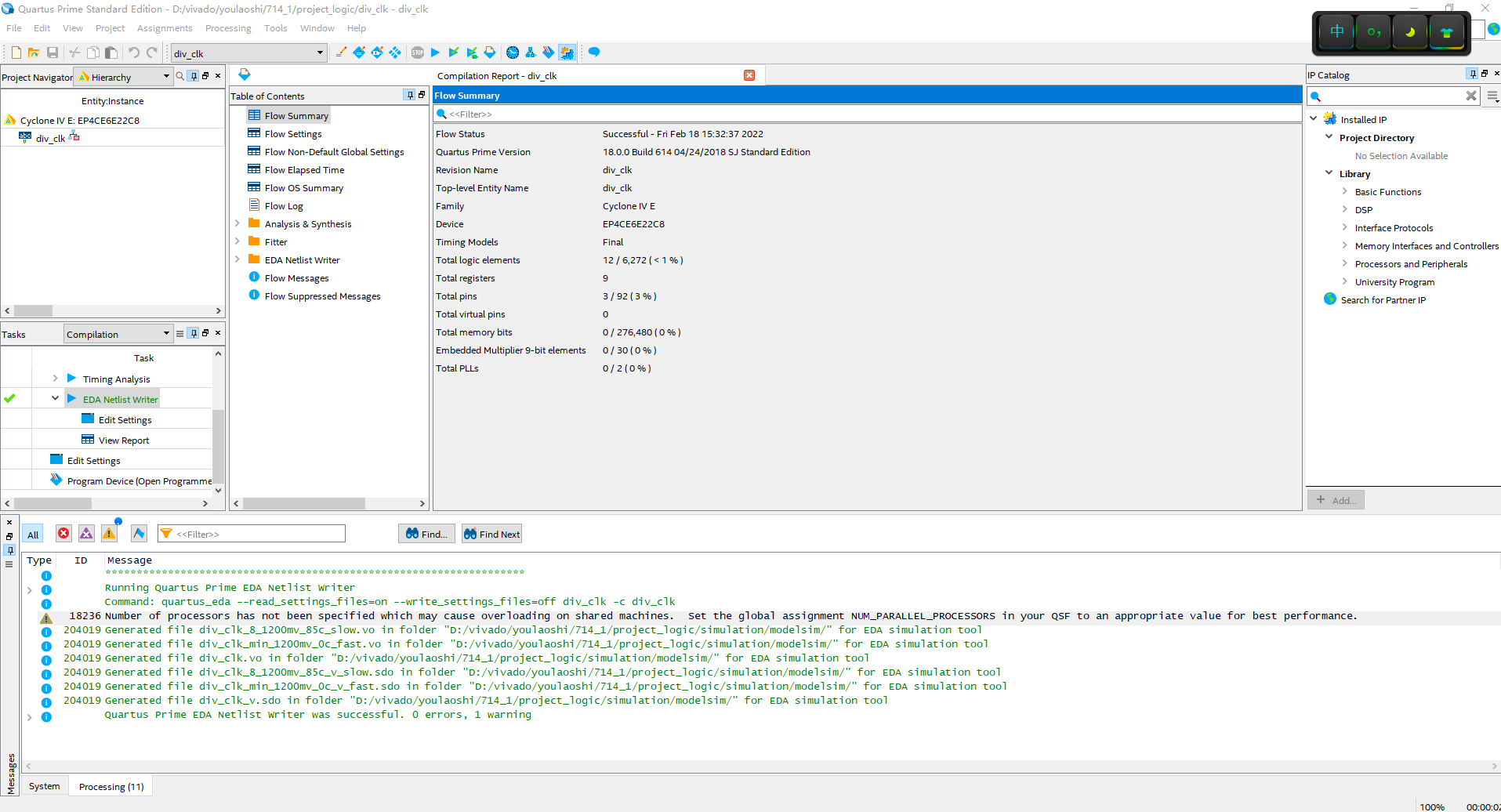

4. Quartus 生成网表

4.1 .在当前目录下生成Project项目——添加div_clk.v文件(后面器件可以自己选择)

4.2 更改目录

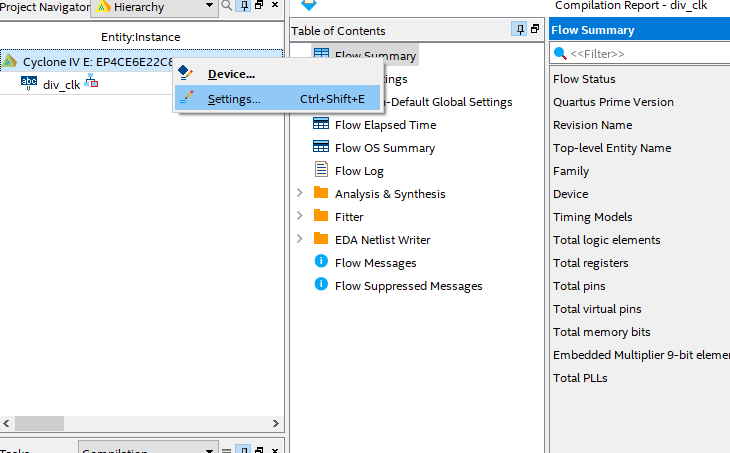

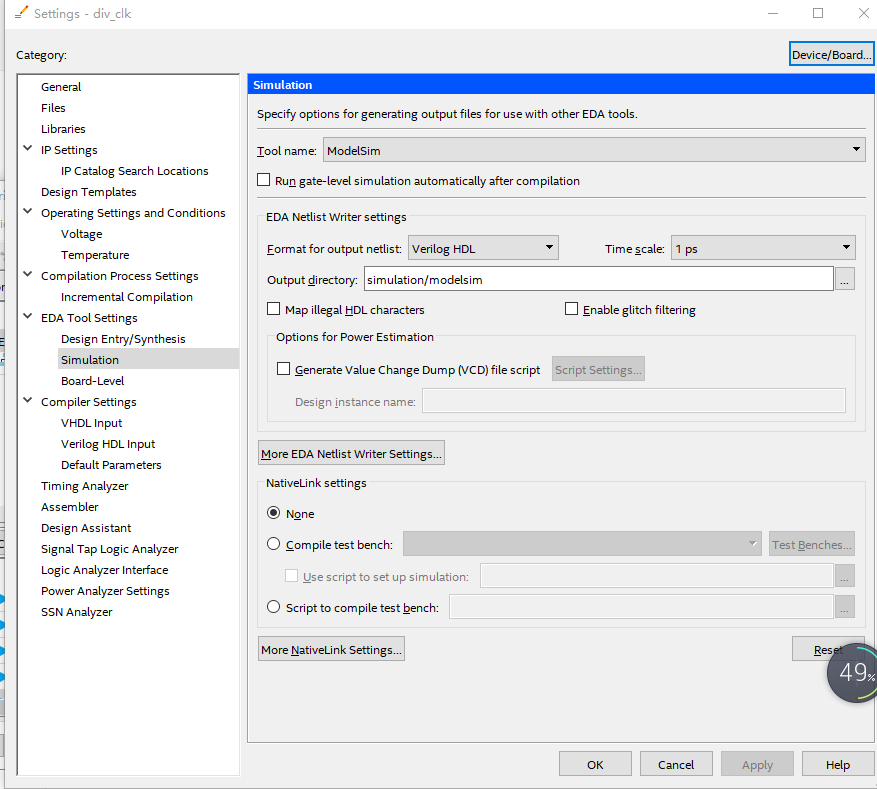

右键Cyclone IV 点击Settings——EDA Tools Setting——Simulation

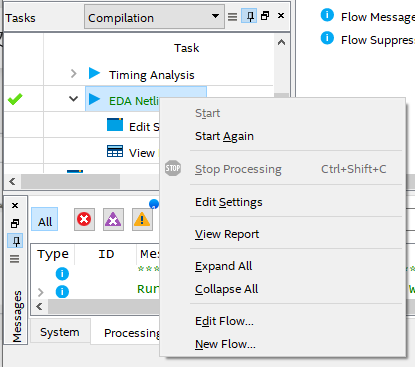

4.2 EDA Netlist Writer 生成网表

右键EDA Netlist Writer 点击start

5. 在ModelSim 建立后仿真

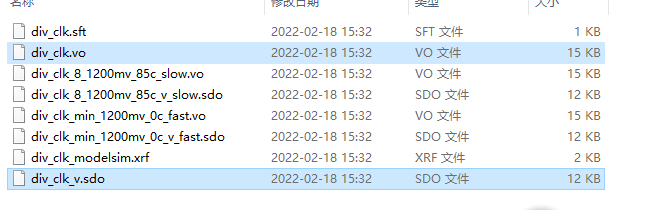

5.1 生成网表后打开当前目录——Simulation——modelsim复制div_clk.vo与div_clk_v.sdo文件复制到sim文件中

// altera_lib文件夹为后续生成添加库文件

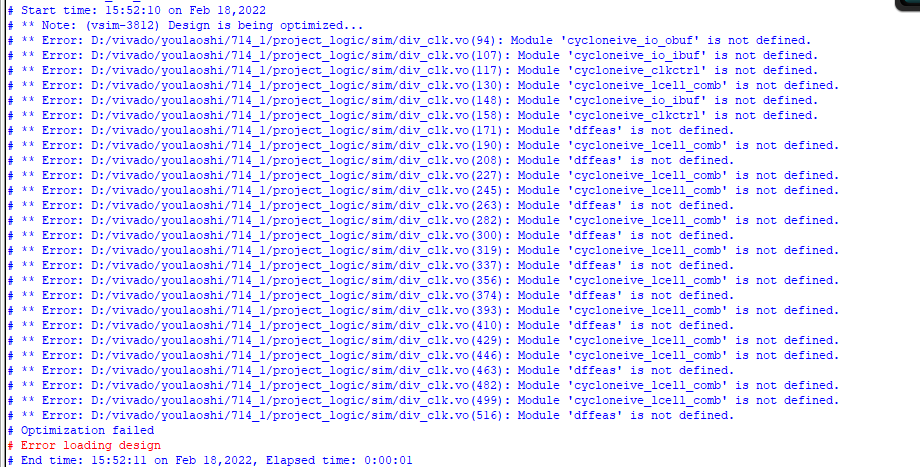

5.2 将ModelSim——Project中的div_clk 删除,添加div_clk.vo文件 进行编译 会发现报错 是因为库文件未添加

// 添加文件方法 在Project空白处右键Add to project——Existing file

5.3 在Sim文件中创建altera_lib文件夹 从Quartus目录下添加 altera_mf.v,altera_primitives.v,cycloneive_atoms.v三个文件

// 在Quartus安装目录中寻找

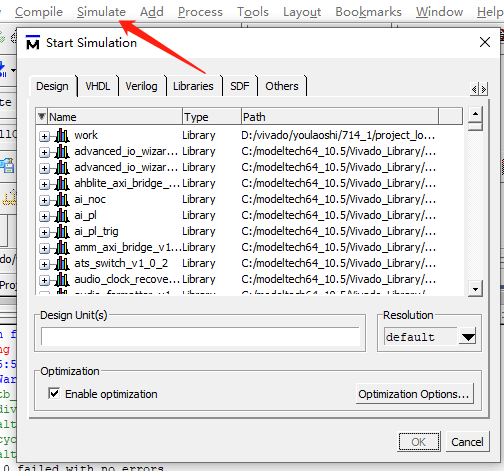

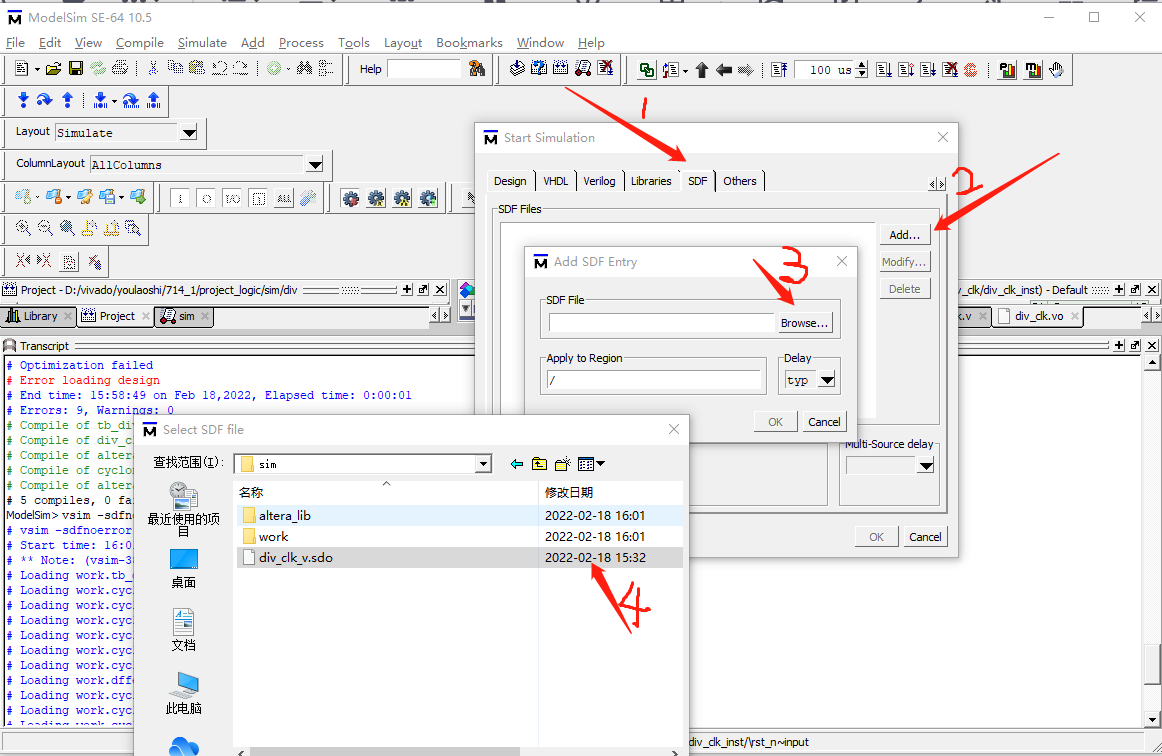

5.4 点击Simulate——Start Simulation ——SDF——添加div_cnt_v.sdo

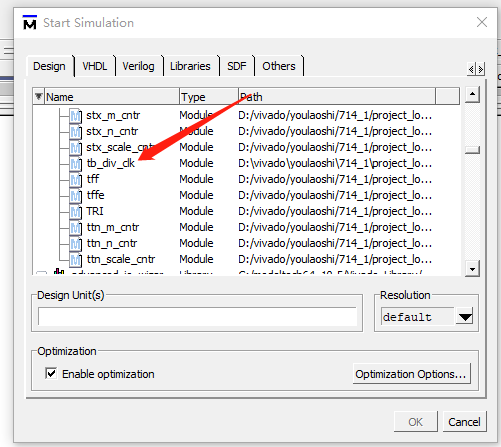

5.5 添加完后 点击Design 找到tb_div_clk点击确认

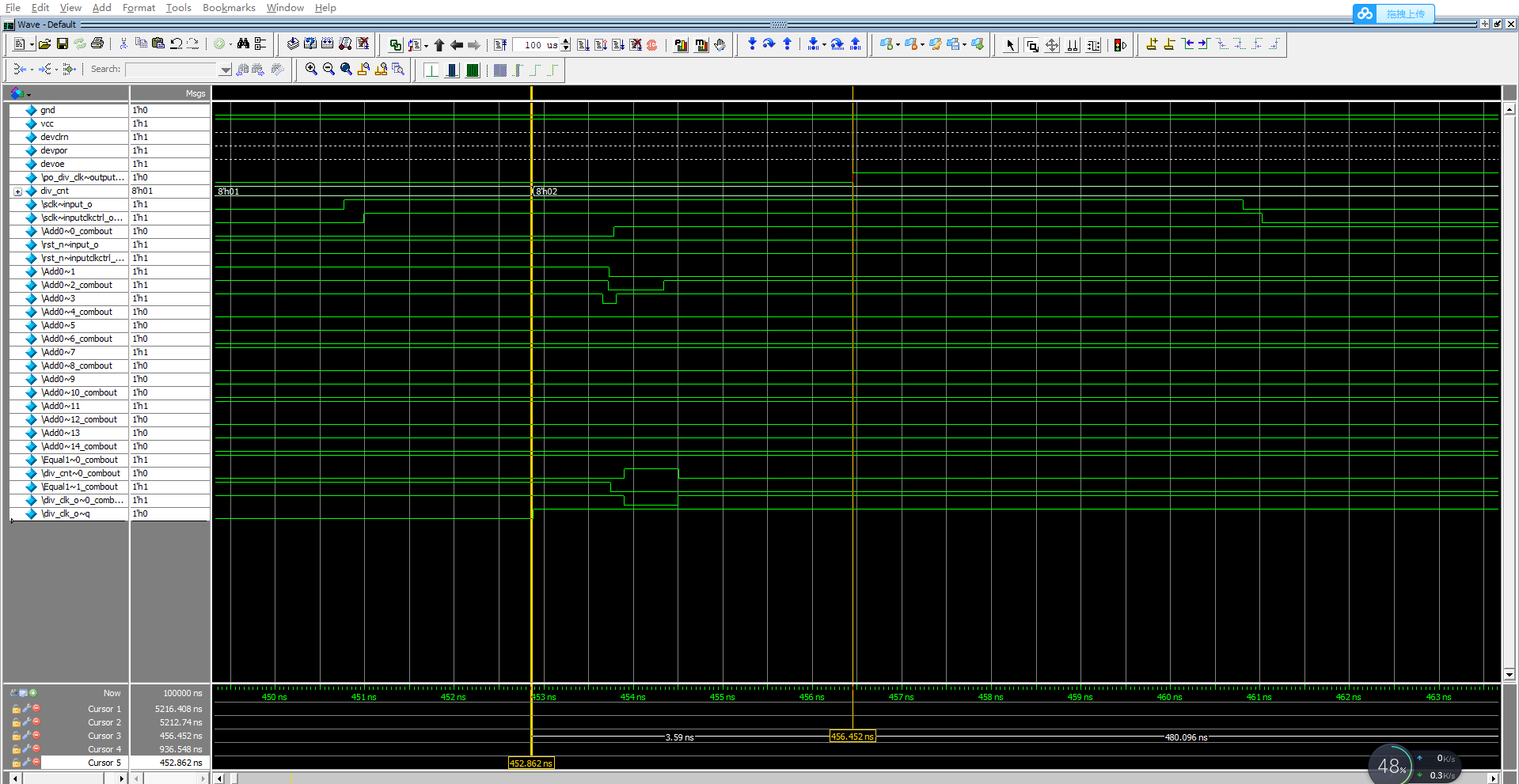

5.6 生成的后仿真

// 产生原因为 器件本身的延迟导致的

最后

以上就是隐形手套最近收集整理的关于FPGA学习_四分频(包含前仿真与后仿真)1.Design-div_clk2.TB-tb_div_clk3.利用ModelSim产生仿真(前仿真)4. Quartus 生成网表5. 在ModelSim 建立后仿真的全部内容,更多相关FPGA学习_四分频(包含前仿真与后仿真)1.Design-div_clk2.TB-tb_div_clk3.利用ModelSim产生仿真(前仿真)4.内容请搜索靠谱客的其他文章。

发表评论 取消回复