分频器介绍

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。

4分频代码

如时钟频率为50MHz,而实际需要(50/6 MHz)的频率,因此就需要4分频电路处理。4分频电路代码设计如下:

`timescale 1ns/1ns

module tb;

reg clk, rst;

wire clk_out;

div_4 dut(.clk(clk),

.rstn(rst),

.clk_out(clk_out)

);

initial begin

clk <= 0;

forever begin

#5 clk <= ~clk;

end

end

initial begin

#10 rst <= 0;

repeat(2) @(posedge clk);

rst <= 1;

end

initial begin

#500 $finish;

end

endmodule

module div_4(clk, rstn, clk_out);

input clk, rstn;

output clk_out;

reg clk_out;

reg [1:0] cnt;

always @(posedge clk or negedge rstn)

begin

if (!rstn) begin // cnt_reset

cnt <= 1'b0;

end

else if (cnt == 2'b11) begin

cnt <= 1'b0;

end

else begin

cnt <= cnt + 1'b1;

end

end

always @(posedge clk or negedge rstn)

begin

if (!rstn) begin

clk_out <= 1'b0;

end

else if(cnt == 1'b1) begin

clk_out <= !clk_out;

end

else if (cnt == 2'b11) begin

clk_out <= !clk_out;

end

else begin

clk_out <= clk_out;

end

end

endmodule

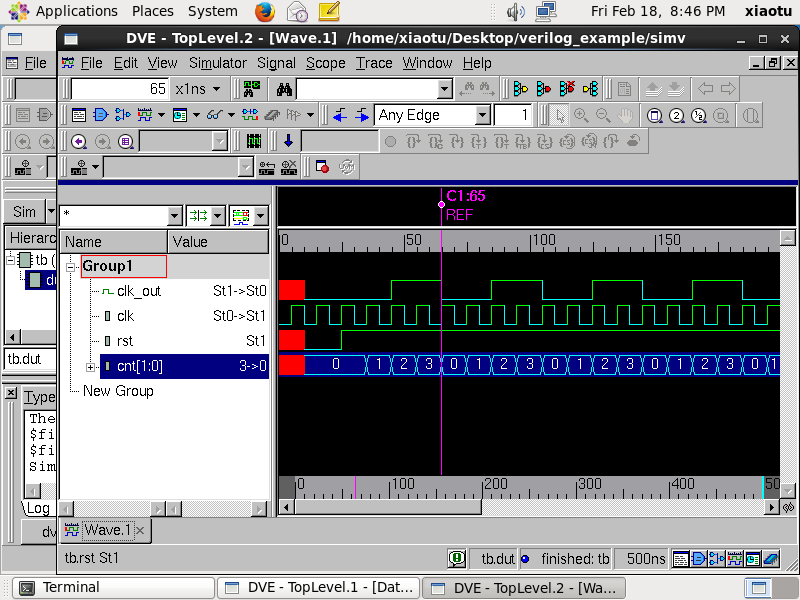

仿真结果

最后

以上就是耍酷帆布鞋最近收集整理的关于【4分频电路 -verilog】的全部内容,更多相关【4分频电路内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复