组合逻辑电路:

输出仅取决于当时的输入。

时序逻辑电路:

输出不但取决于当时的输入,而且还取决于上一时刻的电路状态

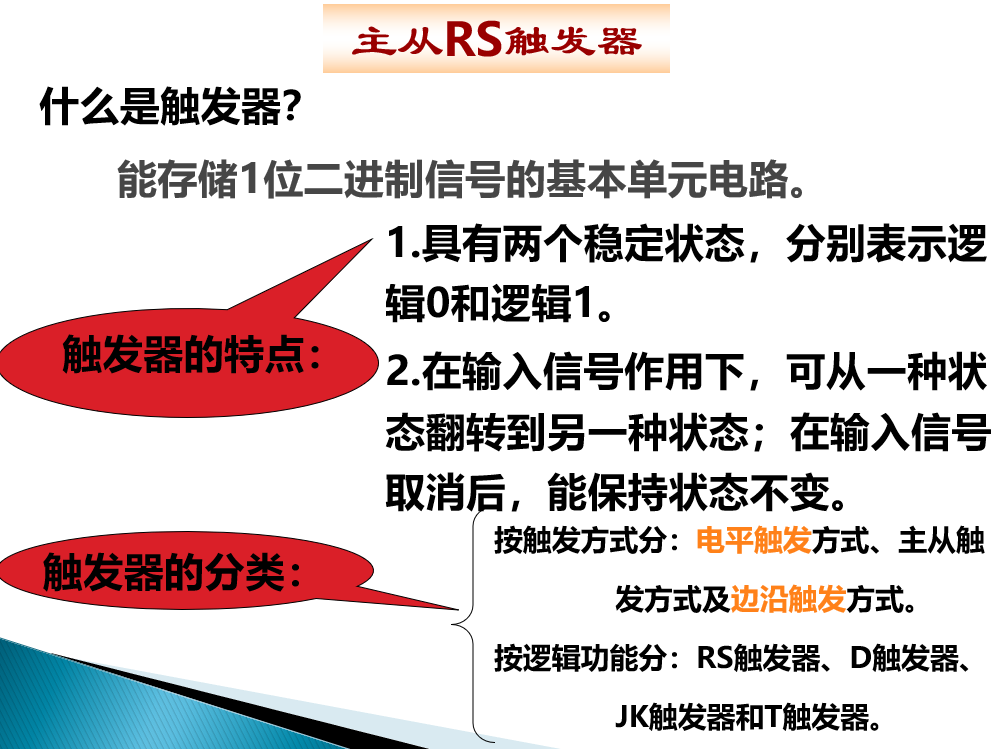

基本锁存器、触发器

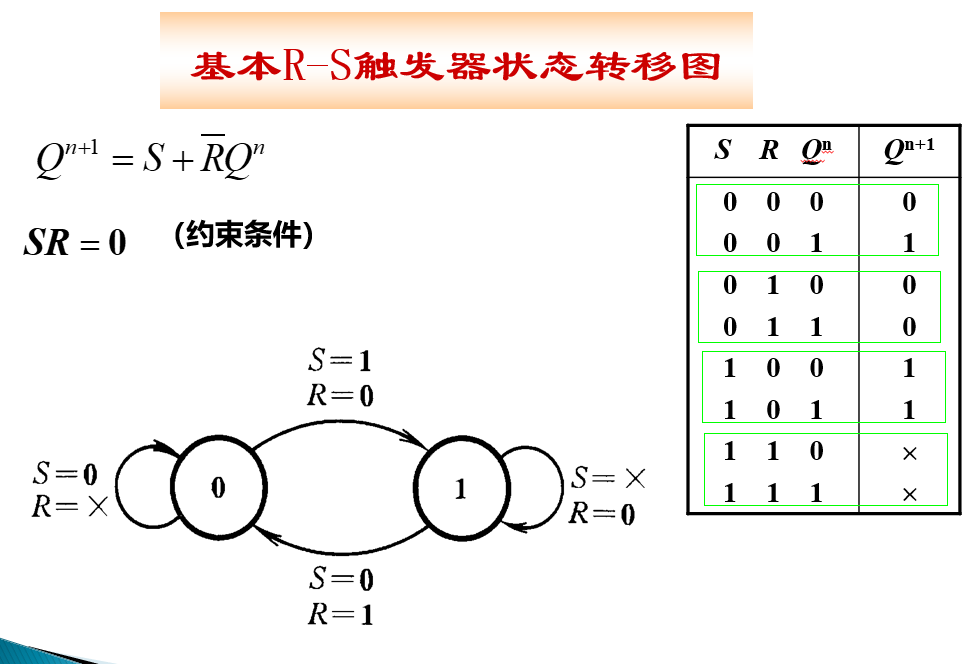

什么是锁存器?

能够存储1位二进制的基本单元电路。

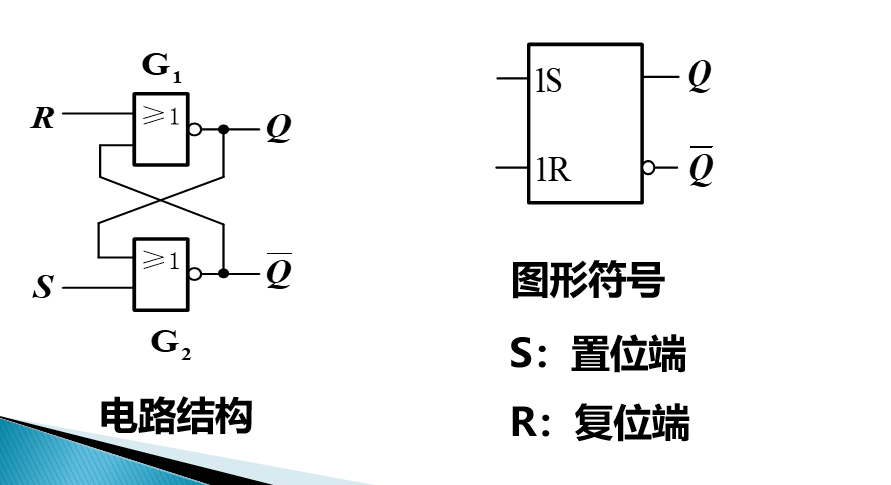

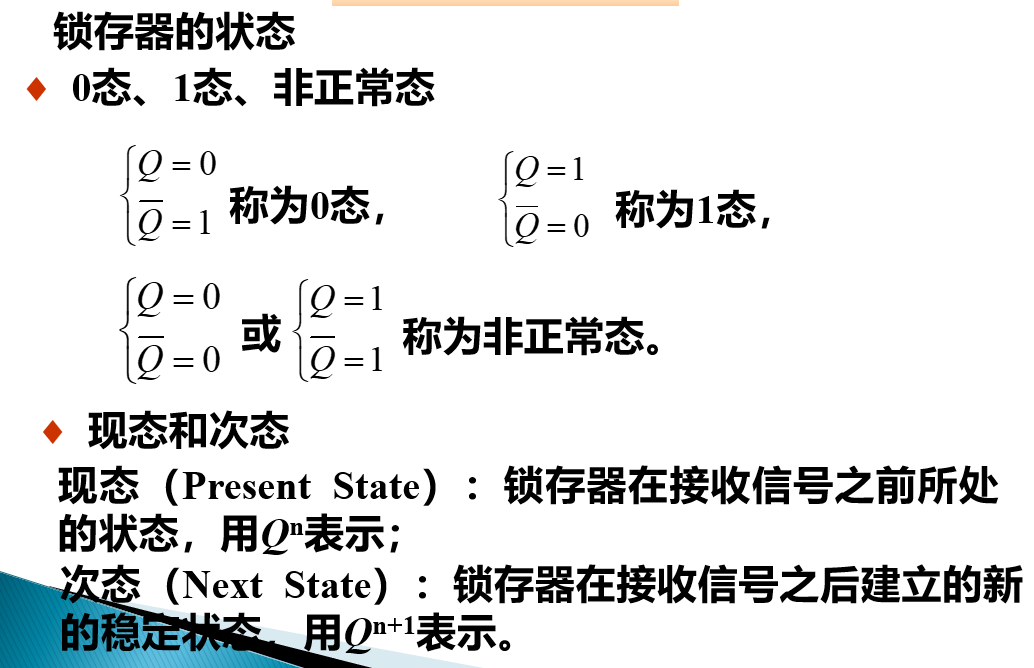

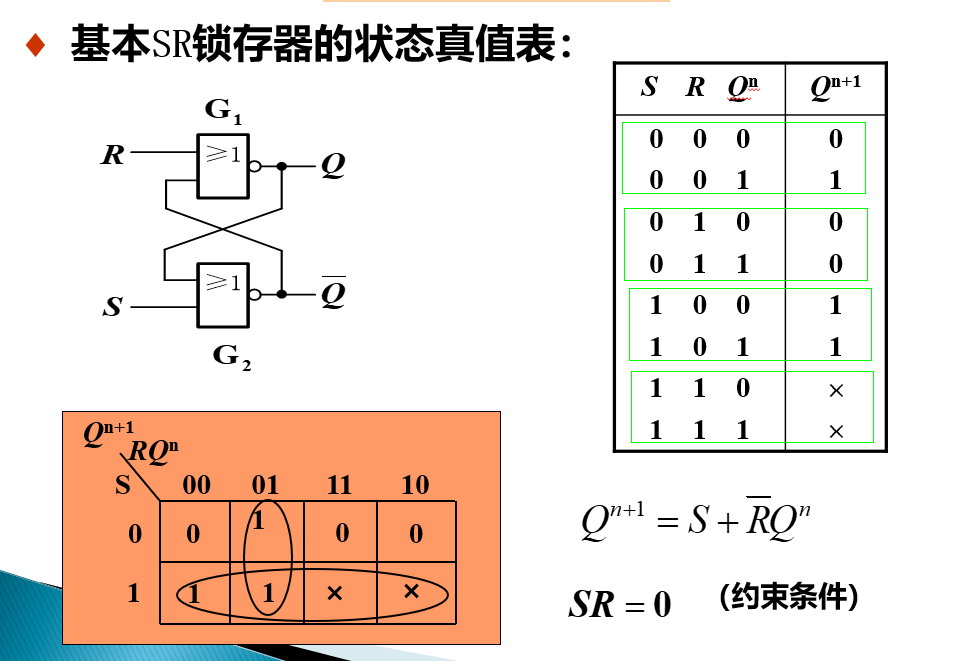

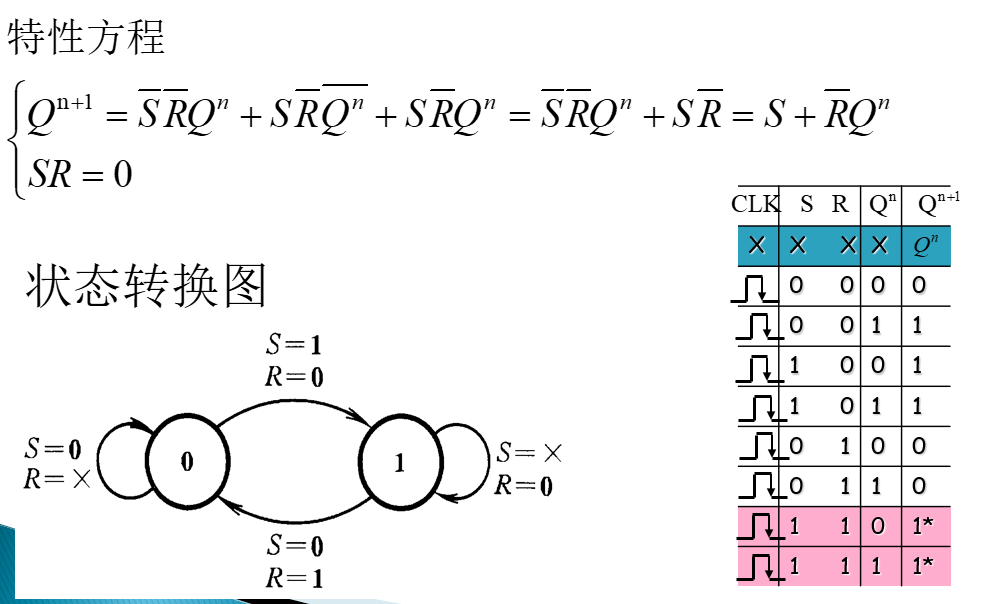

基本RS锁存器

1.或非门组成的基本RS锁存器

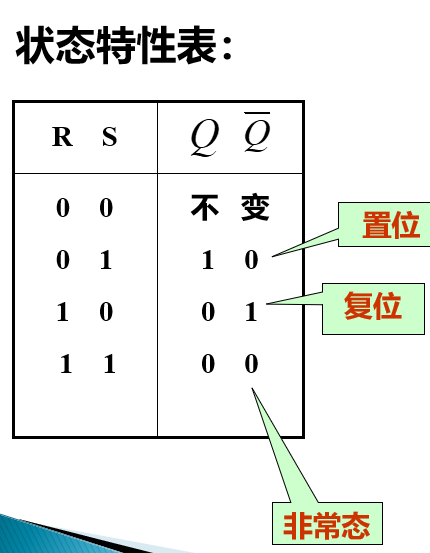

置位的意思就是:Q=1,输出状态为高电平;

复位的意思就是:Q=0,输出状态为低电平;

在一般的运算里,锁存器的输出总是互为相反的。

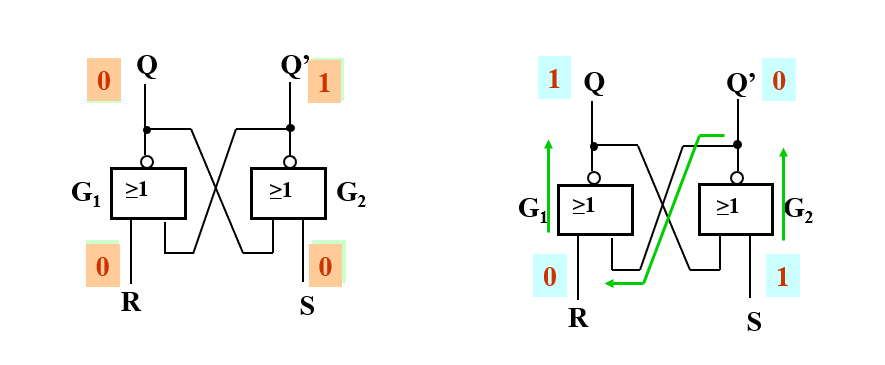

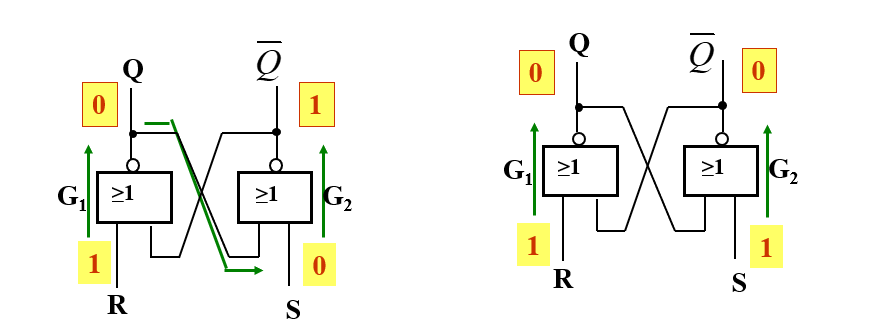

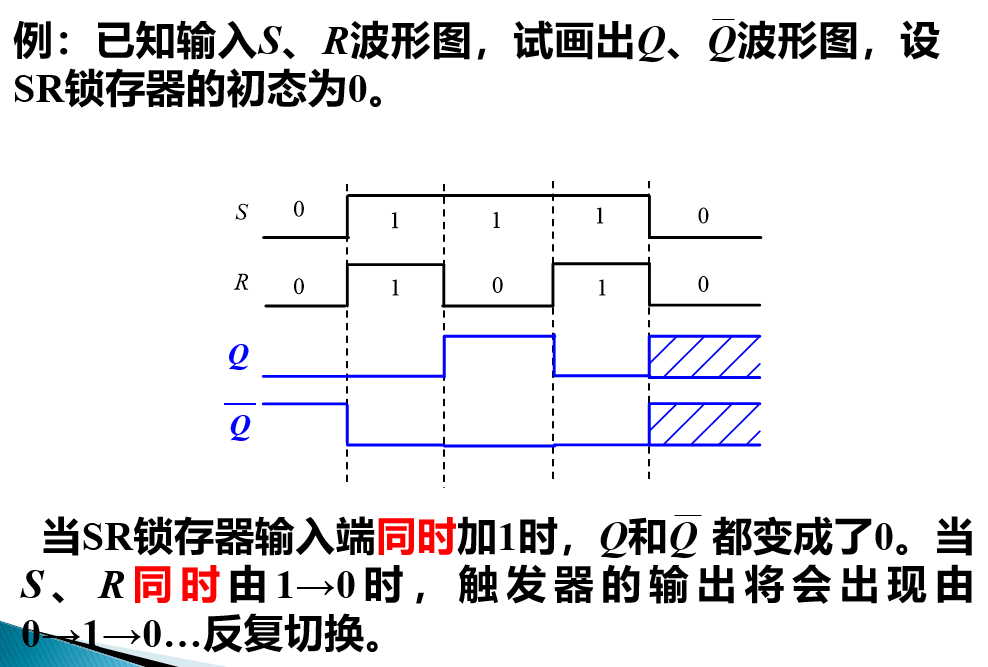

工作原理:

1.当R=S=0时,输出不变;

2.当S=1,R=0时,输出为1;

3.当R=1,S=0时,输出为0;

4.当R与S均为1,两个输出均为0

正常工作输入信号约束:SR=0.

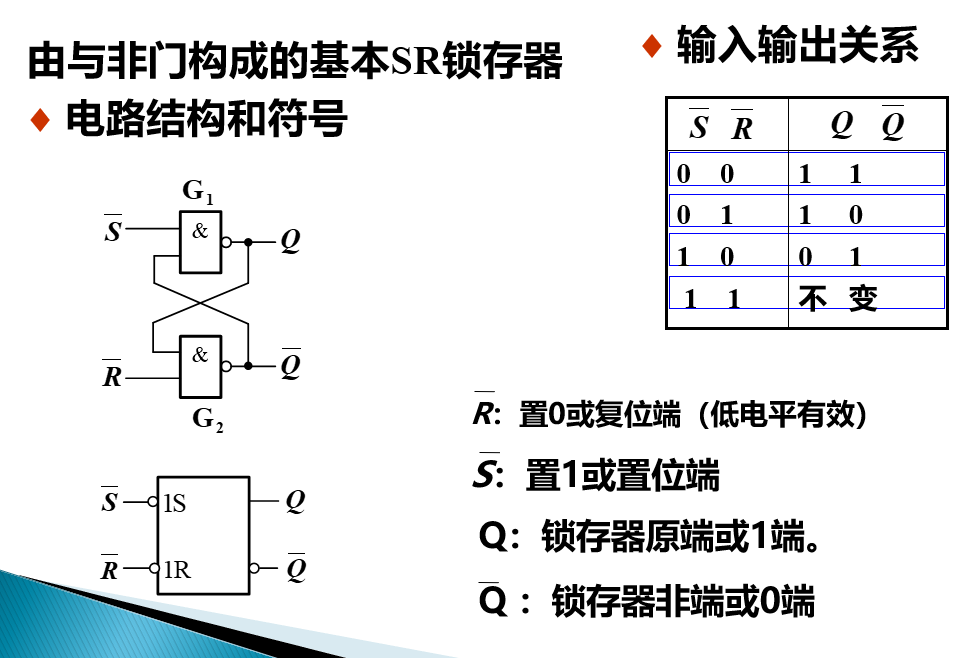

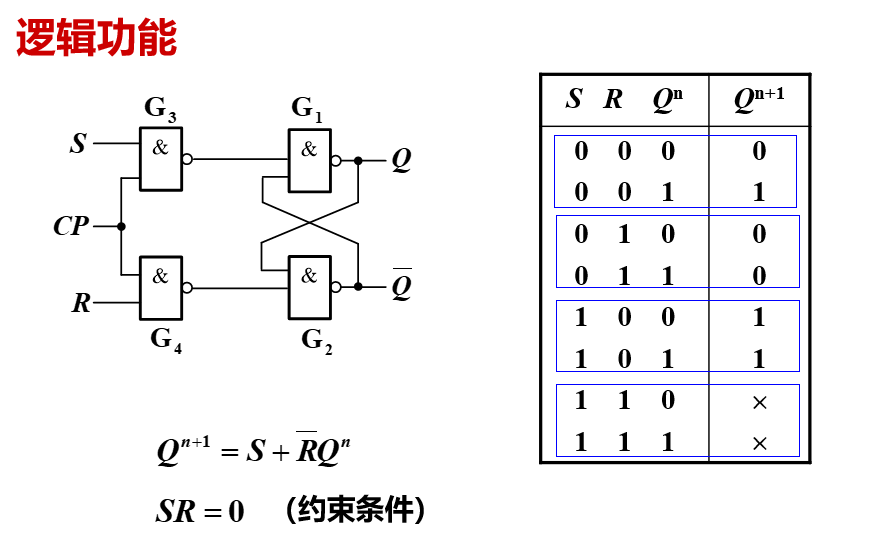

2.由与非门构成的基本RS锁存器

2.由与非门构成的基本RS锁存器

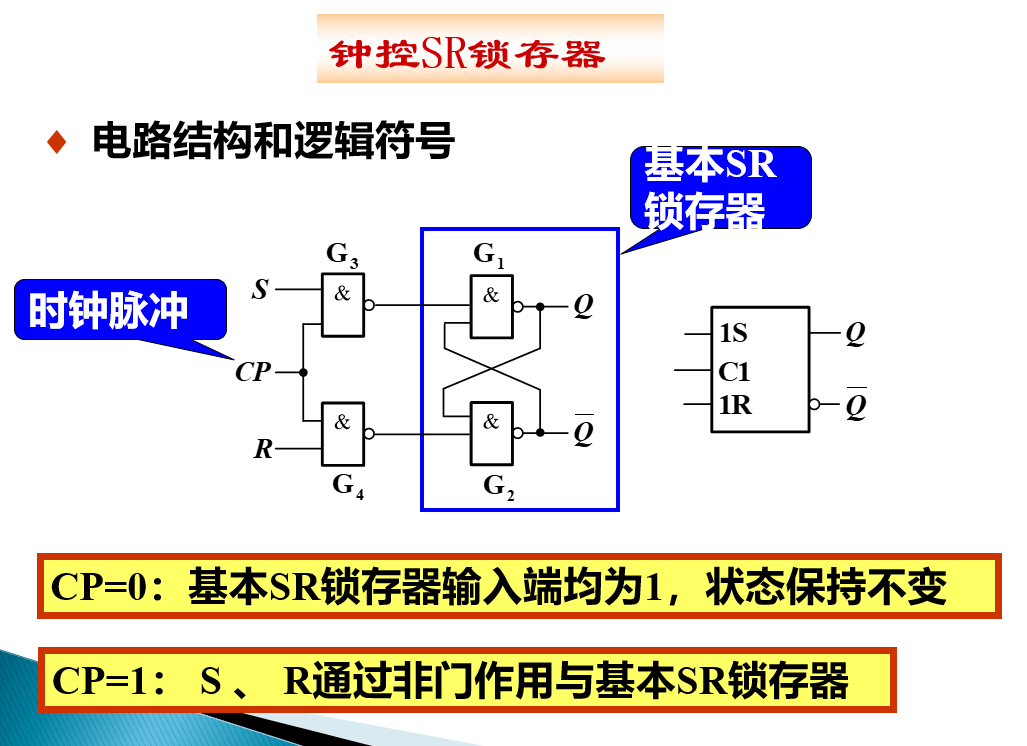

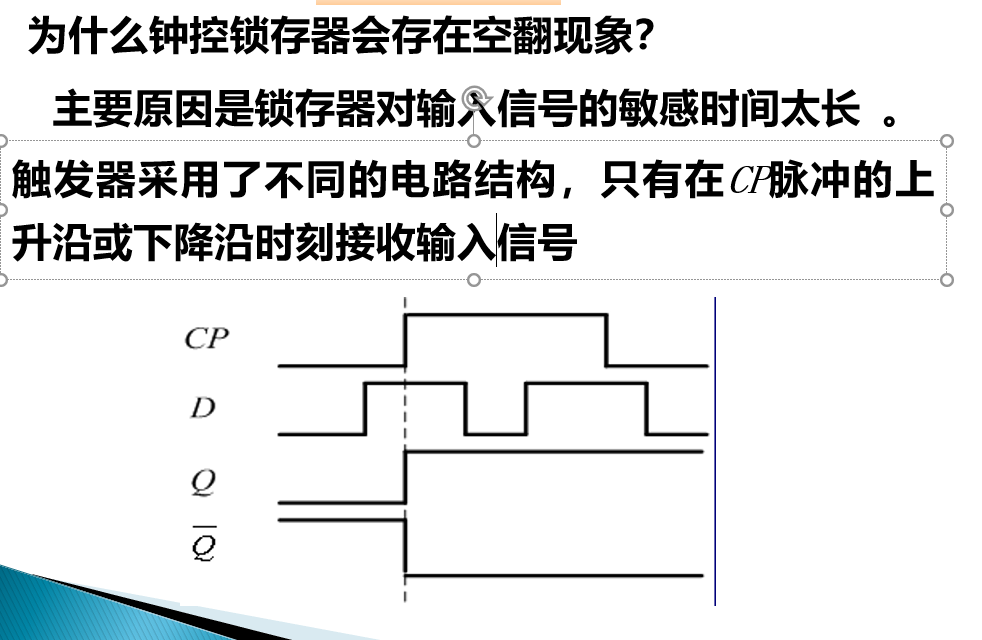

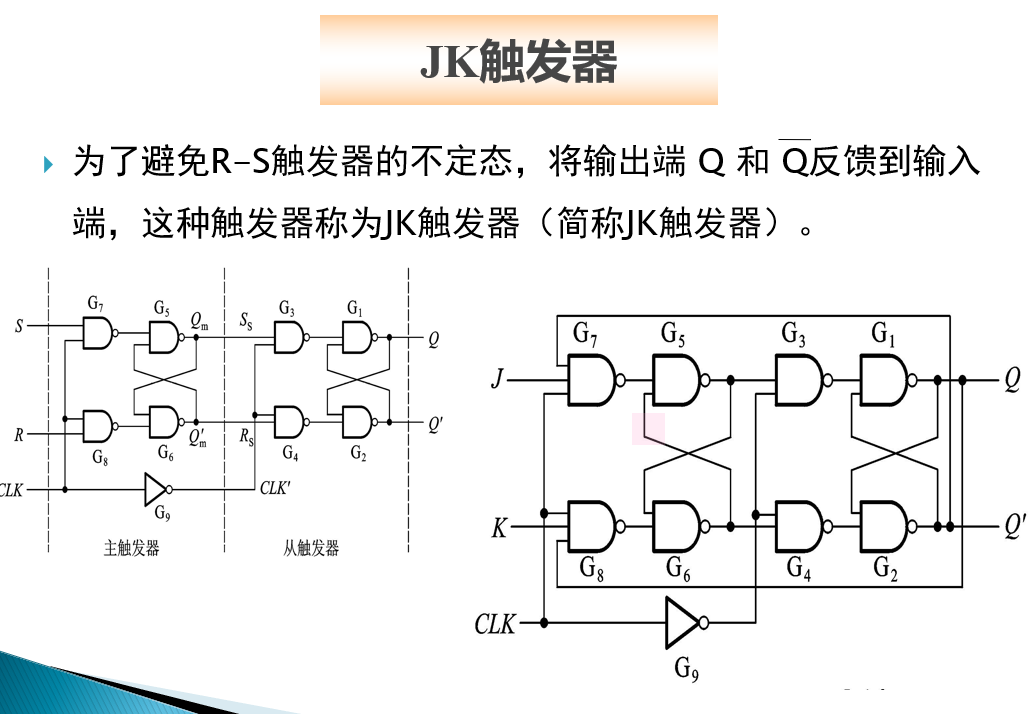

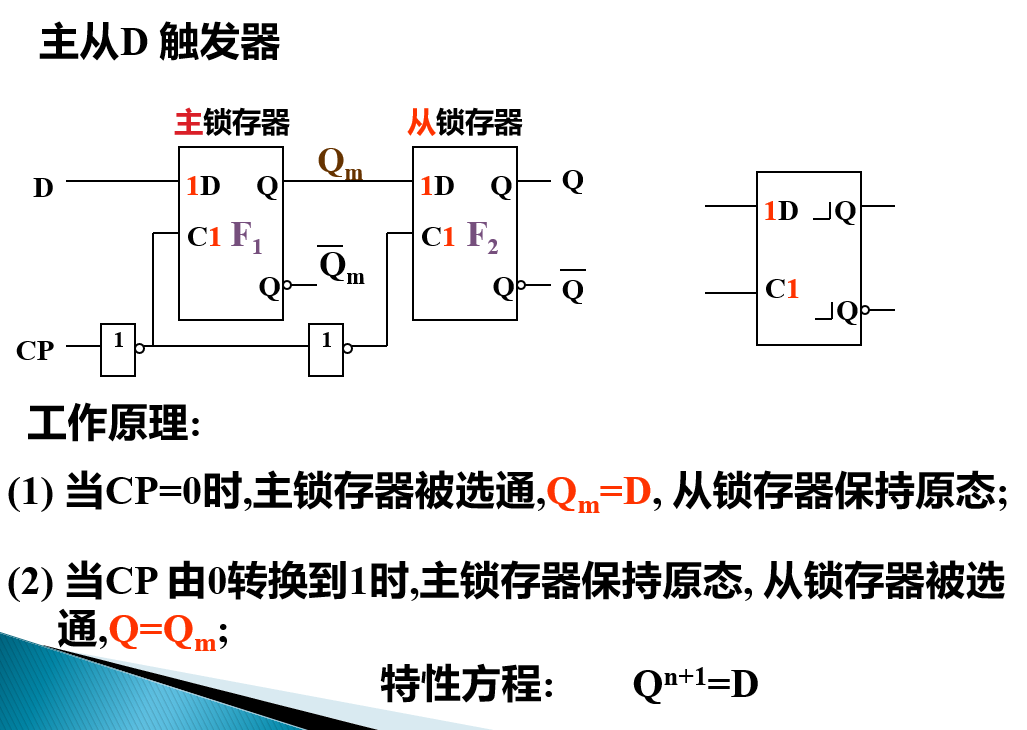

图上是下降沿接受信号触发的。

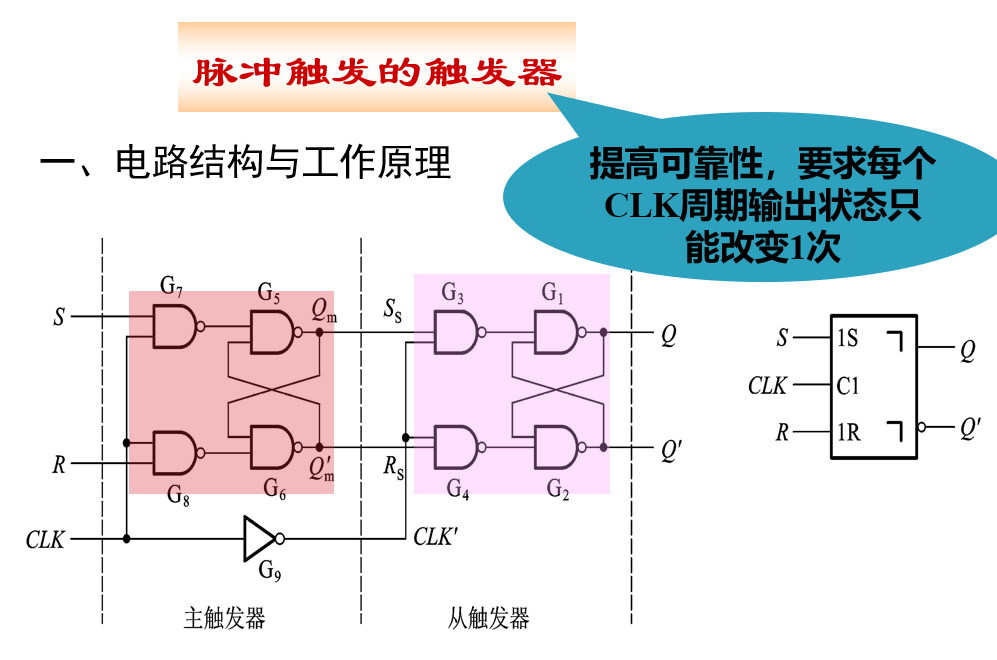

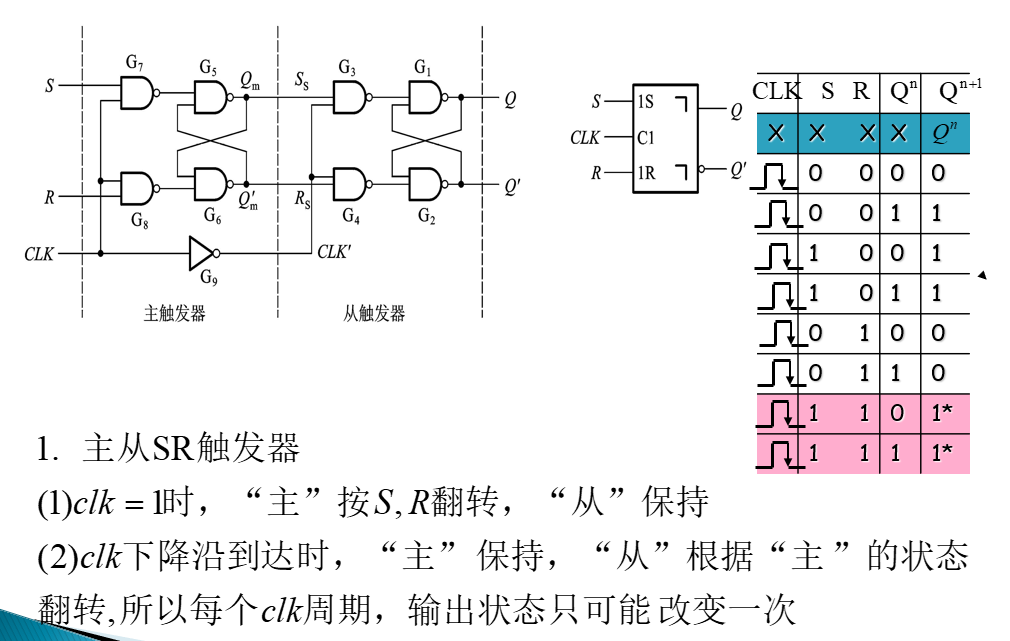

很容易理解,当CLK为1时,主触发器是正常运行的,而从触发器是不运行的。

当CLK=0时,主触发器是无法接受新的输入信号的,但是原本的输出状态是存在的,此时从触发器正常进行,那么之前 主触发器 的输出就可以作为 从触发器 的输入。

并且如果CLK一直不变的话,那么最终的输出是不会改变的,

为什么在下降沿,这个是由于从触发器接受的其实是上一个状态的主触发器的输出。

若是上升沿,即CLK从0变为1,在CLK为0时正常 从触发器 接受 主触发器 的输出,当CLK变为1时,主触发器的输出可能改变了,但是 从触发器 的输出跟输入已经没有关系了,那么输出依然不会改变

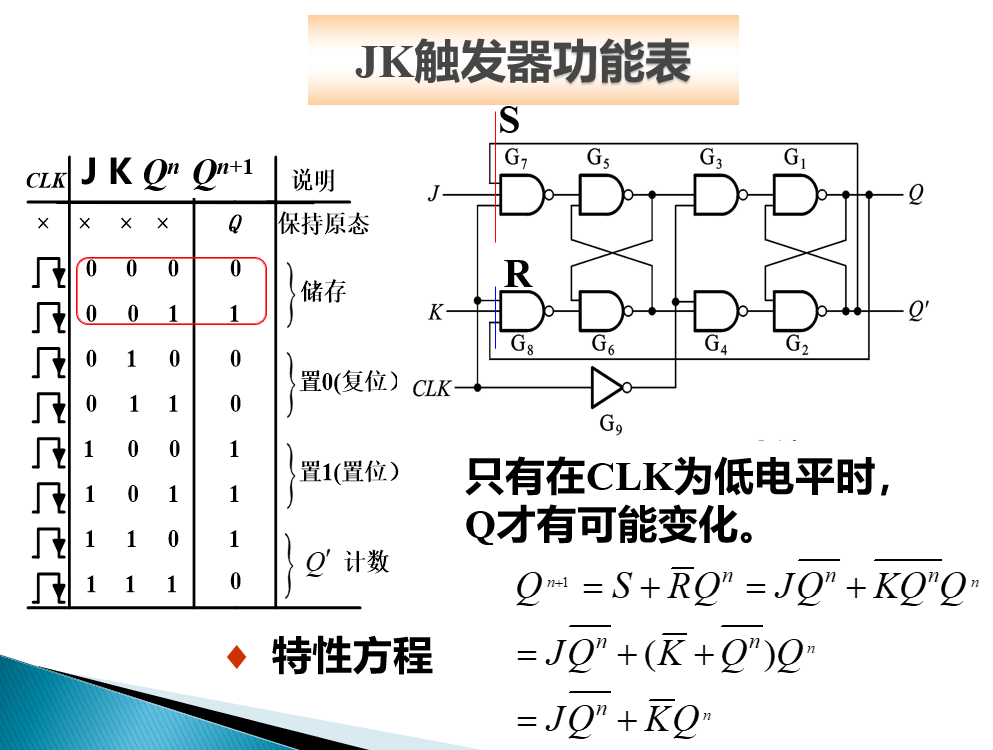

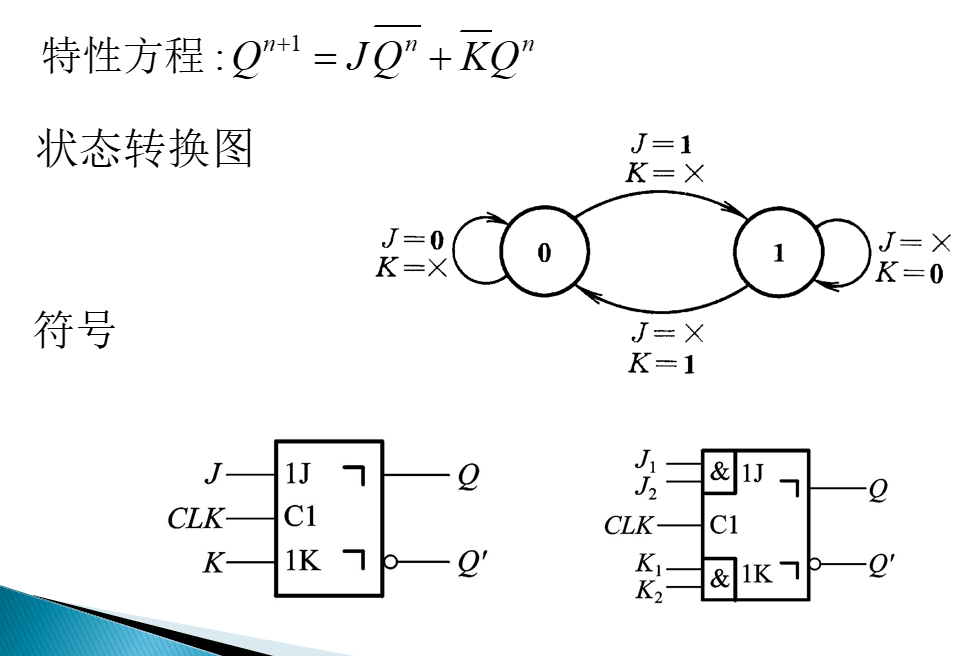

当J与K输出都为1时,输出的状态变为相反状态。(从而避免了不稳定状态的产生)

最后

以上就是淡然冬日最近收集整理的关于锁存器与触发器什么是锁存器?的全部内容,更多相关锁存器与触发器什么是锁存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复