使用Verilog语言描述触发器和锁存器;触发器和锁存器的区别。

修正/添加:

修改时间:2020/08/18

添加内容:锁存器危害

什么是触发器和锁存器?

触发器:一种具有触发功能的存储单元。

锁存器:一种由电平控制的存储单元。

无论是触发器还是锁存器都具有存储功能,关键是在时钟的变化下和输入信号的作用下,输出信号会有什么表现?

锁存器的Verilog描述。

锁存器在有效电平时间内输出信号可以随着输入信号变化而变化,在其他时间内维持不变。

在时序电路中要避免锁存器的出现,因为锁存器的出现无法过滤输入信号的变化,这种变化会对之后电路产生难以估计的后果。

本次添加内容为 :输出信号被锁死,输入信号的变化不起作用;同时锁存器使静态时域分析非常复杂。。

不过,如果需要锁存器,设计代码如下:

注:latch表示锁存器

module latch (clk,d,q);

input clk;

input d;

output q;

assign q=clk?d:q;

endmodule

测试代码如下:

module latch_tb;

reg clk,d;

wire q;

integer seed;

latch t1 (clk,d,q);

initial

begin

clk=0;d=0;seed=1;

repeat(10)

begin #7 d=($random(seed)/2); end

#10 $stop;

#10 $finish;

end

always #5 clk=~clk;

endmodule

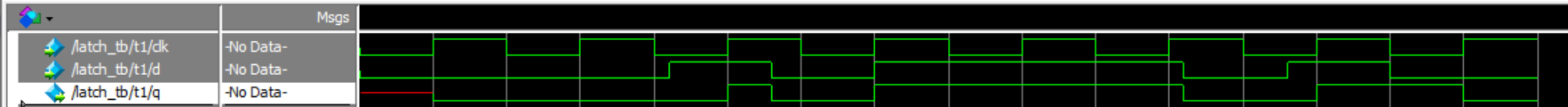

测试模块随机放置10个二进制随机数模拟输入。最终的仿真波形如下:

这里对“在有效电平时间内输出信号可以随着输入信号变化而变化,在其他时间内维持不变。”做简单的解释。很明显在时钟信号处于高电平时,输出信号会随着输入信号完整的变化,但是一旦时钟信号为低电平时,输出信号会保持前一时刻的状态,一直到下一个时钟为高电平的时刻,再根据输入信号而变化。这样反复下去。

触发器的Verilog描述。

触发器用ff表示,D触发器就是dff。

最常见、用途最广泛的触发器是D触发器。D触发器最简单的理解就是,在时钟满足“某种触发条件时”,输出的值就是输入的值,其他时间保持不变。

“某种触发条件”就是电平触发和边沿触发。

电平触发的D触发器的Verilog描述:

module dff0 (clk,d,q);

input clk,d;

output q;

reg q;

always @ (clk)

q<=d;

endmodule

边缘触发的D触发器的Verilog描述:

module dff1 (clk,d,q);

input clk,d;

output q;

reg q;

always @ (posedge clk)

q<=d;

endmodule

这两种D触发器的代码描述极其相似,区别只是以下两句:

语句1

always @ (clk)

q<=d;

语句2

always @ (posedge clk)

q<=d;

语句1和语句2都是常规事件控制的一种。常规事件控制的执行条件有三种,分别是:信号的值发生变化(语句1);发生正跳变(语句2);发生负跳变。正跳变标志是posedge,负跳变标志是negedge。

事件:某一个寄存器或者线网变量的值发生变化。

事件控制:常规事件控制、命名事件控制、或(OR)事件控制和电平敏感事件控制。(这四个的区别联系以后会说,现在只需要知道有这四种,最常用的是常规事件控制和或事件控制)

锁存器、两种触发器的测试比较代码如下:

reg clk,d;

wire q1,q2,q3;

integer seed;

latch t1 (clk,d,q1);

dff0 t2 (clk,d,q2);

dff1 t3 (clk,d,q3);

initial

begin

clk=0;d=0;seed=1;

repeat(10)

begin #7 d=($random(seed)/2); end

#10 $stop;

#10 $finish;

end

always #5 clk=~clk;

endmodule

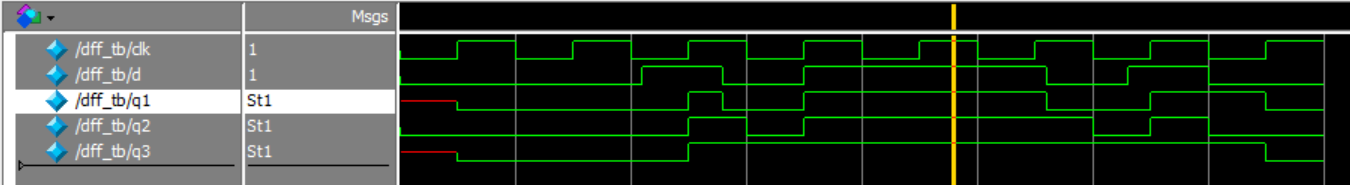

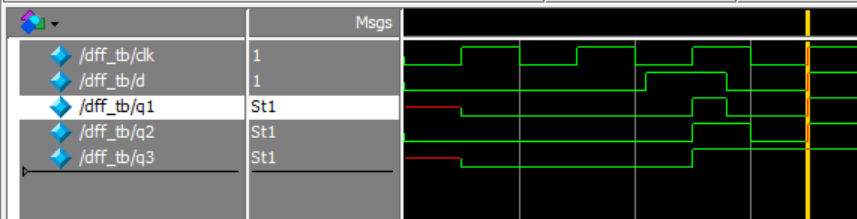

仿真结果如下:

这里的仿真只是前仿真(有关前仿真和后仿真的区别联系,就不说了,重点不在这篇博客,还有自己没有接触过后仿真,没有办法提供什么意见。),前仿真没有考虑时序问题,所以建立时间和保持时间的特点就无法实现。所以当时钟和输入信号同时变化时,按照时序的逻辑是会有问题的。所以如果仅仅是前仿真(功能仿真)可以直接看最左边的值。比如:

可以看出,此时时钟是上升沿跳变且输入为1,所以q1(电时钟的值发生变化触发)的值是1。

可以看出,此时时钟是向下降沿跳变,输入信号为0,所以q1是0。

D触发器有时需要复位信号和置位信号的Verilog描述。

这里采用异步复位信号和异步置位信号,异步就是值得变化不需要等待时钟信号。复位信号和置位信号都是低电平有效。

代码描述:

module dff2 (clk,rst,load,d,q);

input clk,rst,load;

input d;

output q;

reg q;

always @ (posedge clk or negedge rst or negedge load)

if(!rst)

q<=0;

else if (!load)

q<=1;

else

q<=d;

endmodule

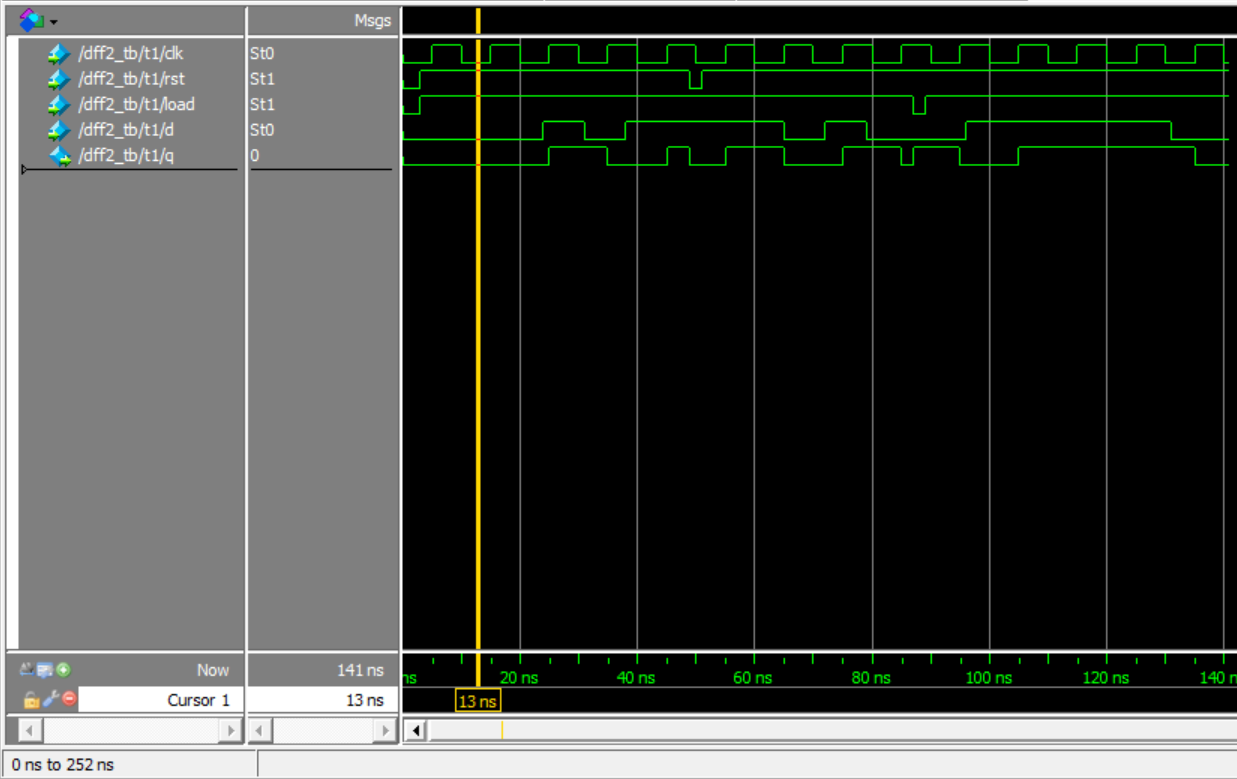

测试模块:

module dff2_tb;

reg clk,rst,load,d;

wire q;

integer seed;

dff2 t1 (clk,rst,load,d,q);

initial

begin

clk=0;rst=0;load=0;d=0;seed=1;

#3 rst=1;load=1;

repeat(6)

#7 d=($random(seed)/2);

#4 rst=0;

#2 rst=1;

repeat(4)

#7 d=($random(seed)/2);

#8 load=0;

#2 load=1;

repeat(6)

#7 d=($random(seed)/2);

#10 $stop;

#10 $finish;

end

always #5 clk=~clk;

endmodule

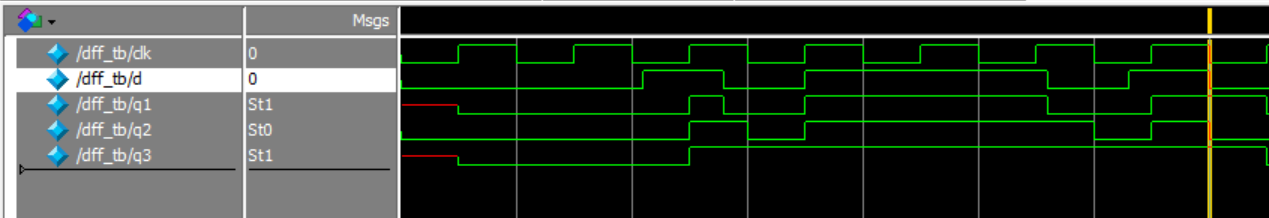

波形仿真:

总结

这篇博客是为了介绍触发器和锁存器的区别,几种功能触发器的建模。要注意触发器的种类有许多,这里只是用Verilog语言描述不同功能要求的触发器。如果学过数电应该明白触发器由于一个又一个的门级电路组成的,最简单的触发器是基本R-S触发器,在基本R-S触发器的基础上会有钟控触发器、钟控D触发器,J-K触发器、边沿触发器等等。

预告

准备写一个计数器的集合,里面有最基本的计数器和指定模的计数器。计数器的作用也有很多。

感想

慢慢来吧,争取多写一点。

最后

以上就是热心心情最近收集整理的关于使用Verilog语言描述触发器和锁存器;触发器和锁存器的区别。使用Verilog语言描述触发器和锁存器;触发器和锁存器的区别。的全部内容,更多相关使用Verilog语言描述触发器和锁存器;触发器和锁存器内容请搜索靠谱客的其他文章。

发表评论 取消回复