我是靠谱客的博主 魔幻棒棒糖,这篇文章主要介绍Verilog寄存器电路描述(异步复位、异步置位等)一、最基本的寄存器二、异步复位寄存器三、异步置位寄存器四、既有异步复位又有异步置位五、同步使能寄存器,现在分享给大家,希望可以做个参考。

寄存器电路的Verilog描述方式

- 一、最基本的寄存器

- 二、异步复位寄存器

- 三、异步置位寄存器

- 四、既有异步复位又有异步置位

- 五、同步使能寄存器

寄存器是时序逻辑设计的核心。因此,掌握寄存器模型的代码描述是非常重要的。

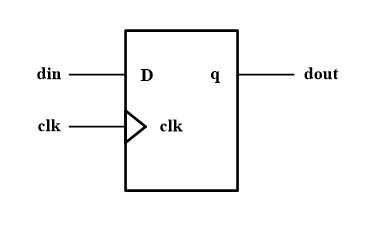

一、最基本的寄存器

功能:在clk时钟信号的上升沿,输入端数据din被锁存到输出端dout。

Verilog代码:

moudle dff(clk,din,dout)

input clk;

input din;

output dout;

reg dout;

always@(posedge clk)

begin

dout<=din;

end

endmodule

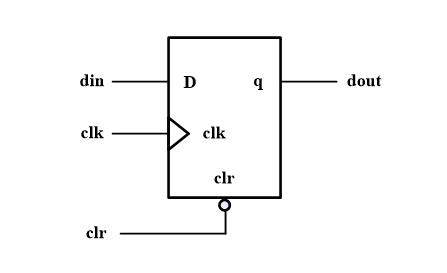

二、异步复位寄存器

功能:每个时钟信号clk的上升沿,输入端数据din被锁存到输出端dout,而异步复位信号clr的下降沿(低电平有效)可以使得输出数据dout为0,并且一直保持clr拉高后的下一个clk上升沿来临。

Verilog代码

module dff1(clk,rst_n,din,dout)

input clk;

input rst_n;

input din;

output dout;

reg dout;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) dout<=1'b0;

else dout<=din;

end

endmodule

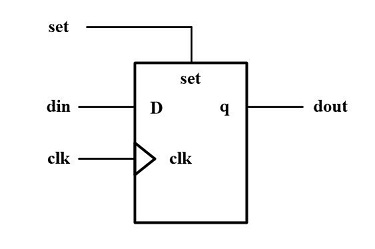

三、异步置位寄存器

功能:每个时钟信号clk的上升沿,输入端数据din被锁存到输出端dout,而异步置位信号set的上升沿(高电平有效)可以使得输出数据dout为1,并且一直保持set拉低后的下一个clk上升沿来临。

Verilog代码

module dff2(clk,set,din,dout)

input clk;

input set;

input din;

output dout;

reg dout;

always@(posedge clk or posedge set)

begin

if(set) dout<=1'b1;

else dout<=din;

end

endmodule

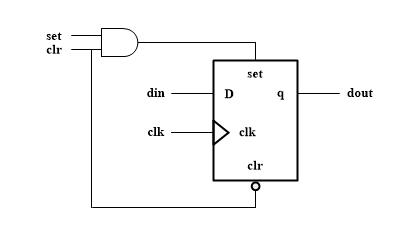

四、既有异步复位又有异步置位

功能:如果set和clr都无效,那么寄存器输出等于输入;如果set有效而clr无效,dout为1;如果set无效而clr有效,则dou为0。但是,如果set和clr同时有效的时候,输出需要设置优先级。因此,重点在于优先级的表达方式(这里令异步复位优先级高一些)。

Verilog代码

module dff3(clk,rst_n,set,din,dout)

input clk;

input din;

input rst_n;

input set;

output dout;

reg dout;

always@(posedge clk or negedge rst_n or posedge set)

begin

if(!rst_n) dout<=1'b0;

else if(set) dout<=1'b1;

else dout<=din;

end

endmodule

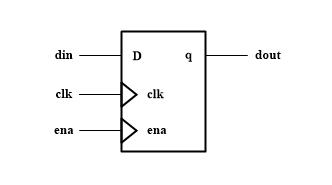

五、同步使能寄存器

功能:在每个时钟clk的上升沿,判断使能信号ena是否有效(这里为高电平有效),如果使能信号有效,dout才能输出din的值。

Verilog代码

module dff4(clk,ena,din,dout)

input clk;

input din;

input ena;

output dout;

reg dout;

always@(posedge clk)

begin

if(ena) dout<=din;

end

endmodule

最后

以上就是魔幻棒棒糖最近收集整理的关于Verilog寄存器电路描述(异步复位、异步置位等)一、最基本的寄存器二、异步复位寄存器三、异步置位寄存器四、既有异步复位又有异步置位五、同步使能寄存器的全部内容,更多相关Verilog寄存器电路描述(异步复位、异步置位等)一、最基本内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复