高层次描述语言(HDL)如VHDL和Verilog是综合的前端。HDL设计允许用工艺无关的方式来表示。然而,不是所有的HDL结构都能被综合,不仅如此,也不是所有的HDL代码都能综合成想要的结果。

1. 不完全敏感信号表

DC对在process或always块中却不在敏感信号表中的信号给出一个警告。然而对包含不完全敏感信号表的块,综合后的逻辑在大多数情况下是正确的,目前还没有遇到因为这种情况导致综合后的逻辑出错的事例。

2. 存储元件推断

有两种类型的存储元件——锁存器和触发器,参考链接:

Osris:Flip-Flop和Latchzhuanlan.zhihu.com

锁存器为电平敏感存储元件,而触发器通常为边沿敏感。只要锁存器的使能是有效的,锁存器就是透明的(output==input)。一旦锁存器使能无效,它在其输出端保持当时输出端的值。另一方便,触发器可以由时钟的上升或下降沿触发。

锁存器是简单器件,与触发器相比占的面积要小。然而,孙存器通常更麻烦,因为在设计中它们的存在使DFT扫描插入变得困难,而且对包含锁存器的设计进行静态时序分析特使很复杂的,这是因为当使能有效时,它们是透明的。

以下部分介绍了如何避免锁存器以及在需要时如何推断它们。

2.1 出现锁存器的情况

常见的是if else和case语句中的不规范描述。

参考链接:

Osris:Flip-Flop和Latchzhuanlan.zhihu.com

2.2 推断出寄存器的情况

一般情况下,当敏感信号表中指定了一个边沿,就可以推断出一个寄存器,这个边沿可以是上升沿也可以是下降沿。

下述例子是上升沿触发的D触发器:

always @(posedge clk)

reg_out <= data;

下述例子是一个带异步复位的D触发器:

always @(posedge clk or posedge reset)

if(reset)

reg_out <= 1'b0;

else

reg_out <= data;

如果将上述例子的”reset“信号从敏感信号表移除,就得到同步复位。在这种情况下,由于块只由时钟沿触发,所以也只在时钟沿进行复位。

工艺库中如果缺乏下降沿/负边沿触发的触发器,会导致DC推断一个带反相器的上升沿触发的触发器。

3. 多路选择器推断

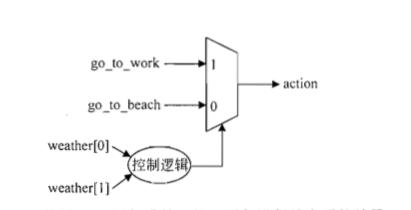

依据设计要求,可用不同的方法进行HDL编码来推断使用多路选择器的各种结构。它们包括所有输入到输出有相同延时的单个多路选择器,或使用接连结构多路选择器以优先选择输入信号的优先级编码器。

3.1 使用case语句的多路选择器

通常,if语句用于推断锁存器和优先级编码器,而case语句用于实现多路选择器。为避免在case语句中综合出锁存器,case语句的default部分(对于Verilog)应当总是被指定的。

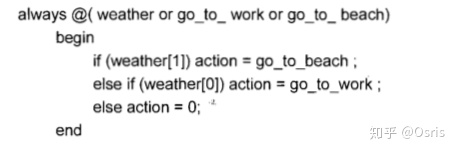

3.2 if语句与case语句——优先级事例

有多个分支的多重if语句生成优先级编码器结构。

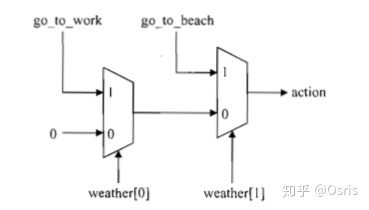

该例子中,综合后将生成级联多路选择器结构的优先级编码器,如图所示:

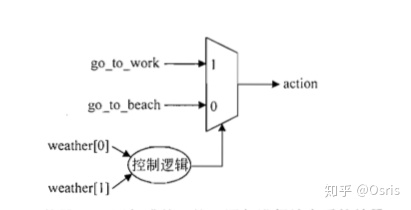

如果上例使用case语句,可以得到这样的综合结果:

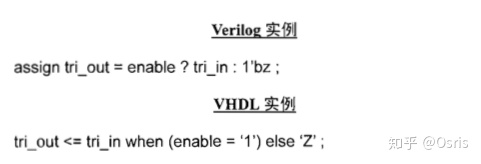

4. 三态推断

当高阻(Z)赋给输出时,可以综合出三态逻辑,一般不使用三态逻辑,原因如下:

——降低可观测性;

——难以被优化,因为不能缓冲:这可能导致max_fanout为例和重负载连线。

然而,三态逻辑却能够显著节省面积。

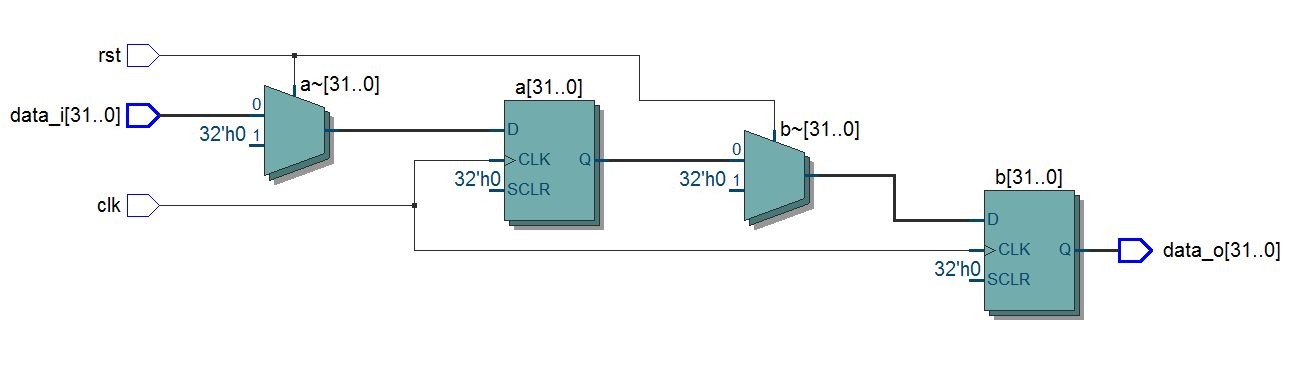

5. 顺序相关

Verilog/VHDL都提供顺序相关/无关的变量赋值。以Verilog为例,其包含阻塞与非阻塞两种赋值方式

参考链接:

Osris:阻塞赋值与非阻塞赋值zhuanlan.zhihu.com

本节和上一节:

https://mp.weixin.qq.com/s?__biz=Mzg4OTIwNzE4Mg==&mid=2247483744&idx=1&sn=7ace293fec7a9a904ab89e846e4f1fc2&chksm=cfee2181f899a897039450555004872d1a29caacca725f2f6f96abbf64cd96d2e277a919eec6&token=171333774&lang=zh_CN#rdmp.weixin.qq.com主要介绍了适用于综合的划分和编码风格,其重点在于编写设计时要”考虑硬件电路“。

最后

以上就是聪慧过客最近收集整理的关于双 JK 触发器 74LS112 逻辑功能。真值表_HDL逻辑推断的全部内容,更多相关双内容请搜索靠谱客的其他文章。

发表评论 取消回复