在设计同步八进制可逆加减法计数器前, 要将设计的流程了然于心:

①逻辑抽象(输入输出变量/状态变量/状态编码/所需触发器数量/状态转换关系),

②绘制状态图, 之后将其转换为状态表,

③根据状态表绘制状态激励表,

④根据状态激励表(通过卡诺图化简方式)求出输出方程/激励方程组,

⑤检查设计电路的自启动功能(将无效状态代入状态特性方程, 判断无效状态能否进入闭环)(若有无法进入循环的无效状态, 必须将该状态重新指向闭环中的任一状态),

⑥绘制逻辑图(根据输出方程/激励方程组来绘制)(由于是同步时序逻辑电路, 故所有触发器连接同一CP脉冲信号),

⑦绘制加入无效状态后的状态图(在有效状态不是全编码的情况下, 除了有效的状态, 还有一些无效状态, 电路若从无效状态启动, 也能进入到闭环中)(此处设计的电路由于电路采用全编码, 所以无无效状态, 也就不需检查电路自动动功能),

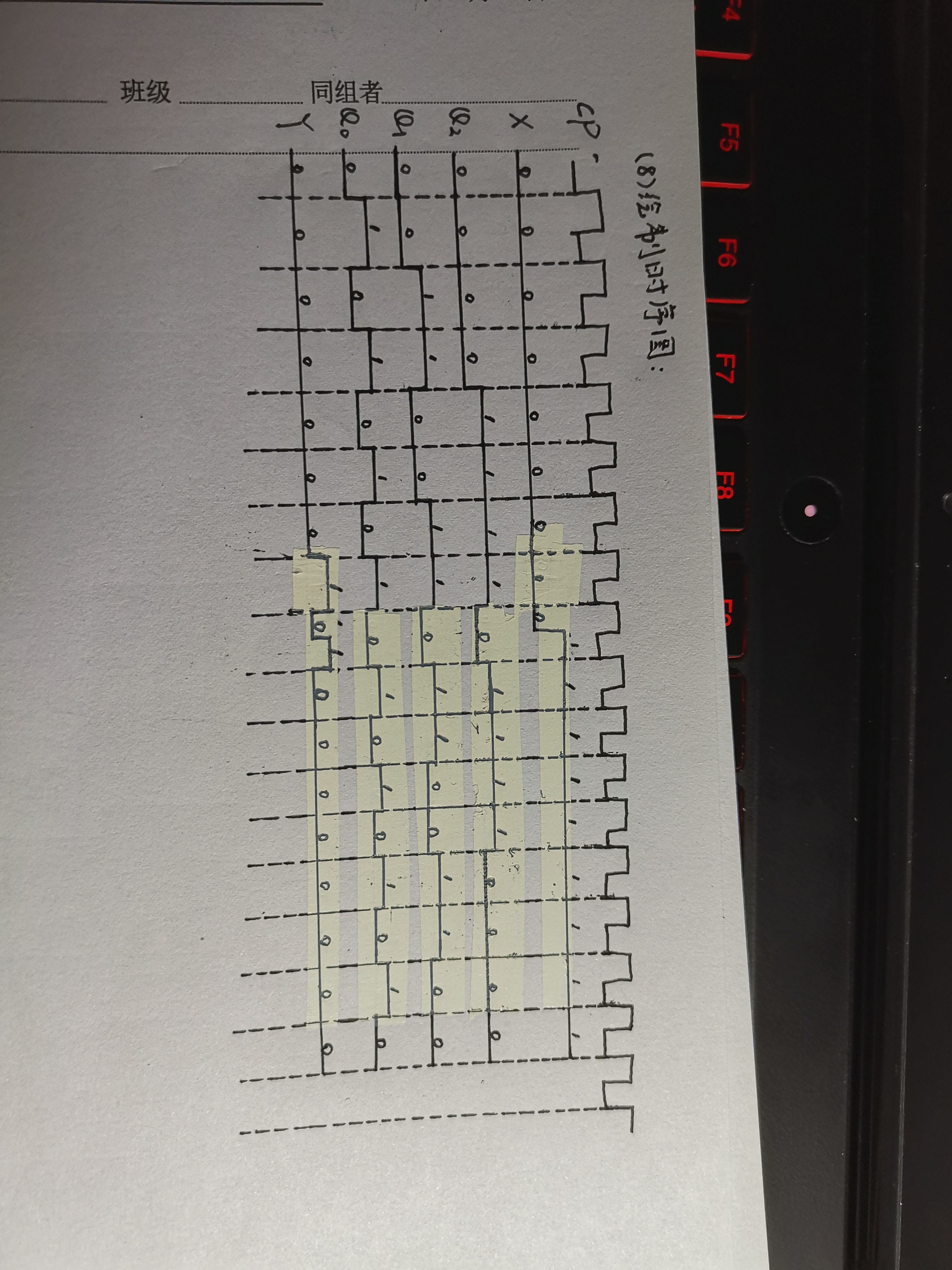

⑧绘制时序图(注意在加法和减法功能改变处的时序图画法).

最后

以上就是舒适小虾米最近收集整理的关于同步八进制可逆加减法计数器设计的全部内容,更多相关同步八进制可逆加减法计数器设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复