时序逻辑电路的设计

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

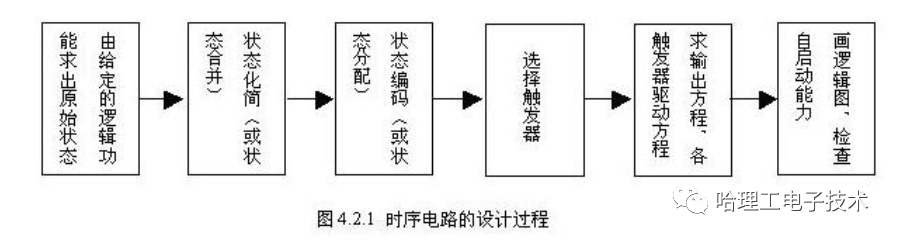

设计时序逻辑电路的一般步骤

111数据检测器的没计

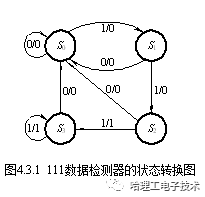

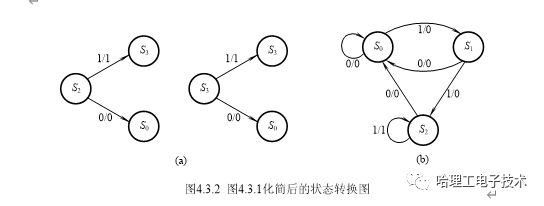

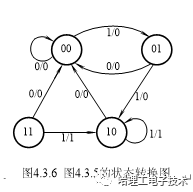

试设计一个串行数据检测器,它具有一个输入端和一个输出端,输入为一串随机信号,当连续输入三个或三个以上的1时,输出为1,否则输出为0。(1)建立原始状态转换图。为了建立检测器的状态转换图,我们首先假设以下几个状态:S0——没有输入1以前的状态;

S1——输入一个1以后的状态;

S2——连续输入两个1以后的状态;

S3——连续输入三个或三个以上1以后的状态。

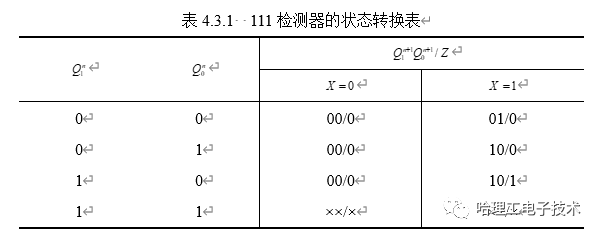

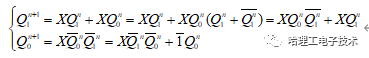

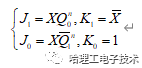

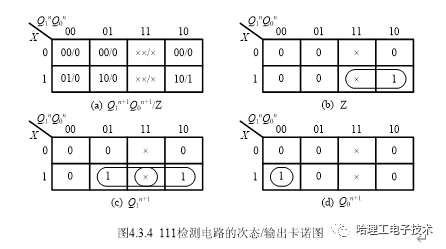

(4)选定触发器类型、求输出方程、状态方程和驱动方程。选用JK触发器组成该电路,并根据状态转换图(或状态转换表)画出其次态卡诺图和输出卡诺图,如图4.3.4(a)所示。为了便于化简,可将图4.3.4(a)分解为(b)、(c)和(d)三张卡诺图,化简后可求出输出方程为Z=XQn

状态方程为

驱动方程为

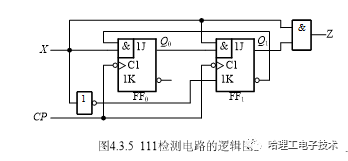

(5)画逻辑电路图

(6)检查自启动。

最后

以上就是怕黑小霸王最近收集整理的关于双 JK 触发器 74LS112 逻辑功能。真值表_【数电笔记】时序逻辑电路设计举例的全部内容,更多相关双内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复