【数电专栏】

前些天发现一个通俗易懂,风趣幽默的人工智能学习网站:

传送门

文章目录

- A 数据分配器和数据选择器

- A.a 数据分配器

- A.b 数据选择器

- A.c MSI数据选择器及其应用

A 数据分配器和数据选择器

A.a 数据分配器

<1> 数据分配器工作原理

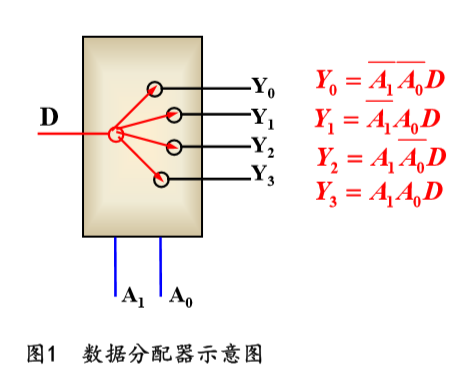

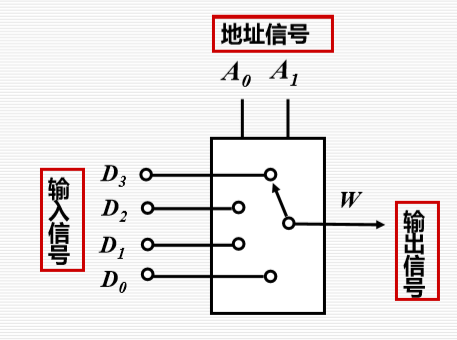

数据传输过程中,有时需要将数据 分配到不同的数据通 道上,能够完成这种功能的电路称为数据分配器,亦称多路分配器、多路调节器, 简称DEMUX,其电路 为单输入、多输出形式。其原理框图如图 1所示。

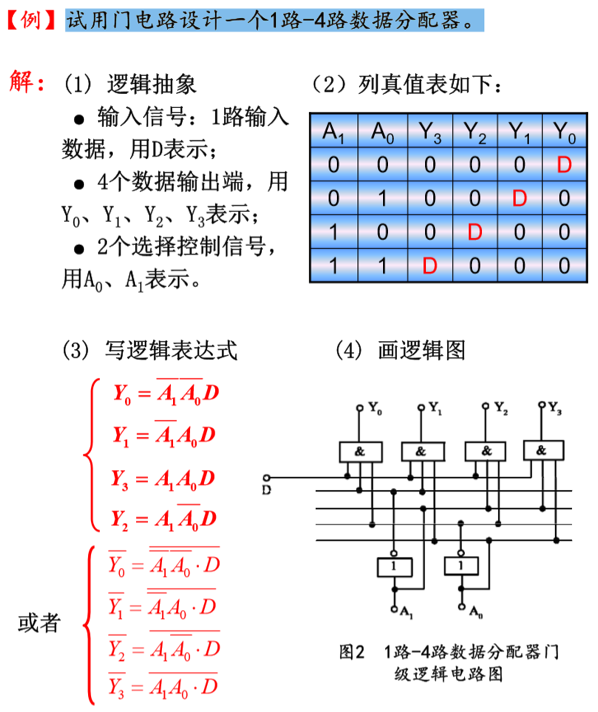

数据分配器门级电路设计举例:

<2> 数据分配器和译码器的联系与区别

- 数据分配器和译码器有着相同的基本电路结构形式——由与非门组成的阵列;

- 在数据分配器中,D是数据输入端,A1A0是选 择信号控制端;在二进制译码器中,与D相应的是选 通控制端,A 1A0是译码输入端;

- 二进制译码器通常即可用作数据分配器,n线 2 n 2^n 2n线译码器即为1路- 2 n 2^n 2n路数据分配器

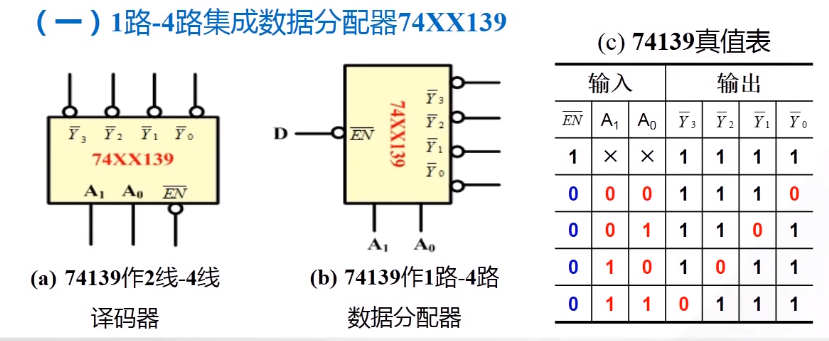

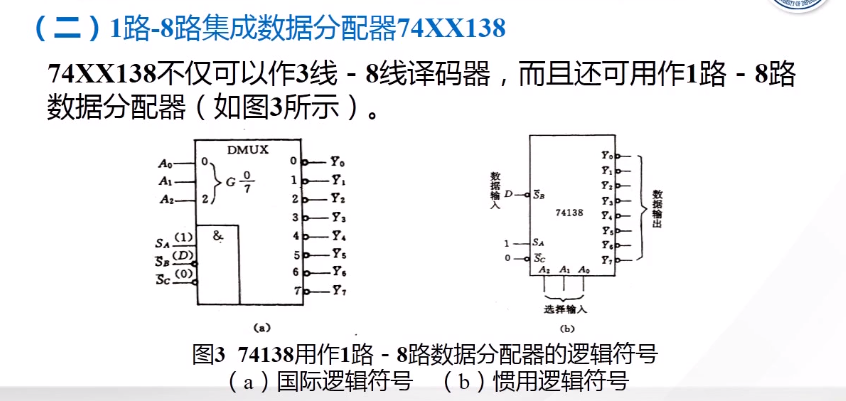

<3>MSI数据分配器

译码器用作数据分配器使用例子:

数据分配器和译码器是完全相同的两个器件,只是应用的侧重点不同而已。

如果A2A1A0为000,则选中Y’0,如果D为低电平,则片选有效,从Y’0正常溢出低电平。而如果D为1,则使能端无效,全部输出端封锁在高电平,Y;0输出高电平。

A.b 数据选择器

<1>数据选择器工作原理

数据选择器与数据分配器的功能正好相反,它完成从一 组输入数据中选出某一个的功能,是一种称为数据选择器 (Data Selector )或多路开关(Multiplexer )的逻辑电路。

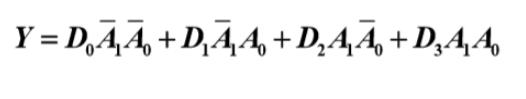

逻辑函数表达式:

A1A0确定时,相当于输入D的某一路确定

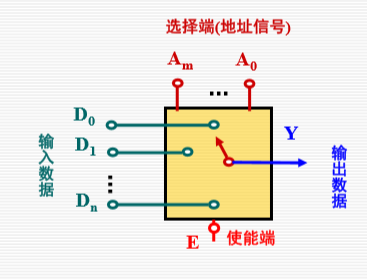

从多路输入数字信号选择一个需要的信号输出。又称多路转换器或多路开关:

n与m关系:

2

m

=

n

2^m=n

2m=n

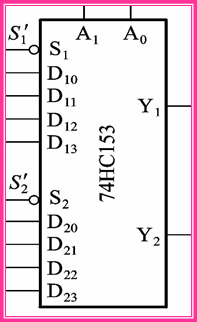

双4选1数据选择器74HC153:

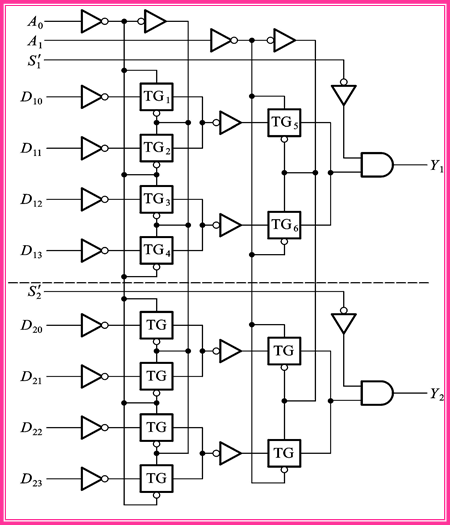

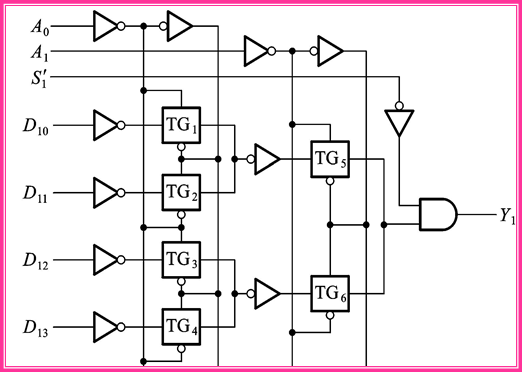

内部电路图:

电路图:

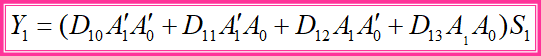

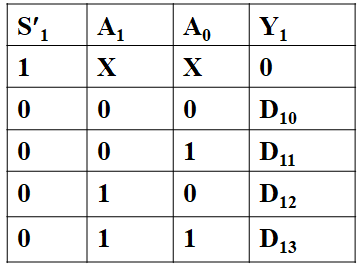

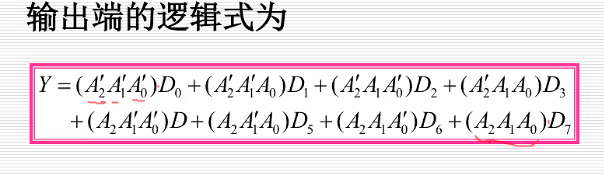

输出端的逻辑式:

其中对于一个数据选择器:

D

10

−

D

13

:

D_{10}-D_{13}:

D10−D13:数据输入端

A

1

、

A

0

:

A_1、A_0:

A1、A0:选通地址输入端

Y

1

Y_1

Y1:输出端

S

1

:

S_1:

S1:附加控制端

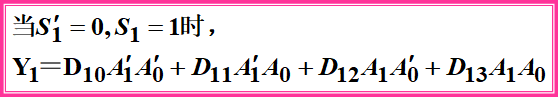

A.c MSI数据选择器及其应用

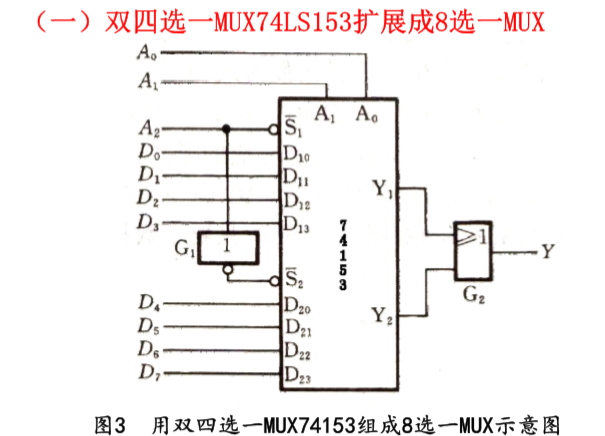

- 级联扩展; (2个4选1=》8选1)

- 实现组合逻辑函数;

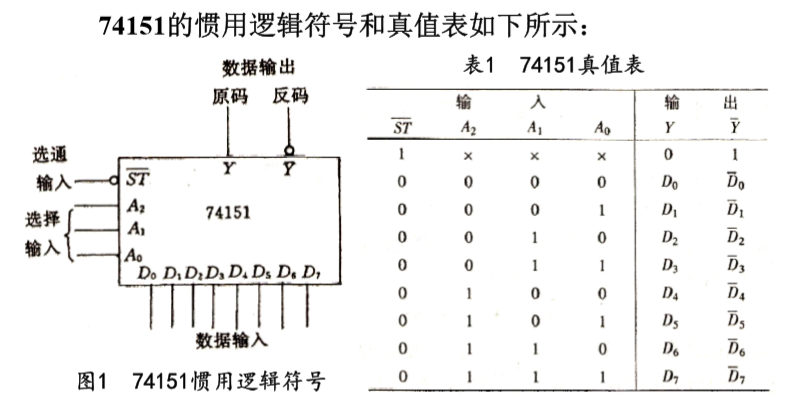

<1>八选一数据选择器74XX151

八选一MUX需要3个选择输入端,8个数据输入端,并 有互补的原码和反码两种输出形式。

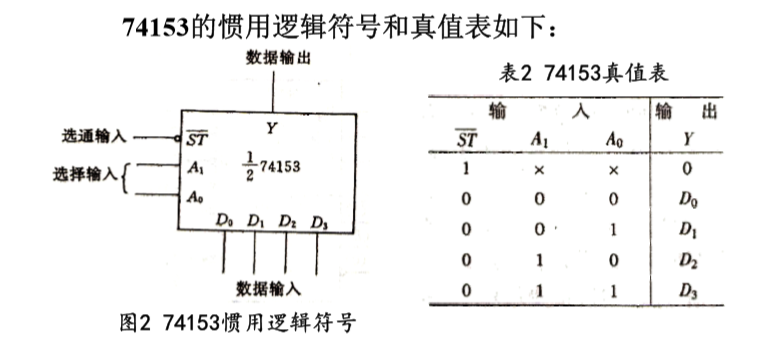

<2>双 4选1数据选择器74XX153

74153包含两个完全相同的4选一MUX,两个MUX 有公共的地址输入端,而数据输入和输出端各自独立。 通过给定不同的地址代码(A1A0),即可从4个输入数据 中选出所需要的一个,并送至输出端Y。

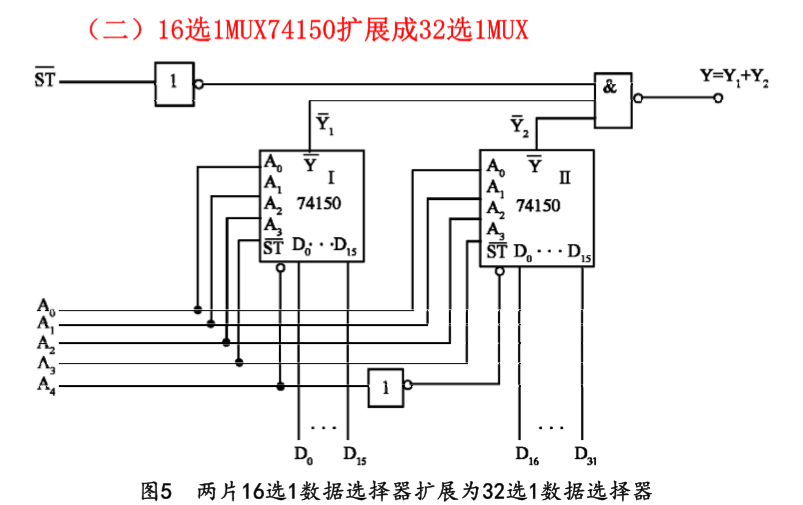

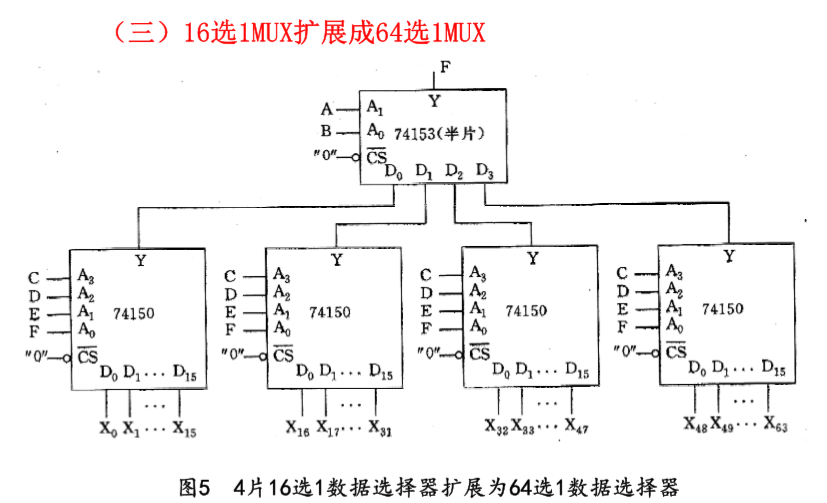

<3>集成数据选择器的扩展

Y

1

Y_1

Y1和

Y

2

Y_2

Y2必有一个是零,相或得到Y等于另一个。

A

2

A

1

A

1

A_2A_1A_1

A2A1A1为000到011时,

A

2

A_2

A2始终为0,则

S

‾

2

overline{S}_2

S2此时为1,下片被封锁,

Y

2

Y_2

Y2始终输出为0。

100到111,则同理得到上片封锁。

A

4

A

3

A

2

A

1

A

0

A_4A_3A_2A_1A_0

A4A3A2A1A0为00000到01111时,1片选通有效,2片选通无效。

100000到11111则相反。

C S ‾ overline{CS} CS为0,五片同时选通。A1A0对D0D1D2D3进行选择。

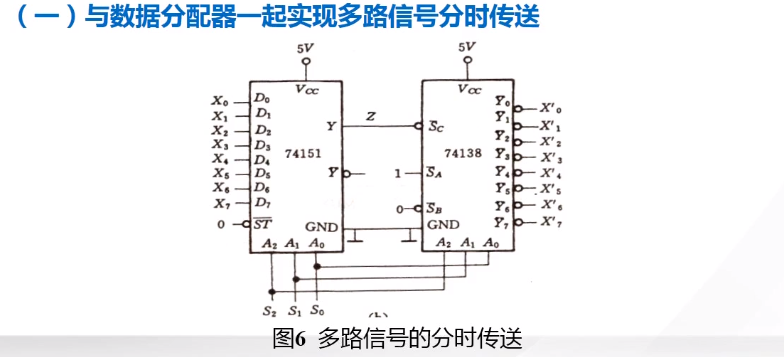

<3>集成数据选择器的应用

左边是8选1的数据选择器,它的Y与右边新芯片的

S

‾

C

overline{S}_C

SC相连。两个芯片都受S2S1S0控制。

如果S2S1S0为000,此时74151选中D0,D0对应的输入X0通过Y传输到Z这个信号,如果X0为低电平,则

S

‾

C

overline{S}_C

SC有效,

Y

0

′

Y'_0

Y0′译成低电平。相反的X0为高电平,则

S

‾

C

overline{S}_C

SC为高电平,

Y

0

′

Y'_0

Y0′封锁在高电平。

如果S2S1S0按照一定时间间隔递增,那么就可以将X0到X7分时从Y’0到Y;7传输出去。

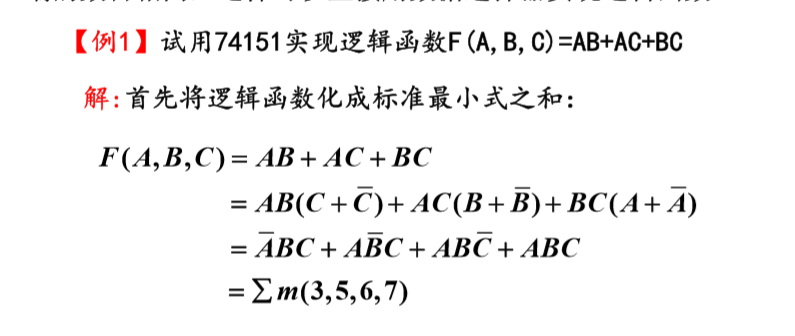

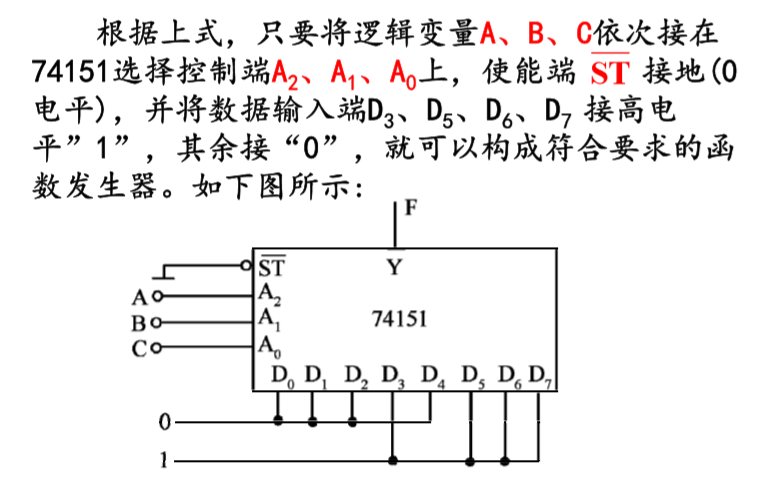

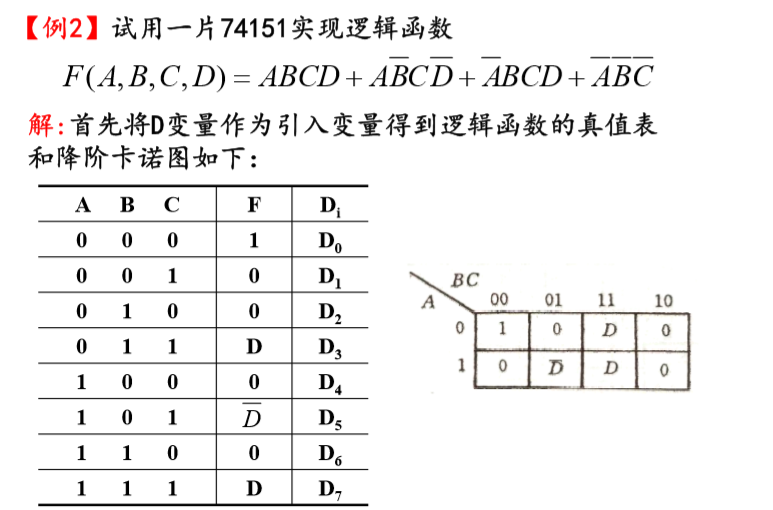

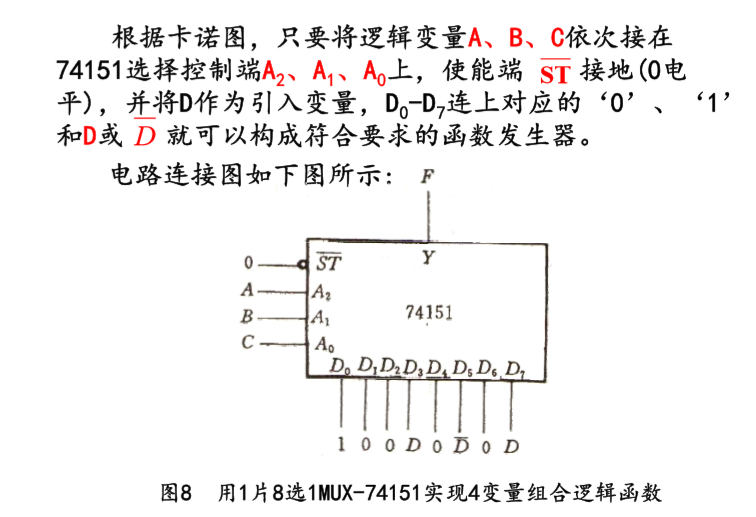

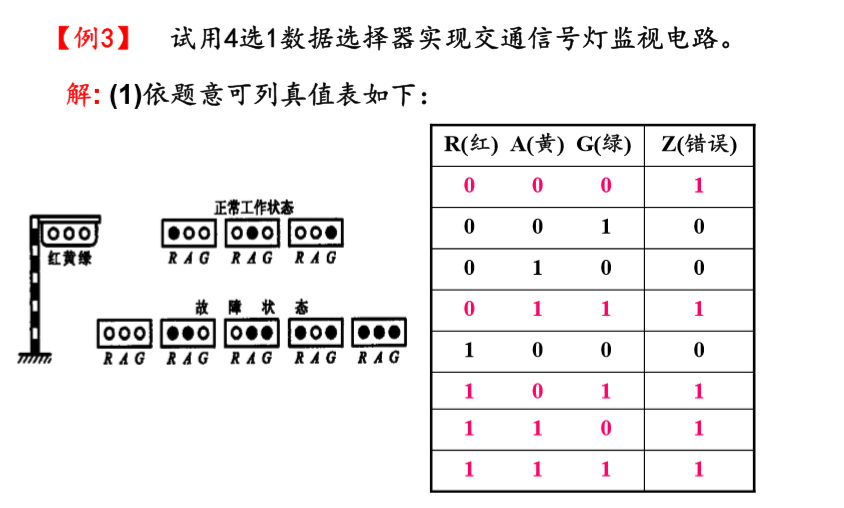

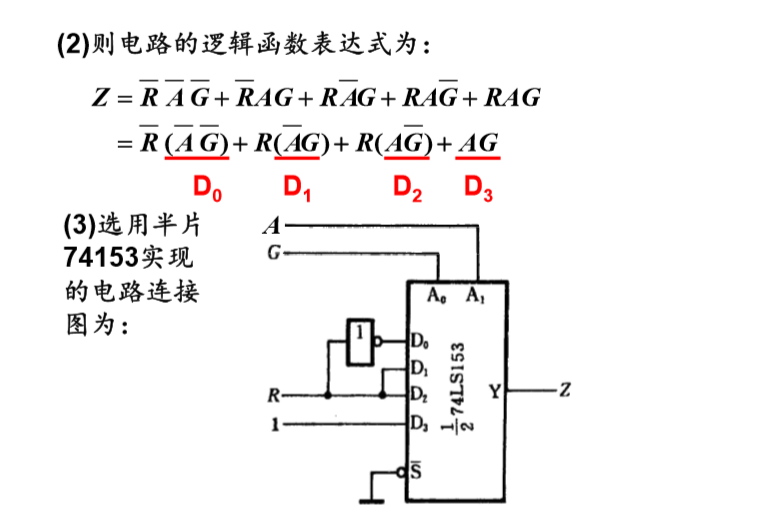

(二)用数据选择器设计组合逻辑电路

原理:若逻辑函数变量的数目与数据选择器选择输入 端的数目相等,则函数最小项的数目就与数据选择器输入端的数目相同,这样可以直接用数据选择器实现逻辑函数。

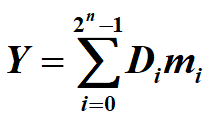

1 数据选择器输出变量的一般表达式:

n

:

n:

n:数据选择器的地址变量个数

M

i

:

M_i:

Mi:地址变量的最小项

2 表达式的特点:

具有标准与或表达式的形式:提供了地址变量的全部最小项;受片选端的控制。

受片选段的控制:

S

′

=

0

S'=0

S′=0时有效;

S

′

=

1

S'=1

S′=1时,Y=0;

一般

D

i

D_i

Di可以当作一个引入变量处理,可以取原变量、反变量、1、0.

2 设计步骤:

- 1 确定应该选用的数据选择器:n=k或n=k-1(n为地址变量个数;k为函数的变量个数)

- 2 将逻辑函数化为标准“与或”式(最小项之和形式)

- 3 写出数据选择器的输出函数表达式

- 4 对照比较,确定选择器各个输入变量的表达式(地址输入端 A i A_i Ai是什么;数据输入端 D i D_i Di是什么。)

- 5 画出连线图

使用数据选择器MUX和数据分配器DEMUX实现组合逻辑函数F的共同点是:

- 不用对F进行化简,省时方便;

- 检查和排除故障容易;

- 可以使集成芯片的数目减到最少。

最后

以上就是勤奋芒果最近收集整理的关于(十一)【数电】(组合逻辑电路)数据分配器和数据选择器A 数据分配器和数据选择器的全部内容,更多相关(十一)【数电】(组合逻辑电路)数据分配器和数据选择器A内容请搜索靠谱客的其他文章。

发表评论 取消回复