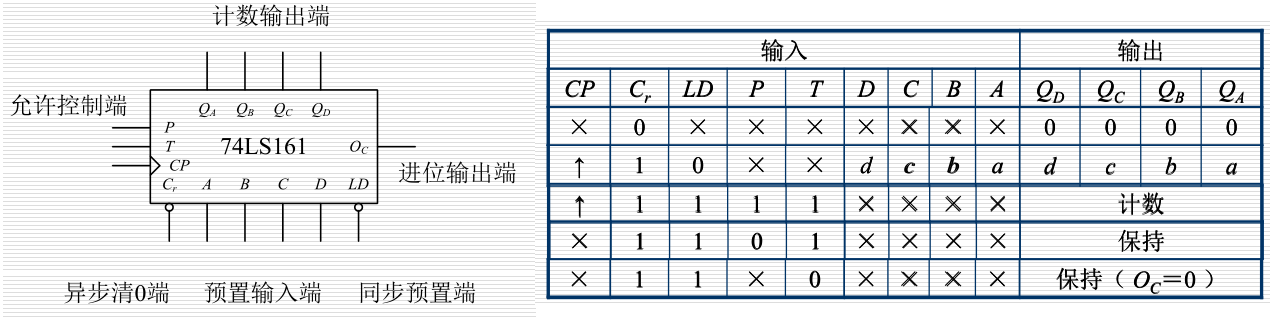

- 74LS161是模16(四位二进制)同步集成计数器,异步清零

- 一张功能表时刻准备查询

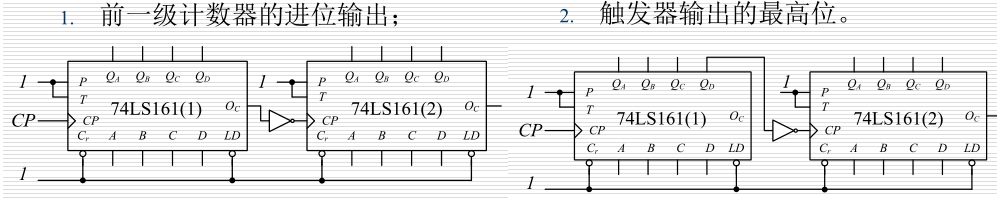

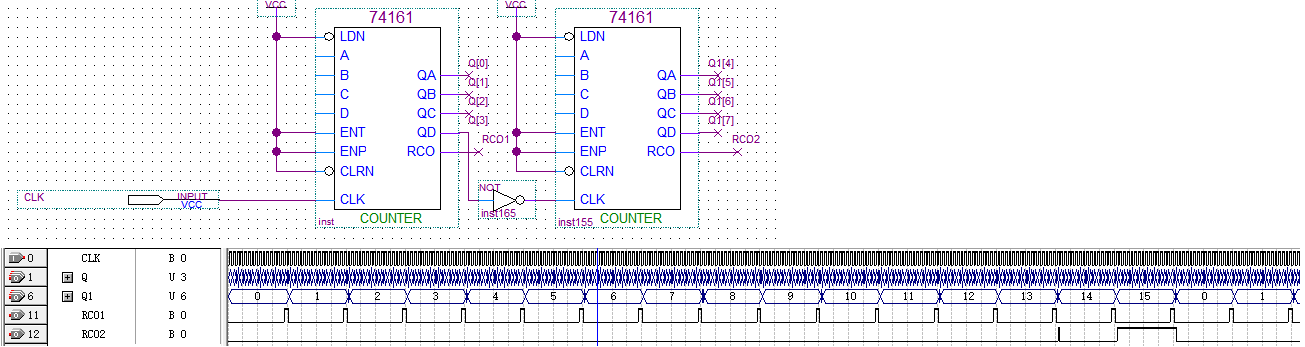

- 异步级联方法:将前一计数器的输出作为后一级计数器的时钟信号

- 两片161所需要的时钟不同称为异步

- 前一级计数器的进位输出

- 触发器输出的高位

- 为何需要加反相器——74161时钟上升沿触发 ,进位输出一个高电平,采用由低变高的边沿输出到时钟不稳定。加了一个反相器相当于下降沿触发,等电平经过一段时间稳定后触发时钟。还有一个原因是用上升沿触发将导致下一级161提前一个时钟周期计数,下降沿触发时等15完全输出后再计数。

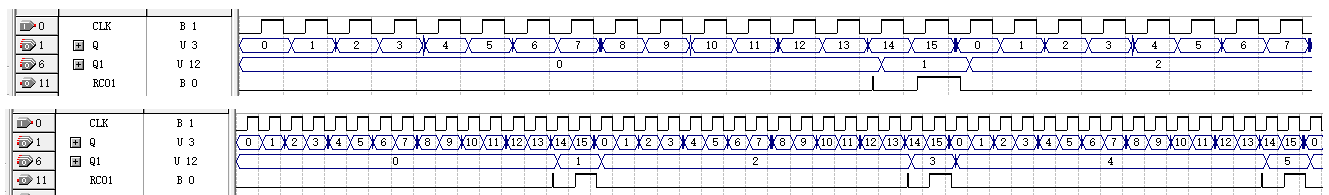

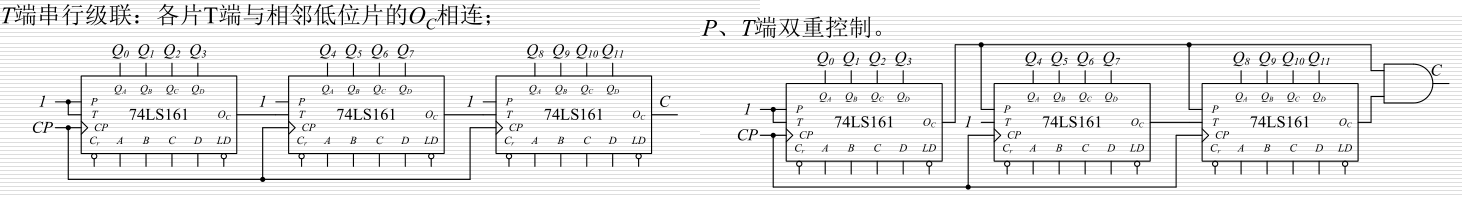

- 通过仿真分析,可以看到假设是美好的。当出现毛刺时,瞬时下降沿同样会造成下一级的161的状态翻转而造成计数错误

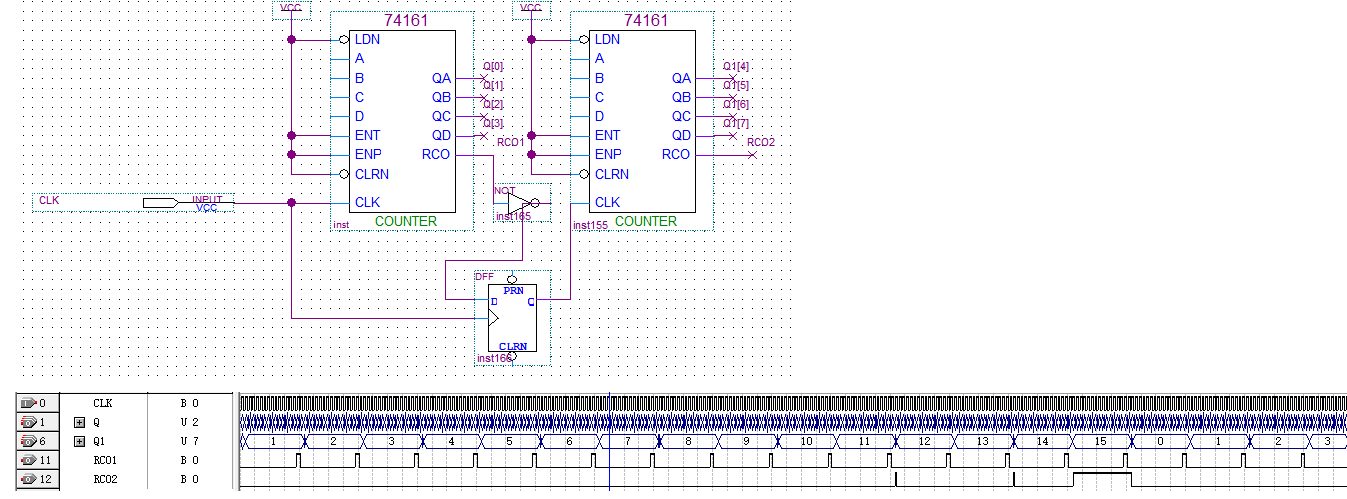

- 解决办法是加一个D触发器过滤掉毛刺,可以看出此时计数规律,第一个计数器计到15时第二个计数器开始输出1。

-

仿真小技巧:第一个计数器输出用一个总线命名,第二个计数器输出用一个总线命名,再把属性设置为无符号十进制,就方便查看计数到几输出

-

第二种情况是利用最高位QD输出从1111->0000时下降沿,加反相器输入进时钟。这种未加D触发器,波形看起来比第一种干净

-

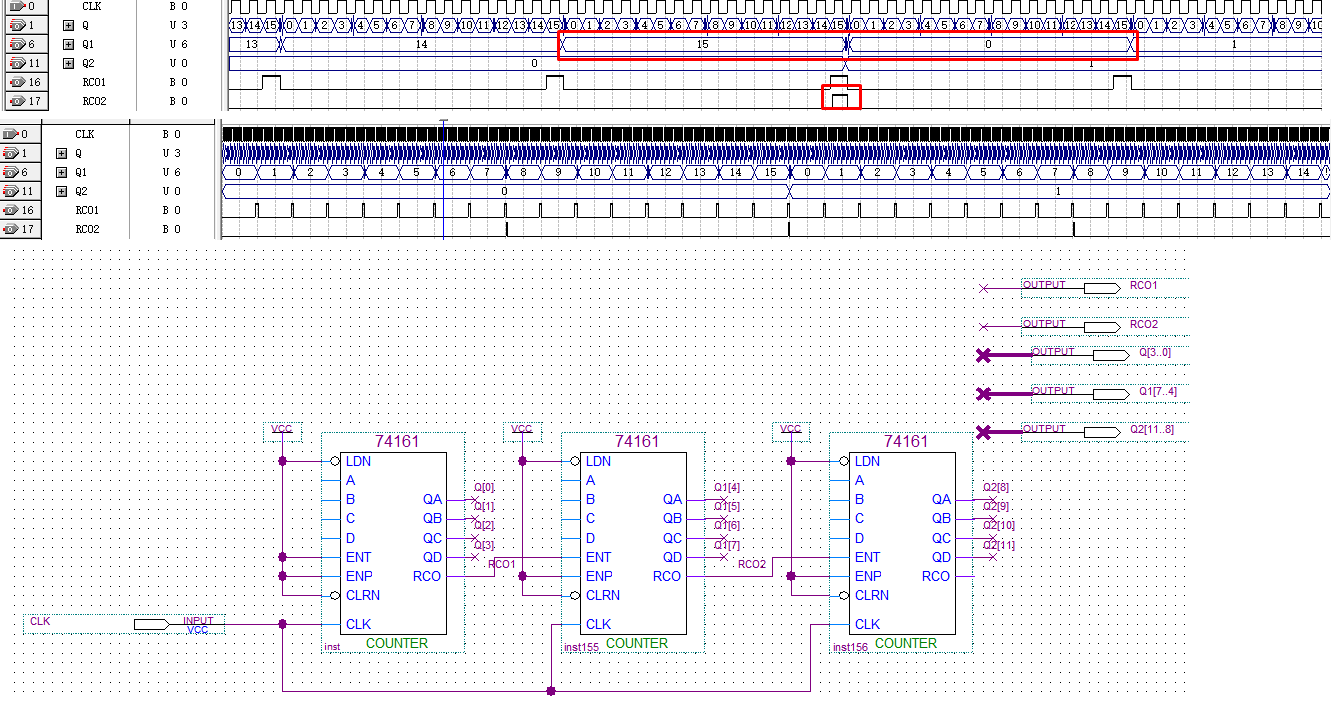

同步级联一般方法:将前一计数器的输出作为后一级计数器的使能信号,

所有计数器使用相同的时钟信号。- T端串行级联:各片T端与相邻低位片的OC相连;

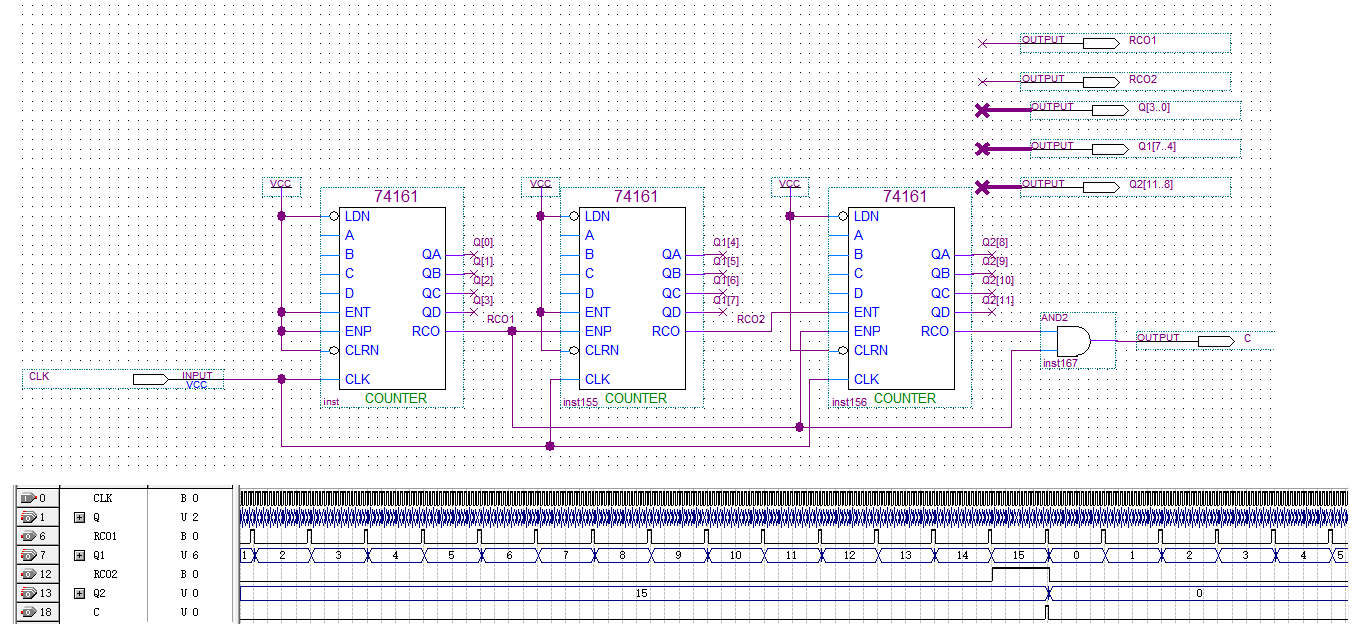

- PT端双重控制

- 只有当OC输出为1时下一级161才可以计数。当第一级OC为0时,第二级161输入T为0,保持当前数值直到上一级OC输出1。当第二级161计到15时,OC2输出一个高电平驱动第三片161工作。

- 第二种方式速度计数较快

最后

以上就是笨笨手套最近收集整理的关于quartus仿真31:74161的级联的全部内容,更多相关quartus仿真31:74161内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复