布线是继布局和时钟树综合之后的重要物理实施任务,其内容是将分布在芯片核内的模块、标准单元和输入输出接口单元( I /O pad)按逻辑关系进行互连,其要求是百分之百地完成它们之间的所有逻辑信号的互连,并为满足各种约束条件进行优化。能否按照设计的需求将信号线布通是决定芯片是否能够流片的首要前提。进行消除布线拥塞(congestion)、优化时序(timing)、减小耦合效应(coupling)、消除串扰(crosstalk)、降低功耗、保证信号完整性(signal integrity)、预防DFM问题和提高良品率等布线的优化工作则是衡量布线质量的重要指标。

超大规模集成电路多层布线采用自动布线方法,它是由双层PCB(printed circuit board),布线和FPGA通道布线等方法发展而来的一种复杂的布线方法。在实施过程中,它被分为全局布线(global routing)和详细布线(detail routing)以及布线修正(search and repair)三个步骤来分别完成。自动布线的质量依赖于布局的效果以及EDA工具中所采用的布线算法和优化的方法。

一、全局布线

全局布线是为详细布线(或称作最终布线,final routing)做好准备。它首先要制定全局布线的目标,然后根据设计的特征,做出具体的规划。比如,需要布线的设计可以是芯片,也可以是定制设计的大模块。芯片的形状可以是正方形,也可以是长方形。对芯片的布局布线做规划时,首先要了解它的特征。芯片通常是由标准单元和模块(block)组成,根据这两部分的比例,我们可以将芯片区分为3 种类型:

- 全部由标准逻辑单元组成的设计(CBlC,cell-based IC )

- 标准逻辑单元(例如,占总面积的20%以上)和大模块组成,常常用于ASIC设计

- 基于模块的设计(block-based design,BBD,例如,标准逻辑单元占总面积的10%以下)

1、全局布线目标

全局布线速度快、时间短,能加快收敛,它为用时很长的最终布线做好规划。如果全局布线发现问题,人们可以及时解决调整,而不必再花费很长时间去做最终布线及其他后续工作。全局布线的主要目标有:

- 使总连接线最短。

- 布线分散均勻不致引起局部拥塞。

- 使关键路径延时最小,遵守时序规则。

- 理解信号完整性的要求,避免串扰(cross talks)。

- 保持将BUS总线聚集相连等。

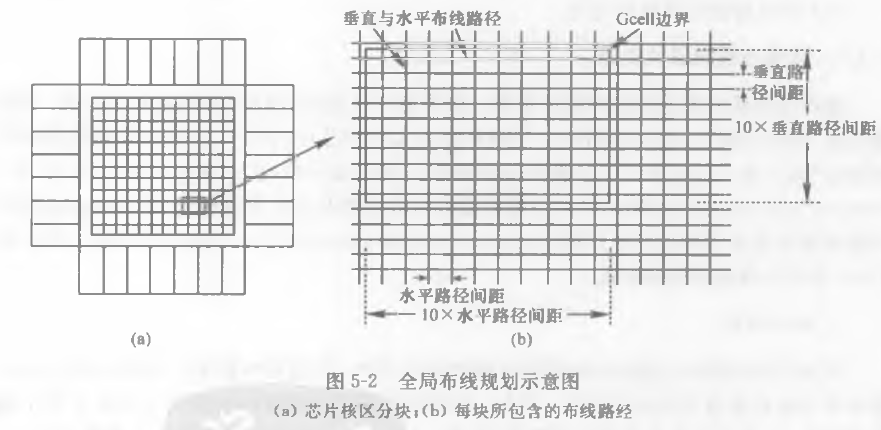

2、全局布线规划

全局布线对整个芯片的走线做全局规划,以便确定即使是很大的芯片设计它的最终布线计划也能实现。全局规划是一种“松散”的布线,它将芯片核区预先划分成若干大方块(也可以是长方块),每个方块纵横方向可以走多条线(例如,10条线,线的数目根据设计特征也可以修改)。这样布线时可以同时规划多条走线方案,极大地加快速度并尽早报告结果,以便进行调整或修改。

二、详细布线

详细(detail)布线也叫做最终(final)布线或者叫做Manhattan布线。相对于全局(global)布线,它事实上是一种局部(local)布线。全局布线做大局规划,详细布线是具体的实现。全局布线粗看松散,详细布线细看密集。全局布线快速简洁,详细布线细致复杂。

1、详细布线目标

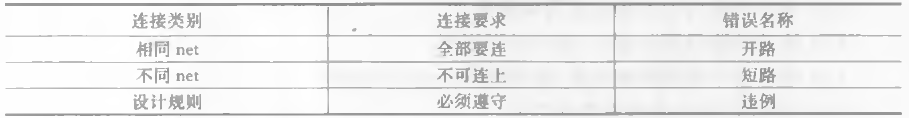

我们已经知道网表中每个逻辑单元和模块间的相互关系是通过接点(pin)来实现的,每个接点可以有多个连接终端(terminal)。需要连接在一起的一条网线称为net。布线目标是将属于同一个net的所有pin连接上;不同net的终端不能连接;要遵守设计规则要求的距离间隔等。如果应该连接的没有连接上就产生了开路(open);不应该连接而被错误地连接上就产生了短路(short);连接后距离间隔不符合设计规则就产生了违例(violation)。

详细布线是物理实施的最后步骤,它所实现的结果将被用来作为参数提取和时序分析。详细布线的方法是在多层金属间进行连线的,它要遵循时序的要求,并能自动搜索连线错误并纠正错误,或称为布线修正(search and repair)。也可以进行递增式(incremental)的布线 ,即进行局部(area)详细布线。对详细布线的要求有:

- 必须理解所有设计规则

- 自动切换并综合利用多层金属作连线。

- 遵守时序规则,优先使关键路径的延时满足要求。

- 对总连线长度进行优化。

2、详细布线与设计规则

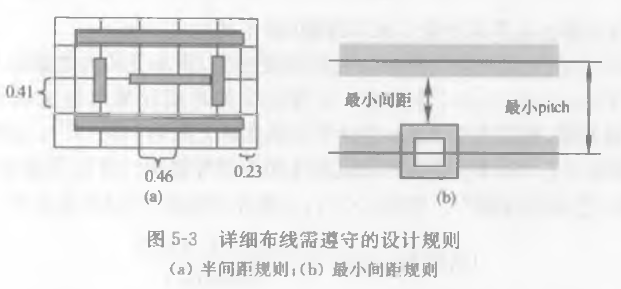

做详细布线时要遵循各种设计规则。除了遵守在版图设计时的线宽和间距外,布线是依据“布线间距”(pitch)进行的。当深亚微米(DSM)芯片(小于0. 35um)开始使用多层金属连线时,新工艺技术产生了新的规则要求。纳米设计中,由于化学机械打平(CMP,chemical mechanical polishing)的作用所提出的密度要求及由于掩模光刻(lithograph)的限制而提出的光学邻近校正(OPC,optical proximity correction)的要求,是设计布线规则的新特征。

1)设计规则

在做详细布线时,理解并处理设计规则是最基本、最重要的要求。布线间距(Pitch)在水平方向和垂直方向是可以不一样的,标准逻辑单元在摆放时会将其边界放于半个间距的位置 ,在布线时要遵守最小间距规则。它包括“线到线”(习惯称为L2L,下同),“线到孔”(L2V),“孔到孔’’(V2V)这三种规则。在版图设计和布线设计中,L2V是最常见的折中处理方法。如果(通)孔的最大宽度与线宽一致,这时只用L2L规则就行。

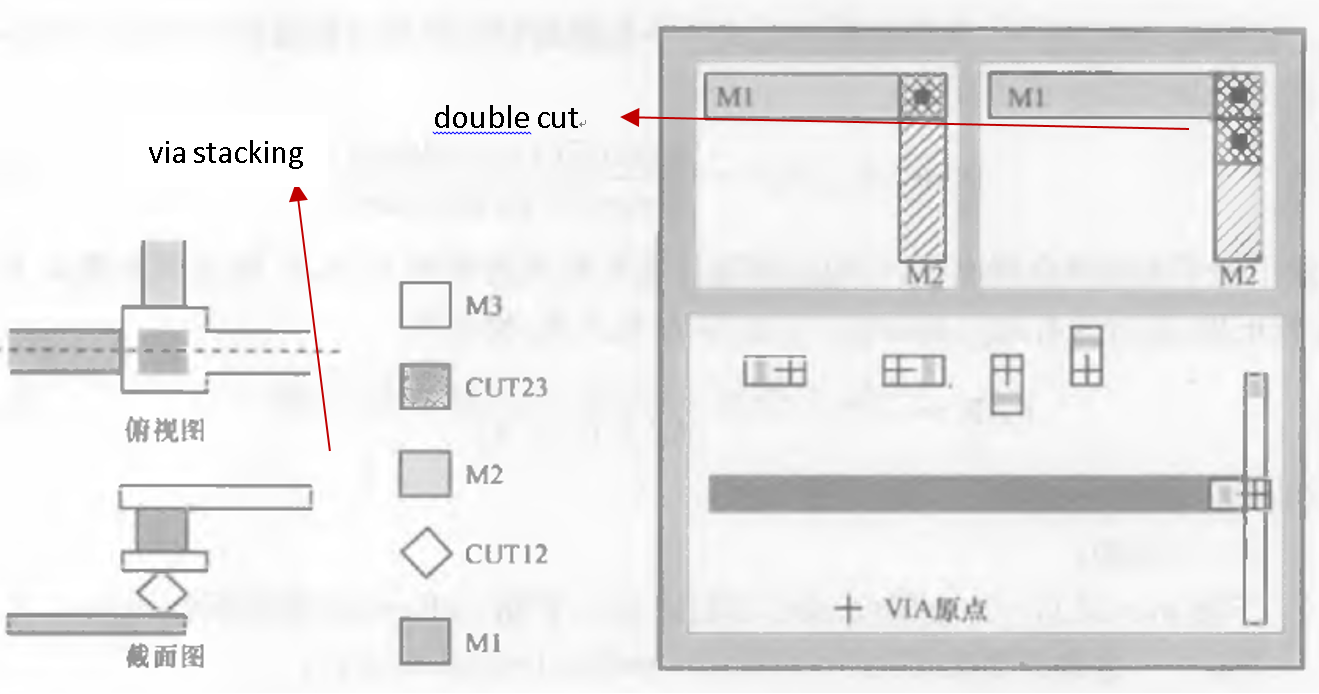

2)通孔和最小面积要求

DSM芯片设计工艺开始用到通孔叠砌(via stacking)技术,为了保证接触的可靠性,还需要遵守最小面积规则(MAR,minimum area rule),在空间允许的情况下,则可以采用双通孔(double cut)技术。

3)密度要求

在深亚微米工艺中要用到化学机械打平(CMP)方法对每层金属进行处理,并达到一定的密度要求。实现密度要求可以从两个方面去实现,一是在空白区域采用金属填充法,二是将较宽的连线切割分布。在化学机械打平中,它要求每一层互连线金属在单位区域内达到一定的密度(一般为50%〜80%),是保证均匀度的一种不可或缺的措施。在切割分布的方法中,尤其对于很宽的电源布线,开始采用的方法叫做“挖孔法”(slotting),由于其电流分布的不规则性,后来采用了均匀的“分割法"(splitting)。

详见数字后端——电源规划中电源环线的介绍

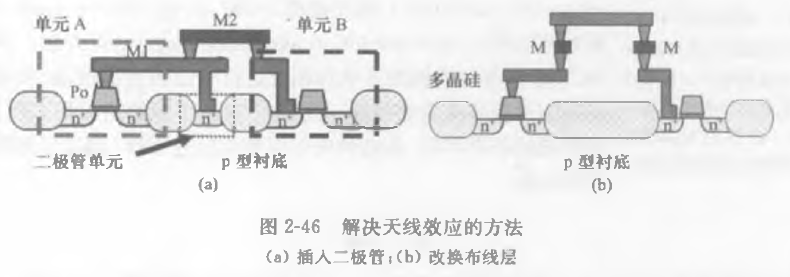

4)掩模光刻过程中的工艺天线效应

在现代等离子体蚀刻工艺和离子注入过程中产生的积累电荷,如果得不到及时释放,就会对CMOS器件的栅极产生击穿并造成永久性的损伤,这就是工艺天线效应(PAE,process antenna effect)。所谓天线,是指在两次工艺之间连接到栅极多晶硅(poly)和金属线处于悬空不接地的状态而形成的天线结构。为了预防工艺天线效应,在最终布线过程中,是通过连接天线二极管(antenna diode)或跳转到上一层金属(layer hopping)以增强CMOS栅极的静态电荷承受能力来实现的。

5)串扰在布线中的预防和修复

在0.18um设计中,信号完整性分析已经不可缺少。它要解决的首要问题是串扰,实现的方法是通过在布线中进行预防,如果在时序分析时发现问题,可以用布线器进行修复。用布线器进行预防和修复的方法包括:

- 增加走线间隔

- 将关键信号线屏蔽

- 缩短平行走线的长度

- 转换到另一层连线

- 加入缓冲器

6)纳米布线规则

近年来已经大量设计中提出了新的纳米布线规则。由于在掩模光刻中OPC的限制,必须应用光罩(分辨率)增强技术(RET)的方法遵循特殊设计规则进行校正。纳米设计规则包括平行重叠间隔规则(parallel overlap cut spacing)、线端规则 EOL(end of line spacing)、最小分级最大边缘规则(minimum step maximum edge)、最大悬浮面积规则(maximum floating area)。这些纳米设计规则是通过LEF的技术文档进行定义和控制。

7)对角(45 °)布线规则

在65nm及以下的设计中,顶部几层金属连线可以用45°方向的规则来实现,这种连线也称为“重新分布层"(RDU,redistribiition layer)。它们的连接所用层、宽度和间距可以由使用者进行定义。

3、布线修正

布线修正(search and repair)是最终布线的一个重要功能。它给用户提供一个方便的选项,根据实际情况采用以下的一种方式,进行布线修正会大大节约时间。

1) 自动修正

在布线开始时如果选择自动修正功能,当最终布线完成发现结果有错误时,布线工具会自动去搜寻并修正错误,这样避免用户从头开始对整个芯片重新做布线规划,节省了运行时间。一般对于布线很困难的设计在第一次布线时,通常不选择自动修正,而是尽快获取初步结果。当布线错误不多时,选择自动修正功能会加快总的设计时间。反之,如果存在大最布线错误并需要运行很长时间时,选择自动修正是很不经济的方法,应当先找出问题后进行相应的调整再去重复布线工作。

2)渐进修正

当布线的错误发生在一条或多条网线(net),对它们进行修复时,就可以选择渐进( incremental)布线的方法进行修正。

3 )局部修正

在很多应用中,布线的错误会发生在较小的区域,这时选择局部范围对其进行布线修正则是一个最佳的办法。局部区域的选择通常用布线路径(track)来定义,例如,选择宽和高为10X10的路径。在一些特殊设计中,芯片或子模块为长方形(例如,很宽很矮)时,布线错误又很多,合适地选择局部区域大小进行局部修正就很重要。渐近修正和局部修正往往和渐近布局方法结合起来。

三、特殊布线

1、电源布线

详见 数字后端——电源规划

2、时钟树布线

详见 数字后端——时钟树综合

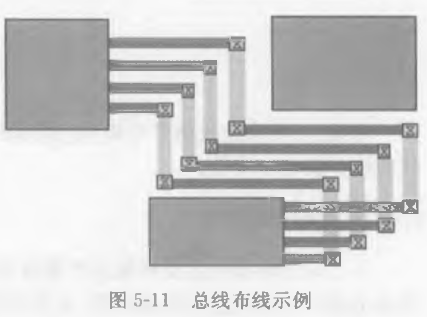

3、总线布线

在CPU芯片等设计中需要做若干总线(bus)布线,并往往要求布线长度同步一致,以减小同一组总线延时的差别。处理和控制布线长度的方法可以采用“手风琴式”和“长号式”。适合总线布线要求的有基于形状(shape-based)的布线器,它可以充分利用空间,并调节总线的长度以达到要求。总线布线中处理和控制布线长度的方法在数模混合设计中得到较多应用。

4、实验布线

全局布线和详细布线方法能够实现符合产品质量最终的结果,但通常需要的时间也较长。在实际应用中,为了尽快尽早了解设计的初步结果,还可以用虚拟(virtual)布线或实验(trial)布线。在布局以后,为了进行初步时序分析,可以调用虚拟布线产生快速布线结果,供时序分析使用。虚拟布线只是建立内部数据供分析用,它并不产生实际的连接线路。更加准确一点的结果则可以用实验布线来产生,它根据布局的结果,建立实际的连接线路,但它不去仔细遵循物理设计规则。因此,如果假定根据虚拟布线去预估时序的误差在20% 左右,根据实验布线去预估时序的误差会在10%左右。结果虽然不准确,但它们在早期设计应用中具有很好的工程指导意义。

最后

以上就是粗犷火龙果最近收集整理的关于数字后端——布线一、全局布线二、详细布线三、特殊布线的全部内容,更多相关数字后端——布线一、全局布线二、详细布线三、特殊布线内容请搜索靠谱客的其他文章。

发表评论 取消回复