一、实验要求

- 包含一个counter与一个state转换模块

- 当reset为1时,则count为0,state=S0

- 当reset为0时,则开始数数,state切到绿灯

- 每过clk一周期则counter+1

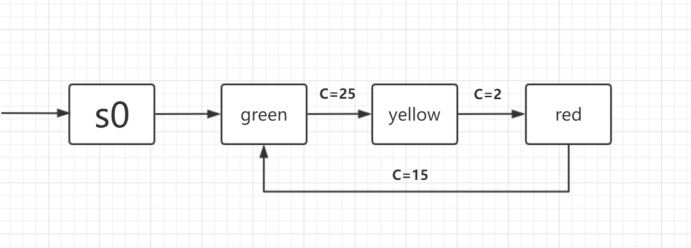

- 绿灯时,当过25周期,则切到黄灯

- 黄灯时,当过2周期,则切到红灯

- 红灯时,每过15周期,则切到绿灯

以此循环。

二、状态机

三、程序实现

1、RTL代码

module traffic_light_ctl(

clk,

reset,

state

)最后

以上就是无私铅笔最近收集整理的关于verilog 交通灯实验(使用状态机)的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复