1.实验内容: 设计一个24h制数字时钟,要求能显示时、分、秒,并可手动调整时和分。

2.实验仪器设备及软件:电脑QUARTUS2

3.实验原理及步骤: 数字钟的主体是计数器,它记录并显示接受到的秒脉冲个数,其中秒和分为模60计数器,小时为模24计数器,分别产生2位BCD码;BCD码经译码、驱动后接数码管显示电路。

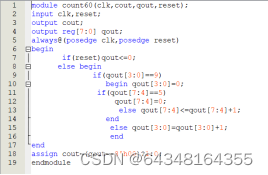

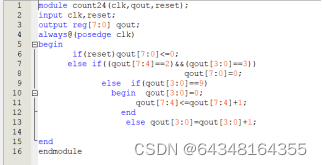

秒、分计时电路分别由模60计数器组成,时计时电路由模24计数器组成。计数可采取同步和异步两种方式:同步方式下,秒模60计数器的进位作为分模60计数器的计数允许信号,分模60计数器的进位作为时模24计数器的计数允许信号;异步方式下,秒模60计数器的进位作为分模60计数器的时钟。分模60计数器的进位作为模24计数器的时钟,在设计时宜注意区分两种不同方式下进位的时序问题。

为了实现手动调整时间,在电路外部需要增加工作方式键 MODE、调时AH和调分单脉冲AM,当MODE为低电平时,电路正常计时;当MODE为高电平时,时和分计数器的时钟改由AH和AM提供:每按一次AH,小时增1,满23后回 0;每按一次AM ,分增1,满59后回0。因此电路的外部信号应包括:

输入:秒脉冲、工作模式 MODE、调时单脉冲 AH 和调分单脉冲 AM;

输出:秒、分、小时(24 h)的数码管显示.

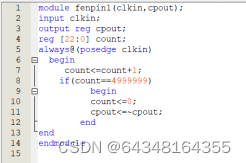

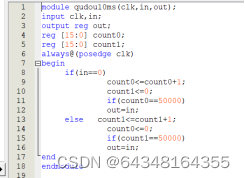

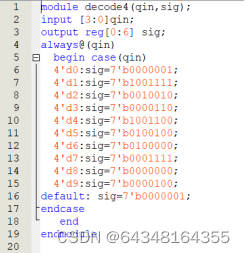

4.实验代码:

5. 实验总结:

在进行Verilog编写的程序时,要注意中英文状态下的符号不同,容易引起错误,编译文件时要先设为顶层,再进行编译,不然会出错,在选择数码管时,注意输出的有效为低电平,所以使用共阳数码管。在之前的都是用原理图形式的设计,这次我使用了模块例化,加深了HDL语言的理解。

最后

以上就是小巧大侠最近收集整理的关于EDA数字钟设计的全部内容,更多相关EDA数字钟设计内容请搜索靠谱客的其他文章。

发表评论 取消回复