数字电子时钟设计与实现

- 设计要求

- 设计实现

- 系统概述

- 单元电路设计

- 555 定时器

- 计数电路

- 显示电路

设计要求

1.采用12小时的计时方式。

2.四位数码管显示时、分,小时和分钟间的小数点以1Hz的频率闪烁表示秒。

3.具有快速校时和校分的功能。

设计实现

系统概述

首先,思考时钟的工作方式,六十秒进一位,六十分进一位,十二个小时归零。因为是要通过产生秒脉冲,显示时与分,所以第一应该思考如何产生秒脉冲。可以通过555 定时器外接RC元件构成多谐振荡电路产生秒脉冲。在秒脉冲下,如何通过计数器,实现进位,60s进1min, 60min进1h。 1;考虑的芯片有74ls160、74ls161,两种芯片都能实现功能,但是考虑到电路线路和焊接难度,首选74ls160。因为74ls160是十进制计数器,要构成两个六十进制和一个十二进制,需要六片74ls160芯片。然后通过译码器和数码管来显示时和分,而数码管只能显示0-9,构成的六十进制所以74ls160芯片为6*10,而74ls160为10进制,两片74ls160用整体置数法构成12进制。

单元电路设计

555 定时器

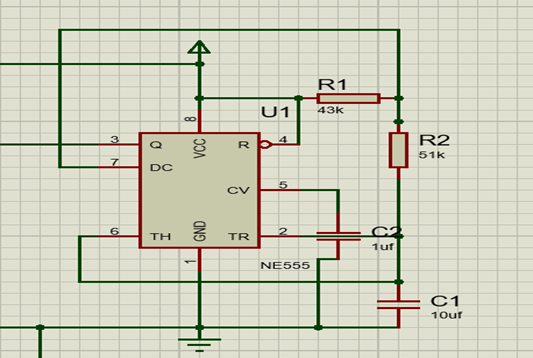

由555 定时器构成的多谐振荡器由电阻R1、R2,电容C1 以及旁路电容C2等组成。其输出频率:f=1/(R1+2R2)Cln2当f=1Hz 时,若选C 为10μF 的电解电容,取ln2=0.69,R1+2R2=144.9275kΩ。令R1=43kΩ,R2=51kΩ。 可得到频率为0.9995HZ的脉冲。

计数电路

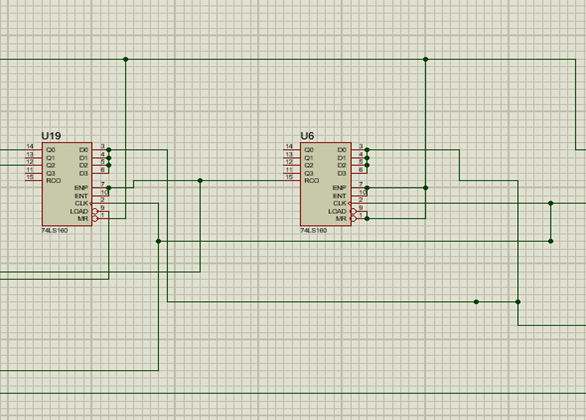

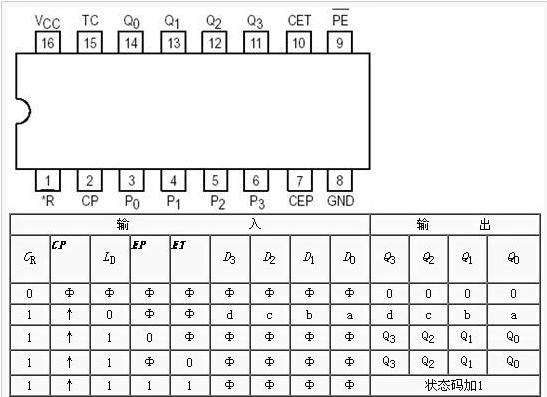

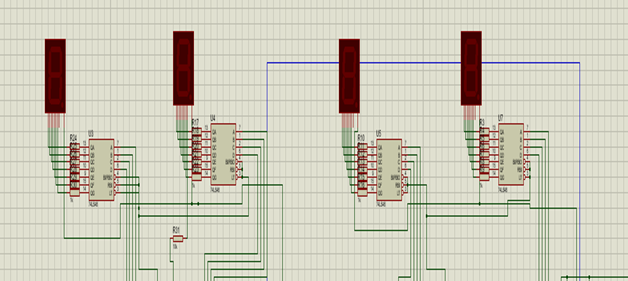

计数器用六片74ls160芯片构成,用于表示时钟的秒、分、时的个位和十位。运用整体置零法,六十秒归零,六十分归零,十二小时归零。采用共CLK,RD’恒接高电平;因为74ls160为十进制,在秒的两个74ls160中,个位是0-9,十位是0-5,所以,个位的进位输出接上十位的ENP,ENT端。没有进位信号时,十位上的74ls160为保持状态,来十个信号进一位,当计数器达到59时应该进一位并置零。所以,应将十位上的74ls160上的Q2、Q0和个位的进位输出端与非接入十位上的LD’端(其中LD’为预置数),实现置零功能,所以十位上的D0、D1、D2、D3应接地;因为74ls160为十进制,所以个位上的74ls160不用复位。

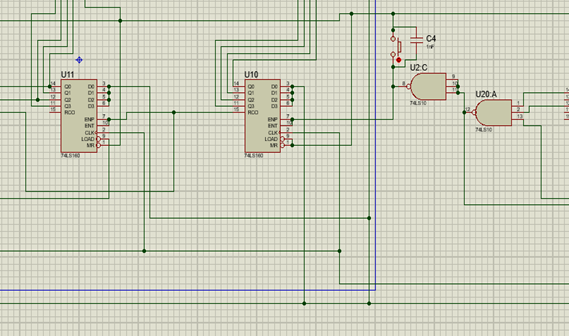

与非后的值再与非(这个也采用三输入与非门,可减少芯片数量)接入分的个位的ENP,ENT,原理和接法与秒上面相同。用开关接高电平,并联一个电容,接上分个位的ENP、ENT端,按下开关,相当于秒给了一个进位,起到快速校分。

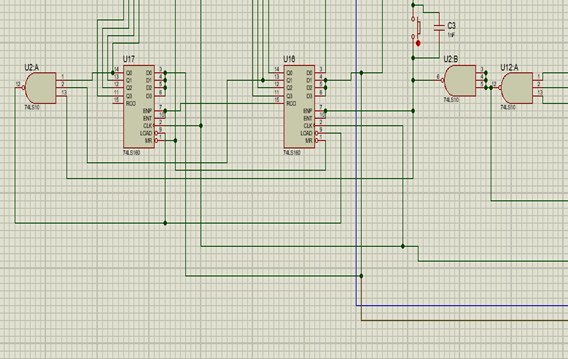

在时上,要构成12进制数,为1-12;采用整体置数法,将时上的十位上的Q0、个位上的Q1和分上的进位输出一起与非输出接上两个74ls160的LD’端,十位上的Q0、Q1、Q2、Q3接地,个位上的Q0接高电平、Q1、Q2、Q3接地,构成12进制。用开关接高电平,并联一个电容,接上分个位的ENP、ENT端,按下开关,相当于分给了一个进位,起到快速校时。

74ls160引脚图与真值表

显示电路

译码器的ABCD端与74ls160的Q0Q1Q2Q3相连接,abcdefg接数码管的abcdefg端,时上的个位上的数码管DP端接上555产生的时钟脉冲, 分钟间的小数点以1Hz的频率闪烁表示秒。

扫码关注公众号“嵌入式小学生”,发送“数字时钟”,获取工程文件下载链接。

最后

以上就是轻松豌豆最近收集整理的关于数字电子钟的设计与实现(纯数字电路,Proteus仿真)设计要求设计实现的全部内容,更多相关数字电子钟内容请搜索靠谱客的其他文章。

发表评论 取消回复