Verilog – 序列发生器的设计

产生序列信号11010111至少需要几级触发器?

思路1 - 状态机实现

最容易想到的就是采用状态机,每个状态输出序列中的一位,发送完一组序列后回到开始状态继续循环。需要注意的是状态变量的位宽,由于题目要求采用最少的触发器,因此至少需要log2(序列长度)个状态,对于本题也就是3个触发器,输出逻辑可以采用always(*)纯组合逻辑实现。

思路2 - 移位寄存器实现

序列的问题很多都可以用移位寄存器解决,只是移位寄存器方案可能会消耗较多的寄存器资源。

对于本题,如果规定了模块只有三个端口:

module seq_gen(

input clk,

input rst_n,

output reg seq );

那么需要在初始化的时候将移位寄存器值初始化为目标序列,或者有一个输入序列的接口,那就可以在初始化时将序列填入移位寄存器中。代码如下:

module seq_gen(

input clk,

input rst_n,

output seq );

reg [7:0]out_seq;

always@(posedge clk or negedge rst_n)

if(!rst_n) out_seq <= 8'b11010111;

else out_seq <= {out_seq[6:0],out_seq[7]};

assign seq = out_seq[7];

移位寄存器版本至少需要序列长度个寄存器,也就是8个。

思路3 – 计数器+组合逻辑

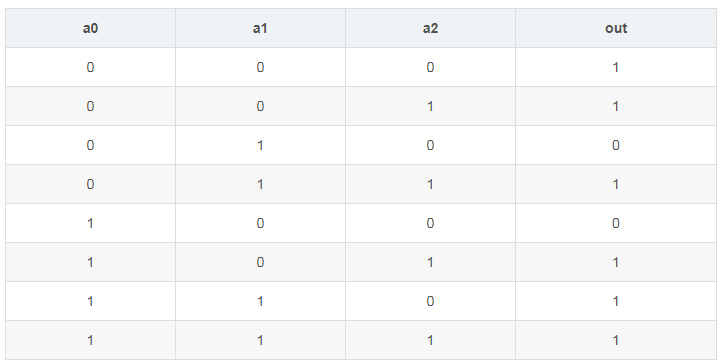

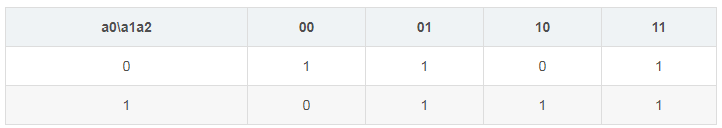

其实最上面的状态机版本就可以理解为计数器+组合逻辑的方法,因为状态变量相当于一个计数器。因此状态机版本的好处在于不需要考虑输出的组合逻辑怎么搭,直接case无脑就好了。而如果真的要自己手搭输出的组合逻辑呢?其实也不难,画个真值表就搞定了:

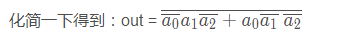

对应的卡诺图:

因此代码中只要有一个不断累加的3位计数器,配合上输出的组合逻辑表达式即可。

在之前的文章中也提到,如果计数器级数为N, 则环形计数器可以代表的状态数为N, 扭环形计数器为2N,线性移位反馈寄存器表示的状态数为2^N-1,所以本题没办法使用N=3的上述计数器。

参考:https://blog.csdn.net/darknessdarkness/article/details/106884392

最后

以上就是落寞烧鹅最近收集整理的关于序列发生器的设计的全部内容,更多相关序列发生器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复