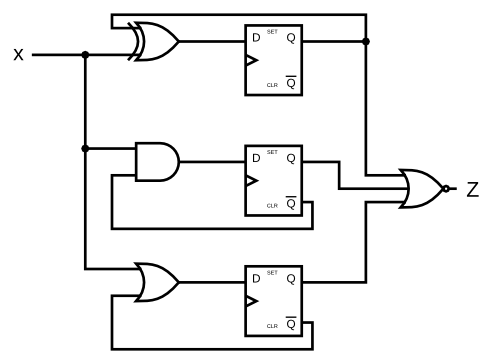

Given the finite state machine circuit as shown, assume that the D flip-flops are initially reset to zero before the machine begins.

Build this circuit.

开始的时候置0,所以一开始所有的Q都得是0;

这个地方放写完之后有个疑惑,就是w1、w2、w3是不是定义成reg类型会更好(reg类型是通过的) ,但是定义成wire类型也是通过了的:

module top_module (

input clk,

input x,

output z

);

wire w1,w2,w3; // 是不是定义成reg类型更好

initial begin

w1 = 0;

w2 = 0;

w3 = 0;

end

always @(posedge clk)begin

w1 = x^w1;

w2 = x&~w2;

w3 = x|~w3;

end

assign z = ~(w1|w2|w3);

endmodule

最后

以上就是忧心金针菇最近收集整理的关于【HDLBits刷题】Exams/ece241 2014 q4.的全部内容,更多相关【HDLBits刷题】Exams/ece241内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复