原理图上的关于EMC的落地体现

- 一、元器件的选型

- 二、原理图上的EMC体现在哪里?

- 1.芯片电源管脚滤波去耦:

- 2.时钟电路滤波设计

- 3.低速电路滤波抗干扰设计

- 4.通讯接口电路的防护滤波

- 5.系统输入电源端口电路的防护滤波

- 6.系统接地的定义

- 7.芯片软件功能的审查

一、元器件的选型

原理图最初设计涉及到选型元器件方面:

- 元器件选型

不仅仅功能需要满足要求,还需要考虑其它细节参数在不同应力下的反应,封装的不同也会产生不同的变化。

- 元器件替代

常常因为成本原因进行器件替代,除了要考虑功能参数相同时也要考虑系统参数。

二、原理图上的EMC体现在哪里?

按照《电磁兼容设计总体思路》总体思路中的三要素:目标 + 工具 + 方法论

关于产品原理图的电磁兼容的目标是什么呢?是为了在原理设计阶段,运用可靠设计手段进行最优化设计,避免或降低后续出现重大EMC问题的可能性。使用的工具一般就是EDA工具。具体的方法流程如下:

- 熟悉原理图的逻辑框图;

- 通过框图理解产品原理图模块的构造;

- 电磁兼容设计方案落地确认;

- 关键电路的电磁兼容方案落地在原理图上的设计体现,此处的设计体现,体现在PCB布局布线阶段的可操作可执行。

说了宏观的方法流程,那么有什么具体的、可落地的细节呢?

-

芯片电源管脚滤波去耦

-

时钟电路滤波设计

-

低速电路滤波抗干扰设计

-

通讯接口电路的防护滤波

-

系统输入电源端口电路的防护滤波

-

系统接地的定义

-

芯片软件功能的审查

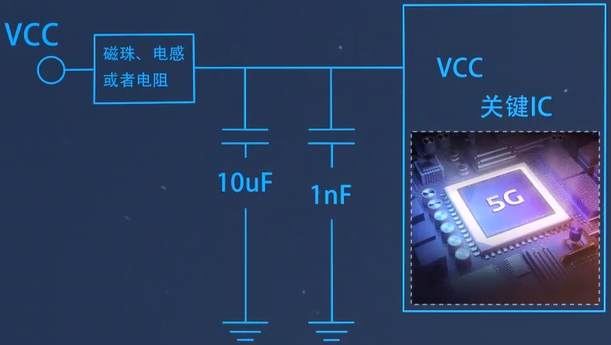

1.芯片电源管脚滤波去耦:

一般来说,所有芯片的电源关键都需要滤波去耦电容,去耦电容具有两个作用:

- 提供一个邻近IC的电荷源,使得IC切换开关时,去耦电容可以通过一个低阻抗通路提供所需的瞬态电流;

- 提供一个在电源和接地线间的低交流阻抗路径,这将有效地最小化由IC回流到电源/地系统的噪声(可以理解为减少了回流的环路面积和电感,从而减小了这方面的噪声,也因此在PCB布局时,去耦电容离对应管脚越近越好)。

有条件的可以采用电源完整性分析分析来指导电容的使用数量以及容值大小,一般参考芯片的datasheet中的推荐设计也可以,常见的方式就是如下图所示,采用大一点容值的储能电容和高频小电容配合使用。

电容封装越小越好,从EMC的角度来看,容值0.1uF和0.01uF的差异不大,重点关注的是封装、布局以及走线带来的电感。对于同一芯片的相同电源电压的滤波电容建议选择相同容值的高频小电容,可以避免不同容值之间,可能会产生的反谐振现象,从而导致滤波去耦性能的变化。

噪声比较敏感或者产生噪声比较大的芯片,例如敏感芯片(模拟、射频、接口驱动、音频等)以及噪声强的芯片(时钟、高速数字、DCDC开关电源、内存芯片SDRAM/DDR、CPU、高速FPGA等)需要采用电感或者磁珠,甚至小电阻进行滤波隔离设计。如何选择电感、磁珠或者电阻这些具体器件呢?

答:有条件的可以获得器件的S参数模型,采用滤波器的一些工具软件进行仿真从而指导选择器件。当然,也可以靠经验值来参考指导选择。

2.时钟电路滤波设计

时钟主要关注三点:

- 时钟晶振/BUFFER的输入电源的滤波去耦;

- 时钟信号输出的阻抗匹配(目的是为了滤除高速谐波);

- 时钟电路接地的定义。

关于第一点可参考上面所述的滤波去耦的方法。第二点可以串联一个电阻或者串阻后再并联一个小电容,电阻电容的值有条件的话可以采用信号完整性仿真分析,也可以先预留焊盘,后续先贴0Ω电阻,封装推荐0603或者0402即可。经验值可参考:电阻一般10Ω(33Ω或者47Ω),电容一般2.2~10pF。关于接地一般视具体器件的datasheet要求即可。

3.低速电路滤波抗干扰设计

对低速电路(例如LED灯信号、复位电路等)抗干扰设计的考虑主要体现在抑制干扰脉冲(例如静电ESD等),有两种方法:

- 使用RC电路(串联电阻限流,并联电容吸收瞬态的脉冲);

- TVS管(并联,结电容小的<1000pF,如果容性对具体电路无影响,则不需要考虑结电容)。

4.通讯接口电路的防护滤波

通讯接口电路有很多,例如USB接口、以太网接口、RS232/485、HDMI接口等。首先针对具体端口的防护滤波设计,我们需要知道这个产品具体应用场景的电磁环境。

是户外呢还是户内呢?附近是否有高压线呢?根据具体电磁环境的定义,就有了电磁兼容设计规格指标。例如:

- 产品应用于室内,布线不超过三米:那么端口的防护设计能力满足ESD就可以了;

- 产品应用于室外,或布线较长甚至于大功率切换的电源走线并行:这时候仅仅考虑ESD就不够了,还需要考虑浪涌防护设计。

具体的接口,需要根据具体接口的速率、工作速率和信号完整性选择适合的滤波防护方案。

5.系统输入电源端口电路的防护滤波

防护的思路类似于通讯接口电路的防护滤波,需要依据供电系统以及其输入的电磁环境来确定浪涌规格,制定防护和滤波设计方案。

6.系统接地的定义

关于系统接地,可以参考《详说EMC设计的三大出发点》中关于接地的内容。

7.芯片软件功能的审查

有些芯片,可以通过调制软件的设置来协助解决EMC的问题,那么我们在原理图检视阶段就需要评审这个功能,是否可在后续的落地执行时,有预留的硬件支撑,例如:

- 时钟或PICE展频功能打开与否是否需要硬件设计上的支撑;

- 数字滤波技术是否需要硬件电路支撑;

- 电源芯片的抖频技术是否需要硬件电路预设支撑等。

分享微信公众号『设计至纯』,查看更多原创内容,O(∩_∩)O一键三连????、分享????、收藏、点赞、支持????????。 ^ o ^ 您的点赞、评论和关注,是小小编继续创作的不懈动力。 ????

最后

以上就是忧心帽子最近收集整理的关于【EMC电磁兼容】02.04——原理图的实战落地细节的全部内容,更多相关【EMC电磁兼容】02.04——原理图内容请搜索靠谱客的其他文章。

发表评论 取消回复