一、OV7725的PCLK的改变和以下几个寄存器有关:

1:OX0D(COM4);

------------------------------------------------------------------------------------------------------------------

0X0D COM4 41 common control 4

Bit[7:6]: PLL frequency control

00:Bypass PLL

01:PLL 4X

10:PLL 6X

11:PLL 8X

Bit[5:4]: AEC evaluate windows

00: Full windows

01: 1/2 windows

10: 1/4 windows

11: Low 2/3 windows

Bit[3:0]: Reserved

------------------------------------------------------------------------------------------------------------------

2:0X11(CLKRC);

------------------------------------------------------------------------------------------------------------------

0X11 CLKRC 80 internal Clock

Bit[7]: Reseved

Bit[6]: Use external clock directly (no clock pre_scale available)

Bit[5:0]: internal clock pre_scalar

F(internal clock) = F(input clock)/(Bit[5:0]+1)/2

. Range : [0 0000] to [1 1111]

------------------------------------------------------------------------------------------------------------------

举个栗子:

Frame Rate Adjustment for 24Mhz input clock

30 fps, PCLK = 24Mhz

SCCB_salve_Address = 0x42;

write_SCCB(0x11, 0x01);

write_SCCB(0x0d, 0x41);

write_SCCB(0x2a, 0x00);

write_SCCB(0x2b, 0x00);

write_SCCB(0x33, 0x00);

write_SCCB(0x34, 0x00);

write_SCCB(0x2d, 0x00);

write_SCCB(0x2e, 0x00);

write_SCCB(0x0e, 0x65);

15 fps, PCLK = 12Mhz

SCCB_salve_Address = 0x42;

write_SCCB(0x11, 0x03);

write_SCCB(0x0d, 0x41);

write_SCCB(0x2a, 0x00);

write_SCCB(0x2b, 0x00);

write_SCCB(0x33, 0x00);

write_SCCB(0x34, 0x00);

write_SCCB(0x2d, 0x00);

write_SCCB(0x2e, 0x00);

write_SCCB(0x0e, 0x65);

第一个:

如上:输入时钟为24MHZ;0X0D为0x41,说明PCLK是输入时钟的4倍频;0X11为0X01,根据函数式:F(internal clock) = F(input clock)/(Bit[5:0]+1)/2,得到内部时钟为:F(internal clock) =24/2/2=6MHZ;得到PCLK=4*6=24MHZ,帧率是30fps

第二个:

如上:输入时钟为24MHZ;0X0D为0x41,说明PCLK是输入时钟的4倍频;0X11为0X03,根据函数式:F(internal clock) = F(input clock)/(Bit[5:0]+1)/2,得到内部时钟为:F(internal clock) =24/4/2=3MHZ;得到PCLK=4*3=12MHZ,帧率是15fps(帧率变小的原因是PCLK的频率降低了)

二、OV7725的帧率和PCLK的频率及0X33及0x34有关,0x33配置的是低8位,0x34配置的是高8位,这里是说增加的假的行,即没有用的行,这样帧率就会下降;

同时还和0x2a及0x2b有关,这里说的是加入的假的列,即没用的列,这样的话帧率也会下降;

---------------------------------------------------------------------------------------------------------

0X33 DM_LNL 00 RW Dummy Row Low 8bit

---------------------------------------------------------------------------------------------------------

-------------------------------------------------------------------------------------------------------

0x34 DM_LNH 00 RW Dummy Row High 8bit

-------------------------------------------------------------------------------------------------------

-------------------------------------------------------------------------------------------------------

0x2a EXHCH 00 RW Dummy pixel insert MSB

Bit[7:4] :4MSB for dummy pixel insert in horizontal direction

Bit[3]:Reserved;

Bit[2]:vertical data outup size LSB

Bit[1:0]:Horizontal data outup size 2LSBs

-----------------------------------------------------------------------------------------------------------------------

----------------------------------------------------------------------------------------------------------------------

0x2b EXHCL 00 RW Dummy pixel insert LSB

8LSB for dummy pixel insert in horizontal direction

--------------------------------------------------------------------------------------------------------------------------------

举个栗子:

Frame Rate Adjustment for 24Mhz input clock

30 fps, PCLK = 24Mhz

SCCB_salve_Address = 0x42;

write_SCCB(0x11, 0x01);

write_SCCB(0x0d, 0x41);

write_SCCB(0x2a, 0x00);

write_SCCB(0x2b, 0x00);

write_SCCB(0x33, 0x00);

write_SCCB(0x34, 0x00);

write_SCCB(0x2d, 0x00);

write_SCCB(0x2e, 0x00);

write_SCCB(0x0e, 0x65);

25fps, PCLK = 24Mhz

SCCB_salve_Address = 0x42;

write_SCCB(0x11, 0x01);

write_SCCB(0x0d, 0x41);

write_SCCB(0x2a, 0x00);

write_SCCB(0x2b, 0x00);

write_SCCB(0x33, 0x66);

write_SCCB(0x34, 0x00);

write_SCCB(0x2d, 0x00);

write_SCCB(0x2e, 0x00);

write_SCCB(0x0e, 0x65);

这两端代码的输入clk都是24MHZ,输出PCLK相同都是24MHZ,但frame rate一个是30fps,一个为25fps,程序中只有0X33不同,如何通过将0X33设置为0X66,从而将30fps变为25fps。看下面的分析:

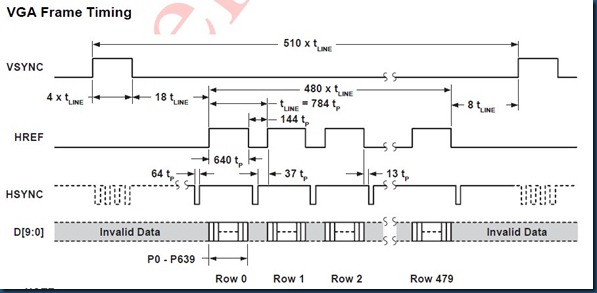

从图片中我们可以看到一个VSYNC有510个t(LINE),所以30fps表示有30*510*t(LINE),结合上面对于0X33的分析,因为都 是24MHZ,所以30fps和25fps两个时间相同。故在这510个LINE中插入102个(0X66)LINE,总的时间才会相同。 30*510*t(LINE)=25*(510+102)*t(LINE).

当然帧率会随着PCLK的变化而变化,当PCLK变为12MHZ时,帧率也就减为15fps了。

最后

以上就是敏感豆芽最近收集整理的关于OV7725的帧率和PCLK寄存器设置的全部内容,更多相关OV7725内容请搜索靠谱客的其他文章。

发表评论 取消回复