三、玄铁c910中的向量指令集

对于矢量浮点指令,只有矢量浮点扩位转换指令和矢量浮点缩位转换指令可在元素位宽为 8 时正常执行,其他矢量浮点指令必须在元素位宽为 16/32/64 时执行,否则产生非法指令异常;矢量整型指令可支持元素位宽为 8/16/32/64 的计算。

每条指令位宽为 32 位,指令按英文字母顺序排列。

缩写含义如下:

- VLEN:矢量寄存器位宽,C910 中为 128。

2. VLMAX:当前矢量寄存器组最大元素个数,VLMAX=VLEN/SEW*LMUL。

玄铁c910中向量指令集主要分为三类,共394条,具体为:

• 矢量整型指令

• 矢量浮点指令

• 矢量加载存储指令

按照具体功能分,有如下:

- 矢量控制指令

- 矢量 MISC 指令

- 矢量缩减指令

- 矢量乘法乘累加指令

- 矢量移位指令

- 矢量整型加减法指令

- 矢量整型比较指令

- 矢量整型最大值/最小值指令

- 矢量整型除法/取余指令

- 矢量元素排序操作指令

- 矢量整型定点加减法指令

- 浮点运算指令

- 矢量浮点比较指令

- 浮点传送指令

- 浮点数据类型转换指令

- 浮点缩减指令

- 浮点分类指令

- 矢量加载存储指令

- 矢量原子指令

- 矢量 SEGMENT 指令

四、 github上的向量协处理器

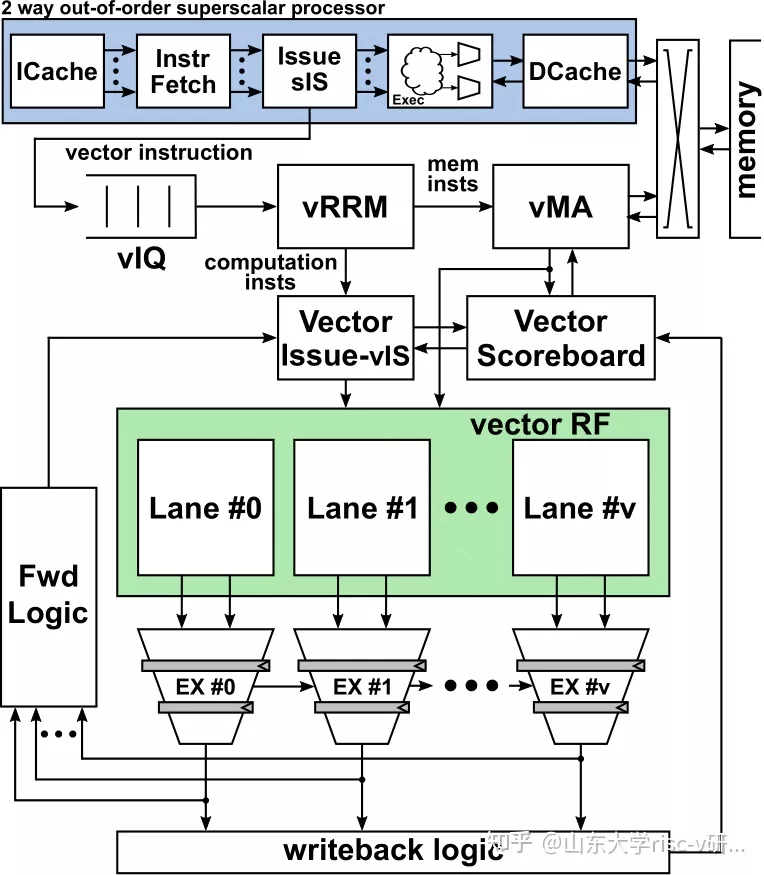

1、希腊人写的向量协处理器 挂在双发射处理器上

上传者:

1、模块介绍

| 模块名 | 详情 |

|---|---|

| vrrm | 寄存器映射,分配 |

| Vis | 基于计分板,发射级, |

| Vex | 执行阶段,包含矢量通道、环绕逻辑和连接。 |

| Vex_pipe | 执行通道,包括多个执行单元 |

| Vmu | 向量存储单元 |

| Vmu_ld_eng | Load |

| Vmu_St_eng | Store |

| Vmu_tp_eng | 数据预取 |

2、包含的指令:

| Memory Operations | Integer Operations |

|:-------------------:|:-------------------:|

| vfld |vadd |

| vflh |vaddi |

| vflsd |vaddw |

| vflsh |vaddiw |

| vflsw |vsub |

| vflw |vsubw |

| vflxd |vmul |

| vflxh |vmulh |

| vflxw |vmulhsu |

| vlb |vmulhu |

| vlbu |vmulwdn |

| vld |vdiv |

| vlh |vdivu |

| vlhu |vrem |

| vlsb |vremu |

| vlsbu |vsll |

| vlsd |vslli |

| vlsw |vsra |

| vlswu |vsrai |

| vlw |vsrl |

| vlwu |vsrli |

| vlxb |vand |

| vlxbu |vandi |

| vlxd |vor |

| vlxh |vori |

| vlxh |vxor |

| vlxhu |vxori |

| vlxhu |vseq |

| vlxw |vslt |

| vlxwu |vsltu |

| vsb |vrelu |

| vsd |vstep |

| vsh |vbrelu |

| vssb |vprelu |

| vssd |vradd |

| vssh |vrand |

| vssw |vror |

| vsw |vrxor |

| vsxb | |

| vsxd | |

| vsxh | |

| vsxub | |

| vsxud | |

| vsxuh | |

| vsxuw | |

| vsxw | |

| *vtplcfg* | |

| *vtpl* | |其中,vtplcfg、vtpl为自定义指令

3、架构图

- 代码

| Vstruct.sv | 结构体文件,打包信号用 |

|---|---|

| Vrrm.sv | 寄存器重新映射 |

| Vrat.sv | 寄存器别名表 |

| Vis.sv | 向量指令发射级 |

| Vrf.sv | 向量寄存器文件 |

| VEX.SV | 执行级的顶层 |

| Vex_pipe.sv | 每一lane的流水线 |

| Vmu.Sv | 向量内存单元 |

| vmu_ld_eng | Load单元 |

| vmu_st_eng | Store单元 |

| vmu_tp_eng | 预取单元 |

Vector lane

并行计算机体系结构 #1 向量处理器 - 知乎

将阵列架构中的ALU替换为向量处理单元,在计算每一个元素时也进行流水线。现代向量扩展都会在硬件中自动实现这种形式。在这种架构中,每一个流水线向量单元也被称为“vector lane”。SIMD宽度就等于vector lane的数量。

- vrrm=Register Remmaping

(1)指令种类

- 配置指令

- 内存指令

- 数据预取配置指令

- 数据预取指令

- 加载指令

(2)指令流输入

包括如下信息:

Src1,src2 索引,dst索引

32位的src1数据和32位的src2数据,7位的microop

(3)指令流输出

Src1,src2 索引,dst索引

新增iszero信号:store指令和扩展指令不写回dst

Remap在rat模块中完成

2、vrat=Vector Register Aliasing Table

用32个表项暂存寄存器信息,看起来是向量物理寄存器堆,一写三读 ,写入指令信息,

3、vis

4、vrf

5、vex:

执行级的每个pipe 包括整型和浮点两个ALU

6、vmu

五、github上的ara

1、22nm 1.7Ghz 16路执行

本文章仅供学习交流,如有引用请标注出处。

最后

以上就是紧张蜜蜂最近收集整理的关于RISC-V 向量指令集研究(二)的全部内容,更多相关RISC-V内容请搜索靠谱客的其他文章。

发表评论 取消回复