一、基本概念

(1)锁存器

1. 锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

分为普通锁存器和门控锁存器:

2.普通锁存器无控制信号,输出状态始终直接由输入决定。

3.门控锁存器在控制信号无效时,输出保持不变,不随输入变换;当控制信号有效时,输出由输入决定,跟随输入变化。

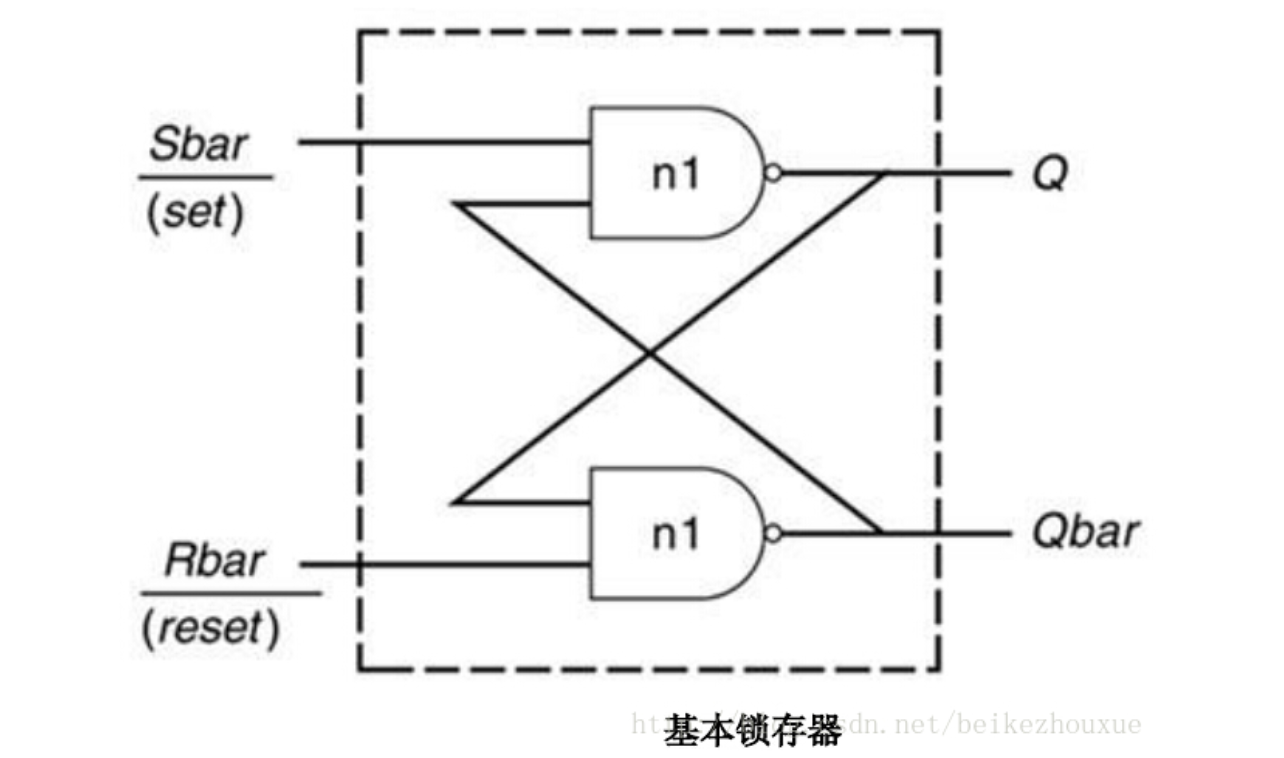

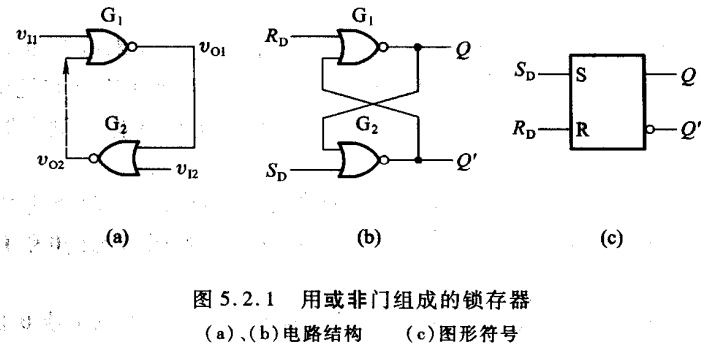

4.SR锁存器(基本锁存器):

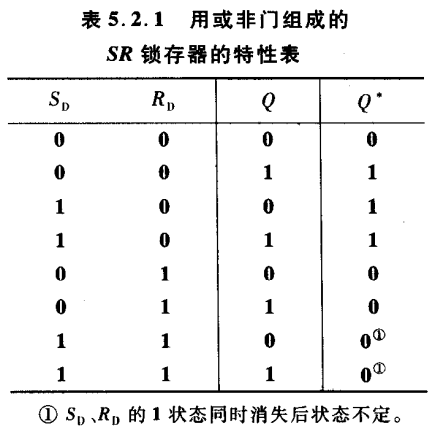

由两个或非门或者两个与非门组成,电路结构、图形符号和特性表如下所示。

此时,输出状态(次态)与输入状态、锁存器初态都有关。

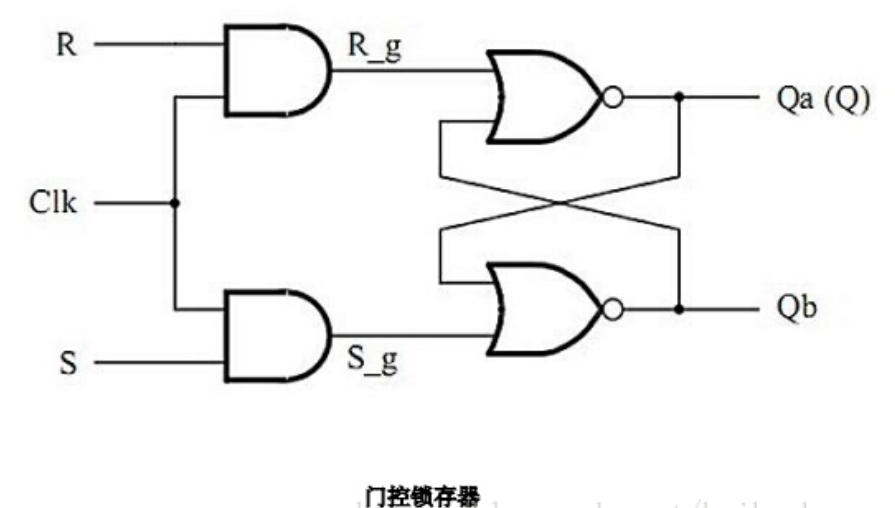

电平触发SR触发器(门控SR锁存器):

当CLK=0时(无效),输出状态(次态)保持不变;只有当CLK=1时(有效),输出状态才随输入、初态的不同而改变,且与SR锁存器的特性一样。

当门控锁存器的控制信号有效时,锁存器就变成了一个组合电路,若此时输入信号发生多次变化,输出状态也可能发生多次变化,这一现象称为锁存器的空翻。此时,时序逻辑电路的模型就等效为两个各组合电路互为反馈的反馈系统,因此,系统有可能会因为瞬态特性不稳定而产生振荡现象,抗干扰能力差。

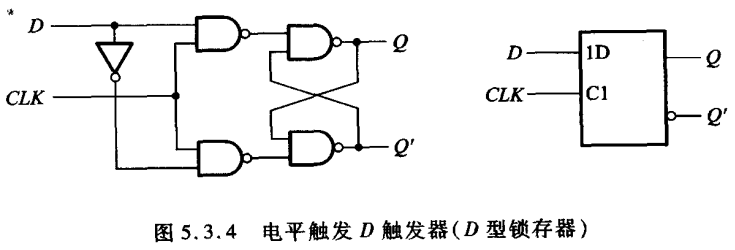

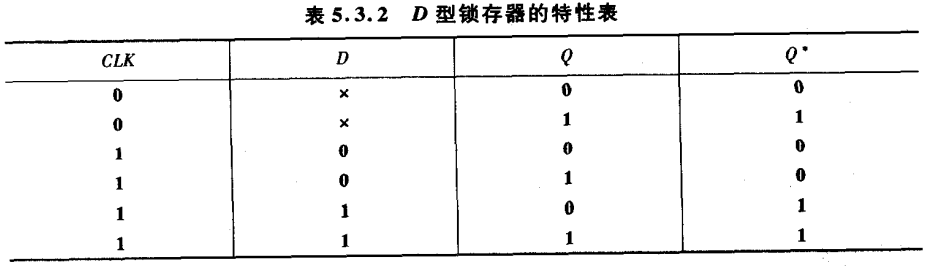

5.电平触发D触发器(D型锁存器):

在CLK的有效电平期间,输出状态始终随输入状态变化,输出与输入状态保持相同,所以这个电路又叫“透明的D型锁存器”。

6.特点:

- 正是因为门控锁存器在控制信号有效的期间内,都可以接收输入信号, 所以,激励信号的任何变化, 都将直接引起锁存器输出状态的改变。这时输入信号若发生多次变化,输出状态也可能发生多次变化,这一现象称为锁存器的空翻。

- 其次,当门控锁存器的控制信号有效时,锁存器就变成了一个组合电路,时序逻辑电

路的模型就等效为两个各组合电路互为反馈的反馈系统,因此,系统有可能会因为瞬态特性

不稳定而产生振荡现象。 - 对毛刺敏感(使能信号有效电平时,输出状态可能随输入多次变化,产生空翻,对下一级电路很危险),不能异步复位,因此在上电后处于不确定的状态。

- 锁存器会使静态时序分析变得非常复杂,不具备可重用性。(首先,锁存器没有时钟参与信号传递,无法做STA;其次,综合工具会将latch优化掉,造成前后仿真结果不一致)

- 在FPGA中基本的单元是由查找表和触发器组成的,若生成锁存器反而需要更多的资源。根据锁存器的特点可以看出,在电路设计中,要对锁存器特别谨慎,如果设计经过综合后产生出和设计意图不一致的锁存器,则将导致设计错误,包括仿真和综合。因此,在设计中需要避免产生意想不到的锁存器。如果组合逻辑的语句完全不使用 always 语句块,就可以保证综合器不会综合出锁存器。

- 但如果锁存器和触发器两者都由与非门搭建的话,锁存器耗用的逻辑资源要比D触发器少(D触发器需要12个MOS管,锁存器只需6个MOS管),锁存器的集成度更高,所以在的ASIC设计中会用到锁存器。但锁存器对毛刺敏感,无异步复位端,不能让芯片在上电时处在确定的状态;另外,锁存器会使静态时序分析变得很复杂,不利于设计的可重用。所以,在ASIC设计中,除了CPU这高速电路,或者RAM这种对面积很敏感的电路,一般不提倡用锁存器。

- 在 PLD 芯片中,基本的单元是由查找表和触发器组成的,若生成锁存器反而需要更多的资源。根据锁存器的特点可以看出,在电路设计中,要对锁存器特别谨慎,如果设计经过综合后产生出和设计意图不一致的锁存器,则将导致设计错误,包括仿真和综合。因此,在设计中需要避免产生意想不到的锁存器。

7.锁存器(Latch)的出现及解决办法

在基于always的组合逻辑描述语句中容易综合出锁存器的地方:

(1)在赋值表达式右边参与赋值的信号未在always@(敏感电平列表)中列出完整,生成透明锁存器;

(2)if语句的使用中缺少else语句(前提不是始终时钟触发);

(3)case语句没有给出全部情况。

举例说明:

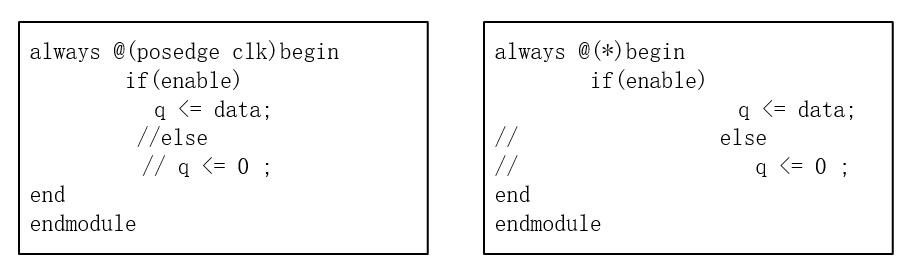

(1)时序电路中if...else不完整不会生出latch,只会生成触发器,而组合逻辑就会产生latch:

左上的电路是时序逻辑,生成触发器,而触发器是有使能端(enable)的,使能端无效时就可以保存数据,无需锁存器。右上的电路是组合逻辑,在enable为低电平时,输出q要保持不变,而组合逻辑没有存储元件,只能生成锁存器来保持数据。所以在时序逻辑中,不完整的 if…else… 结构并不会生成锁存器,而组合逻辑中不完整的 if…else… 结构就会生成锁存器。为了避免我们设计的组合逻辑中出现不想要的锁存器,在使用 if…else… 结构时一定要写完整。

解决方法:

①将锁存器改为带使能的触发器(变为时序电路);

②给输出变量赋初始值;

③补全if...else语句。

如果组合逻辑的语句完全不使用 always 语句块,就可以保证综合器不会综合出锁存器,

例如:assign a = din ? x : y;上述语句不需要保持信号 a 的前一个状态,因此肯定不会产生锁存器。

(

感悟:

①在always模块内被赋值的每一个信号都必须定义成reg型,但不一定就会生成寄存器。

②组合逻辑一般使用assign语句。

③当组合逻辑使用always模块时,@(*)或敏感信号列表需写完整,都属于电平触发。另外,if...else以及case情况(必要时加上default)需写完整,或者输出状态赋初始值。

④时序逻辑中“always @(posedge clk)”属于同步时钟,而“always @(posedge clk,negedge rst)”属于同步时钟,异步复位。

⑤“=”阻塞赋值表示组合逻辑,“<=”非阻塞赋值表示时序逻辑。

一般的设计规则是:在绝大多数设计中避免产生锁存器。它会让您设计的时序完蛋,并

且它的隐蔽性很强,非老手不能查出。锁存器最大的危害在于不能过滤毛刺 (使能信号有效

时,输出状态可能随输入多次变化,产生空翻) 。这对于下一级电路是极其危险的。所以,

只要能用 D 触发器的地方,就不用锁存器。

)

(2)触发器

触发器(Flip Flop,FF)是一种只能存储1个二进制位的存储单元,可以用作时序逻辑电路的记忆原件。

触发器(flip-flop)是边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内) 。

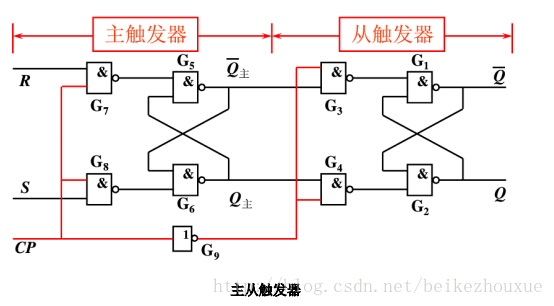

(钟控 D 触发器其实就是 D 锁存器,边沿 D 触发器才是真正的 D 触发器)触发器分为两种,一种是主从触发器和边沿触发器。主从触发器在时钟有效期内 (主触发器) 接收数据,在时钟边沿输出状态转换。

边沿触发器在时钟边沿期间, 触发器才接收数据并使输出状态转换。

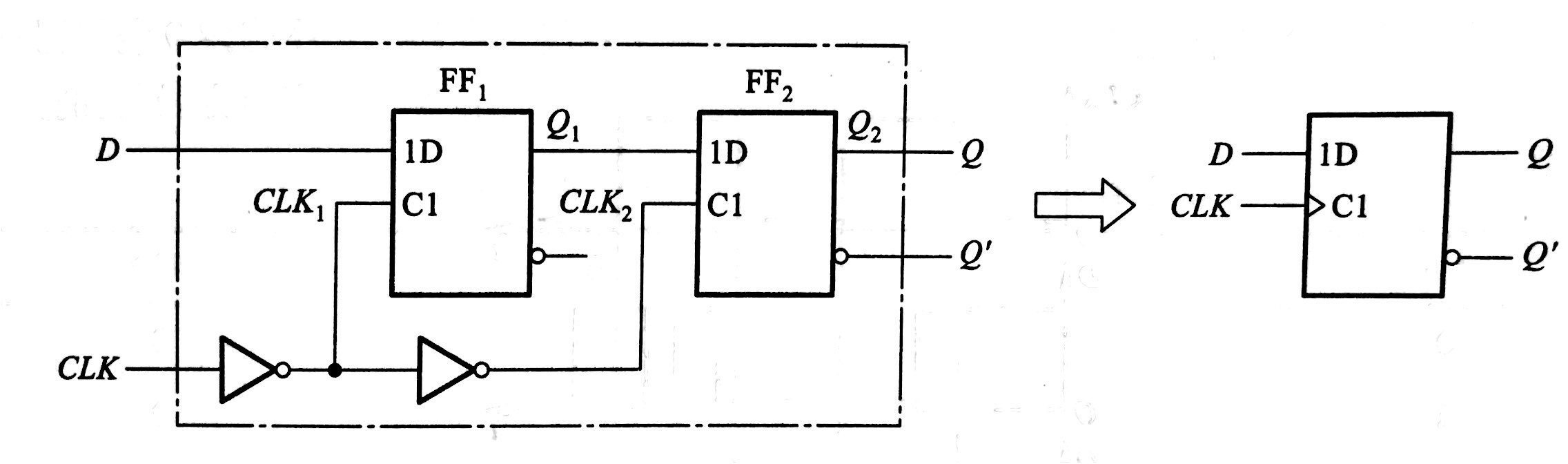

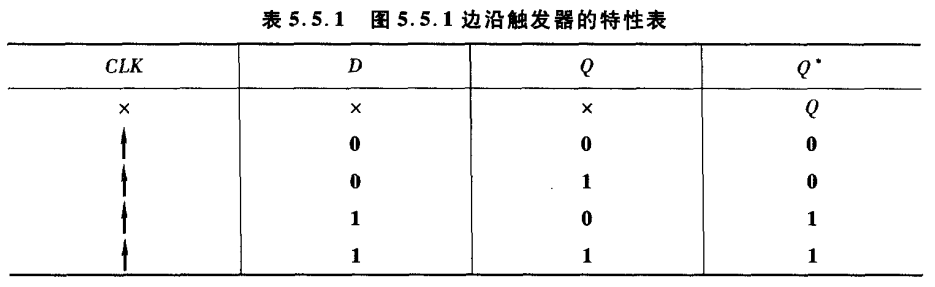

- 边沿触发D触发器:

由两个D型锁存器组成,次态仅取决时钟有效边沿到达时输入的逻辑状态,且值保持不变到下次触发到达时(保持n个时钟周期)。

电路抗干扰能力强,工作可靠性更高。

(3)寄存器

寄存器能够存寄一组二值代码,即由N个触发器组成。

用来暂时存放参与运算的数据和运算结果。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

寄存器与存储器的区别

现代的计算机主要包括三级存储,寄存器、内存储器和外存储器,存储数据的速率也依次递减。(外存储器不在本次讨论之中,姑且略过不讲)我们不妨将寄存器和 内存储器都抽象成一个大的数组,其中的每个元素都有一个字节(8位)大小,CPU寻址的时候就是以该元素为最小单位完成的。如前一个元素的地址是 0x1FFFFFF0的话,那么下一个元素的地址就是0x1FFFFFF1。我们可以理解为硬件构成上寄存器和内存储器也都是由一个8位大小的元器件线性 排列组成的,地址对应着上面讲到的数组中元素的地址。到这里也许你能明白我的意思了,抛开存储速率不谈,对面向软件开发的人来说寄存器和内存储器结构可以 看作是相同的,那它们有什么不同呢?

当然是存储速率不同了!先别骂街……速率只是表面现象,寄存器与内存本质的区别还是物理结构的不同,寄存器是有DFF(D触发器)构成的,它起的只是暂时存储数据的作用;内存储器有MOS门和TTL门两种构成,有ROM和RAM两种。ROM是由厂家固定地制造的,又分为掩膜ROM,PROM,EPROM,EEROM。有用门电路组成的ROM(由厂家写入信息)和用二极管或熔断丝构成的可由用户写入信息的PROM等.....RAM可分为DRAM和SRAM两种。前者是由电容构成的必须及时刷新,SRAM由MOS门构成不必刷新...... 从在计算机内部的放置位置上说,寄存器是在主板上离CPU最近并且速度最快。内存在计算机主机内,当时在计算机设计时,速度一直提不高,后来把内存放在计算机内速度才得以质的飞跃达到100M以上。内存速度快,容量小,价格高。外存可以取出,如光盘,磁盘价格便宜,但速度慢,用于存放大量数据。。它们之间的具体区别跳过不讲,我只想让你知道二者之间在寻址原理上都是相同的!

二、区别与联系

上述解释中已经阐述了三者的区别,现在将它们总结一下:

1.目前,主从触发器基本上已经很少见了,实际使用的大都是边沿触发器。

2.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把 n 个触发 器的时钟端口连接起来就能构成一个存储 n 位二进制码的寄存器。

3.从寄存数据的角度来讲,寄存器和锁存器的功能是相同的;它们的区别在于寄存器是同步时钟控制,而锁存器是电位信号控 制。

4.锁存器的工作原理:锁存器不同于触发器,锁存器在不锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓存器 一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。因此锁存器也称为透明锁存器,值得是不锁存是输出对 输入是透明的。

参考文章:https://blog.csdn.net/Jackiezhang1993/article/details/85005521

https://blog.csdn.net/beikezhouxue/article/details/40107955

https://www.eefocus.com/liuyuxue/blog/13-11/300280_d7008.html

https://blog.csdn.net/u011435712/article/details/42105563

最后

以上就是迷你服饰最近收集整理的关于触发器、锁存器、寄存器以及它们之间的区别的全部内容,更多相关触发器、锁存器、寄存器以及它们之间内容请搜索靠谱客的其他文章。

发表评论 取消回复