这是第一篇用Verilog的文章

沿正边沿触发的触发器,包括使能端en

Verilog描述如下

module d_ff(clk, in, en, out);

input clk, in, en;

output reg out;

always @(posedge clk)

if(!en)

out <= 0;

else

out <= in;

endmodule

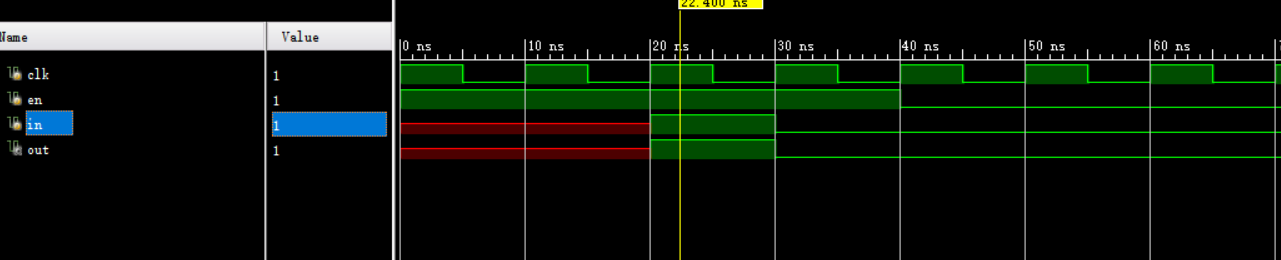

仿真如下

module d_ff_sim();

reg clk, en, in;

wire out;

d_ff u(clk, in, en, out); //这里一定要记着实例化

initial begin

clk = 1; en = 1;

//#10 clk = 1;

#10 en = 1;

#10 in = 1;

#10 in = 0;

#10 en = 0;

end

always //用always语句来模拟时钟变化

//begin

#5 clk = ~clk;

//end

endmodule

可以看出D触发器就是当时钟上升沿来临时,输出数据的值是此刻输入数据的值,并一直保持到下一个上升沿来临。

最后

以上就是沉静火车最近收集整理的关于D触发器(Verilog)的全部内容,更多相关D触发器(Verilog)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复