Circuits----sequential Logic

文章目录

- Circuits----sequential Logic

- 前言

- 一、shift registers(移位寄存器)

- 1.异步置零的移位寄存器

- 2.环形移位寄存器

- 二、算术移位寄存器

- 1题目

- 三、线性反馈移位寄存器(LFSR)

- 总结

前言

计算机中补码的形式存在,所以看补码的算术移位和逻辑移位

一、shift registers(移位寄存器)

对于逻辑移位,就是不考虑符号位,移位的结果只是数据所有的位数进行移位。

左移:低位补0

右移:高位补0

例:

01010101>>3=00001010

01101011<<3=01011000

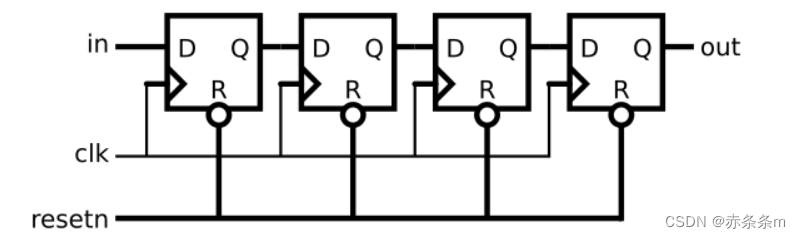

1.异步置零的移位寄存器

移位补0

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,//Data is loaded at high levels

input ena,//High levels shift data to the right

input [3:0] data,

output reg [3:0] q);

always@(posedge clk or posedge areset)begin

if(areset)

q <= 4'd0;

else if(load)

q <= data;

else if(ena)

q <= {1'b0,q[3:1]};//q <= q[3:1]; Use vector part select to express a shift.

else

q <= q;

end

endmodule

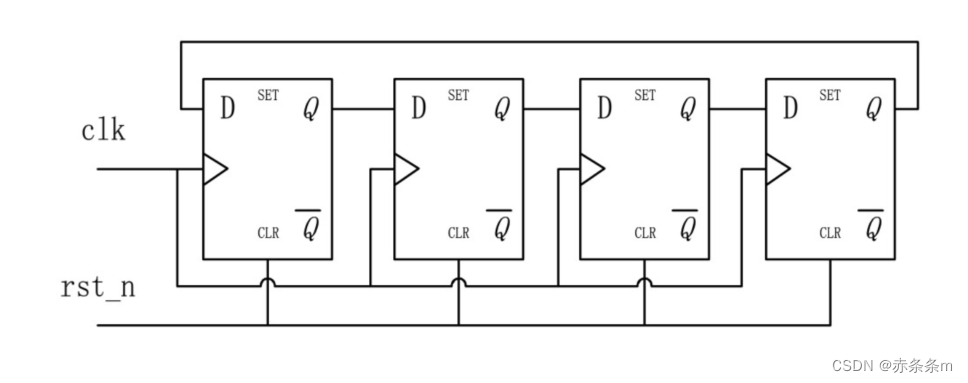

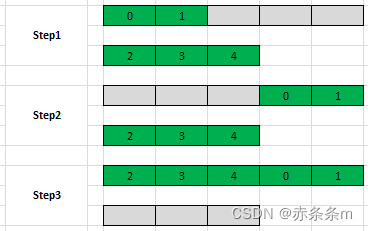

2.环形移位寄存器

以图为例子,数组data的大小为5,值分别为{0,1,2,3,4},循环右移3位

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always@(posedge clk)begin

if(load)

q <= data;

else

begin

case(ena)

2'b01: q <= {q[0],q[99:1]};

2'b10: q <= {q[98:0],q[99]};

default: q <= q;

endcase

end

end

endmodule

二、算术移位寄存器

左移:属于逻辑移位,补’0’

右移:属于算术移位,补’符号位’

例:

01010101>>3=00001010(正数右移)

11010101>>3=11111010(负数右移)

01101011<<3=01011000

(补码的算术移位运算)

1题目

Build a 64-bit arithmetic shift register, with synchronous load. The shifter can shift both left and right, and by 1 or 8 bit positions, selected by amount.

(64位算术移位寄存器)

load: Loads shift register with data[63:0] instead of shifting.

ena: Chooses whether to shift.

amount: Chooses which direction and how much to shift

- 2’b00: shift left by 1 bit.

- 2’b01: shift left by 8 bits.

- 2’b10: shift right by 1 bit.

- 2’b11: shift right by 8 bits.

代码如下(示例)

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always@(posedge clk)begin

if(load)

q <= data;

else if(ena)

case(amount)

2'b00: q <= {q[62:0],1'd0};

2'b01: q <= {q[55:0],8'd0};

2'b10: q <= {q[63],q[63:1]};

2'b11: q <= {{8{q[63]}},q[63:8]};

endcase

else

q <= q;

end

endmodule

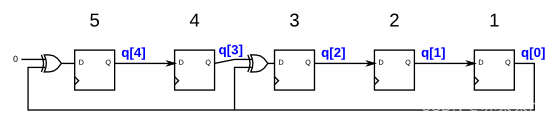

三、线性反馈移位寄存器(LFSR)

LFSR的反馈函数就是简单地对移位寄存器中的某些位进行异或,并将异或的结果填充到LFSR的最左端,如图所示。对于LFSR中每一位的数据,可以参与异或,也可以不参与异或。其中,我们把参与异或的位称为抽头(taps)。

下图taps在 5 和 3

构造线性移位寄存器,reset应当使LFSR归1

代码如下(示例)

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output [4:0] q

);

always@(posedge clk)begin

if(reset)

q <= 5'h1;

else begin

q[4] <= 1'b0 ^ q[0];

{q[3],q[1],q[0]} <= {q[4],q[2],q[1]};

q[2] <= q[3] ^ q[0];

end

end

endmodule

总结

最后

以上就是称心月饼最近收集整理的关于HDLbits笔记-移位寄存器Circuits----sequential Logic前言一、shift registers(移位寄存器)二、算术移位寄存器三、线性反馈移位寄存器(LFSR)总结的全部内容,更多相关HDLbits笔记-移位寄存器Circuits----sequential内容请搜索靠谱客的其他文章。

发表评论 取消回复