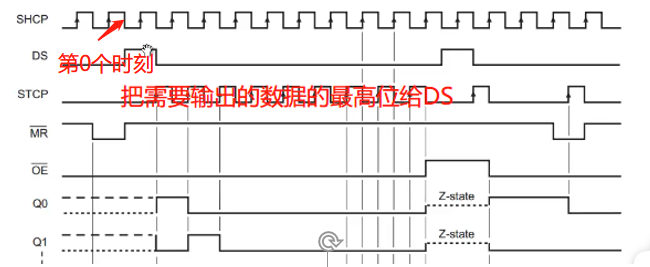

1 串转并功能,通过移位寄存器和输出锁存器实现

2 FPGA需要通过74HC595这个芯片把16位的数据(sel+seg)变为并行端口用来驱动数码管

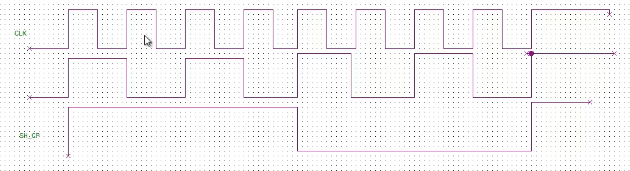

3 3.3V供电情况下,取SHCP时钟频率位12.5MHz(50-20ns,25-40ns,12.5-80ns),让其每40ns翻转一次,也就是每两个CLK周期翻转一次

上图所对应的代码段

parameter CNT_MAX = 2;

reg [7:0]divider_cnt;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

divider_cnt <= 0;

else if(divider_cnt == CNT_MAX - 1'b1)

divider_cnt <= 0;

else

divider_cnt <= divider_cnt + 1'b1;

assign sck_plus = (divider_cnt == CNT_MAX - 1'b1)

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

SH_CP <= 0;

else if(sck_plus)

SH_CP <= ~ SH_CP;

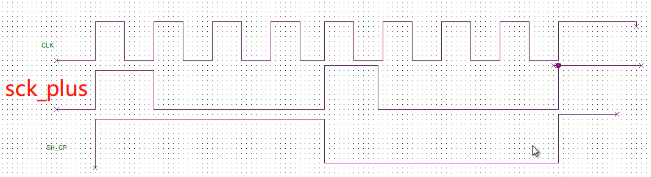

上图所对应打代码

reg [7:0]divider_cnt;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

divider_cnt <= 0;

else if(divider_cnt == 3)

divider_cnt <= 0;

else

divider_cnt <= divider_cnt + 1'b1;

assign sck_plus = (divider_cnt == 3)

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

SH_CP <= 0;

else if(sck_plus)

SH_CP <= ~ SH_CP;32个时刻输出16位数据

reg [5:0]SHCP_EDGE_CNT;//计的是SHCP的边沿变化

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

SHCP_EDGE_CNT <= 0;

else if(sck_plus)begin

if(SHCP_EDGE_CNT == 32)

SHCP_EDGE_CNT <= 0;

else

SHCP_EDGE_CNT <= SHCP_EDGE_CNT + 1'b1;

end

else

SHCP_EDGE_CNT <= SHCP_EDGE_CNT;

//根据SHCP_EDGE_CNT值是多少,决定干什么事

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)begin

ST_CP <= 1'b0;

DS <= 1'b0;

SH_CP <= 1'b0;

end

else begin

case(SHCP_EDGE_CNT)

0:begin SH_CP <= 0; ST_CP <= 1'd0; DS <= r_data[15];end

1:begin SH_CP <= 1; ST_CP <= 1'd0;end

2:begin SH_CP <= 0; DS <= r_data[14];end

3:begin SH_CP <= 1; end

4:begin SH_CP <= 0; DS <= r_data[13];end

5:begin SH_CP <= 1; end

6:begin SH_CP <= 0; DS <= r_data[12];end

7:begin SH_CP <= 1; end

8:begin SH_CP <= 0; DS <= r_data[11];end

9:begin SH_CP <= 1; end

10:begin SH_CP <= 0; DS <= r_data[10];end

11:begin SH_CP <= 1; end

12:begin SH_CP <= 0; DS <= r_data[9];end

13:begin SH_CP <= 1; end

14:begin SH_CP <= 0; DS <= r_data[8];end

15:begin SH_CP <= 1; end

16:begin SH_CP <= 0; DS <= r_data[7];end

17:begin SH_CP <= 1; end

18:begin SH_CP <= 0; DS <= r_data[6];end

19:begin SH_CP <= 1; end

20:begin SH_CP <= 0; DS <= r_data[5];end

21:begin SH_CP <= 1; end

22:begin SH_CP <= 0; DS <= r_data[4];end

23:begin SH_CP <= 1; end

24:begin SH_CP <= 0; DS <= r_data[3];end

25:begin SH_CP <= 1; end

26:begin SH_CP <= 0; DS <= r_data[2];end

27:begin SH_CP <= 1; end

28:begin SH_CP <= 0; DS <= r_data[1];end

29:begin SH_CP <= 1; end

30:begin SH_CP <= 0; DS <= r_data[0];end

31:begin SH_CP <= 1; end

32:begin ST_CP <= 1; end

default:

begin

ST_CP <= 1'b0;

DS <= 1'b0;

SH_CP <= 1'b0;

end

endcase

end

最后

以上就是整齐飞鸟最近收集整理的关于串行移位寄存器原理与结构分析的全部内容,更多相关串行移位寄存器原理与结构分析内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复