触发器1

功能

- 基本D触发器,在时钟上升沿时触发

输入

- 时钟 CLK

- 输入端 D

输出

- 输出 Q:时钟信号为上升沿时,D触发器触发,将输入端D的数据传递给Q

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF1 IS

PORT (CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END DFF1;

ARCHITECTURE bhv OF DFF1 IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (CLK,Q1) BEGIN

IF CLK'EVENT AND CLK='1' THEN Q1<=D;-- 也可以这样写NOT CLK'STABLE AND CLK='0'

-- 下降沿,CLK'EVENT AND CLK='0' 或者 NOT CLK'STABLE AND CLK='1'

END IF;

END PROCESS;

Q<=Q1;

END bhv;

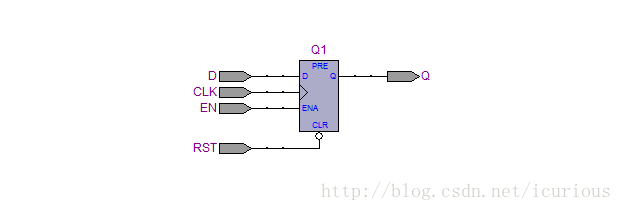

触发器2

功能

- D触发器,具有异步复位功能(即,复位控制端RST不用受时钟CLK信号控制),和时钟使能(即时钟使能信号为1时,时钟处于上升沿时,才能导致D触发器触发)

输入

- 时钟 CLK

- 时钟使能信号 EN:EN=’1’,时钟信号为上升沿(RST=‘1’),D触发器才触发

- 异步清零 RST:在任何时候RST=‘0’,D触发器的输出端立即被清零

- 输入 D:

输出

- 输出 Q:D触发器触发时,将输入信号输出到Q

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF2 IS

PORT (CLK,EN,D,RST: STD_LOGIC; Q:OUT STD_LOGIC);END;

ARCHITECTURE bhv OF DFF2 IS

SIGNAL Q1: STD_LOGIC;

BEGIN

PROCESS (CLK,EN,RST,Q1) BEGIN

IF RST='0' THEN Q1<='0';

ELSIF CLK'EVENT AND CLK='1' AND EN='1'

THEN Q1<=D;END IF;

END PROCESS;

Q<=Q1;

END bhv;

锁存器1

功能

- 含有异步、清零控制

输入

- 时钟脉冲 CLK:

- 清零输入 RST:

- 数据端口 D:

输出

- 输出 D:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LTCH1 IS

PORT (CLK,D,RST:IN STD_LOGIC;Q:OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF LTCH1 IS

BEGIN

PROCESS (CLK,D,RST)

BEGIN

IF RST='0' THEN Q<='0';

ELSIF CLK='1' THEN Q<=D;

END IF;

END PROCESS;

END bhv;

锁存器2

功能

- 基本锁存器功能:即时钟信号CLK为高电平时,输入D被锁存,输出端Q<=D

输入

- 时钟脉冲 CLK:提供一定频率的时钟信号

- 数据端口 D:提充输入电平

输出

- 输出 D:时钟信号CLK为1电平时,输入D被锁存,输出端Q<=D;信号CLK为0电平时,保持原来状态不变。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LTCH IS

PORT(CLK,D:IN STD_LOGIC; Q:OUT STD_LOGIC);

END ;

ARCHITECTURE bhv OF LTCH IS

BEGIN

PROCESS (CLK,D) BEGIN

IF CLK='0' THEN Q<=D;END IF;

END PROCESS ;

END BHV;

注: 从功能和VHDL程序上可以看出触发器和锁存器的不同之处在于,触发器在时钟信号上升或者下降时进行触发。

比较器

功能

- 基本双端口电位比较器,输入端a电位大于输入端b,输出1;反之,输出0;

输入

- 输入端口a

- 输入端口b

输出

- 输出 q:输入端a电位大于输入端b,输出1;反之,输出0

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY COM_BAD IS

PORT (a,b: IN BIT;

q:OUT BIT);

END ;

ARCHITECTURE one OF COM_BAD IS

BEGIN

CMP:PROCESS (a,b) BEGIN --CMP

IF a>b THEN q<='1';

ELSE q<='0';END IF;

END PROCESS;

END;

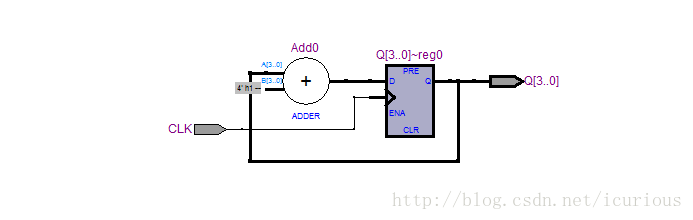

计数器1

功能

- 四位二进制加法计数器

输入

- 时钟 CLK

输出

- 输出 Q:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CNT4 IS --COUNTER OF 4 BITS

PORT (CLK:IN BIT;

Q:BUFFER INTEGER RANGE 15 DOWNTO 0);

END;

ARCHITECTURE bhv OF CNT4 IS

BEGIN

PROCESS (CLK) BEGIN

IF CLK'EVENT AND CLK='1' THEN Q<=Q+1;END IF;

END PROCESS;

END bhv;

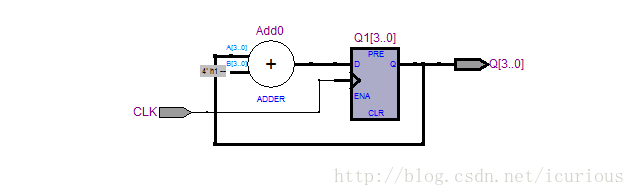

计数器2

功能

- 四位二进制加法计数器

输入

- 时钟 CLK

输出

- 输出 Q:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;--NECESSARY!!! FOR USING '+'

ENTITY CNT4_1 IS --COUNTER OF 4 BITS

PORT (CLK:IN BIT;

Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE bhv OF CNT4_1 IS

SIGNAL Q1:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS (CLK) BEGIN

IF CLK'EVENT AND CLK='1' THEN Q1<=Q1+1; END IF;

END PROCESS;

Q<=Q1;

END bhv;

最后

以上就是稳重黄豆最近收集整理的关于【VHDL】常见触发器/锁存器/比较器/计数器的VHDL描述的全部内容,更多相关【VHDL】常见触发器/锁存器/比较器/计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复