我是靠谱客的博主 靓丽钻石,这篇文章主要介绍【Verilog-A】延迟波形代码测试与仿真前言一、延迟波形功能需求二、Verilog-A 代码及解读三、 测试环境四 、仿真结果,现在分享给大家,希望可以做个参考。

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 前言

- 一、延迟波形功能需求

- 二、Verilog-A 代码及解读

- 三、 测试环境

- 四 、仿真结果

前言

今天做一个延迟波形的Verilog-A代码,并对代码细节做出解释,最后再对其进行仿真和验证。

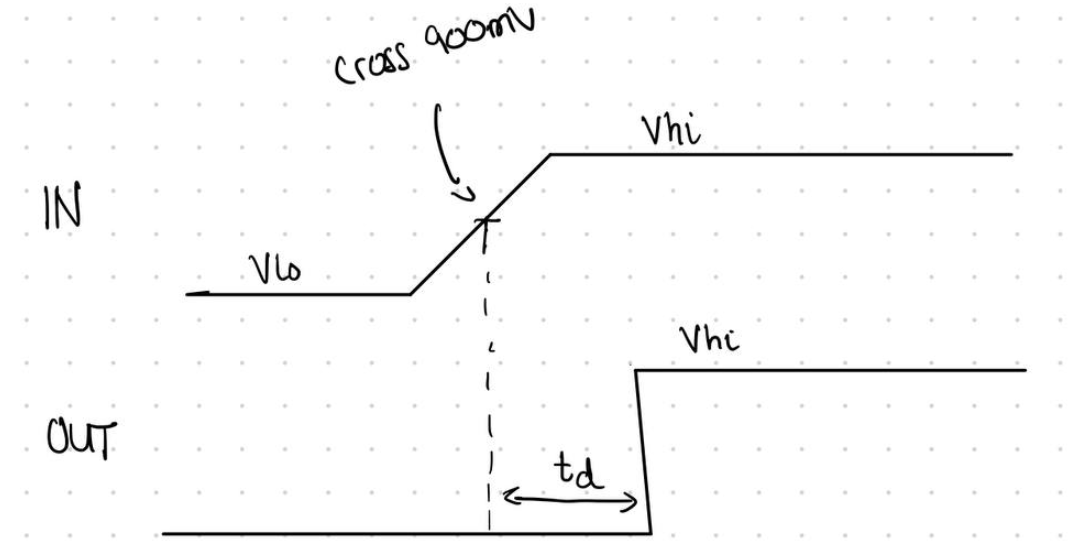

一、延迟波形功能需求

功能如图:

二、Verilog-A 代码及解读

代码如下:

module delay_clk(clk_in, clk_out);

input clk_in;

output clk_out;

electrical clk_in, clk_out;

parameter real td = 100n;//延迟100ns

real clk_val = 0;

parameter vsup = 1.8;

analog begin

@ ( cross(V(clk_in) - vsup/2.0, +1) ) begin

clk_val = vsup;//当输入时钟在900 mv时,clk_val为vsup,波形同方向上升

end

@ ( cross(V(clk_in) - vsup/2.0, -1) ) begin

clk_val = 0;//当输入时钟在900 mv时,clk_val为0,波形反方向下降。

end

V(clk_out) <+ transition(clk_val, td, 1n, 1n);//赋值,延时,上升时间,下降时间

end

endmodule

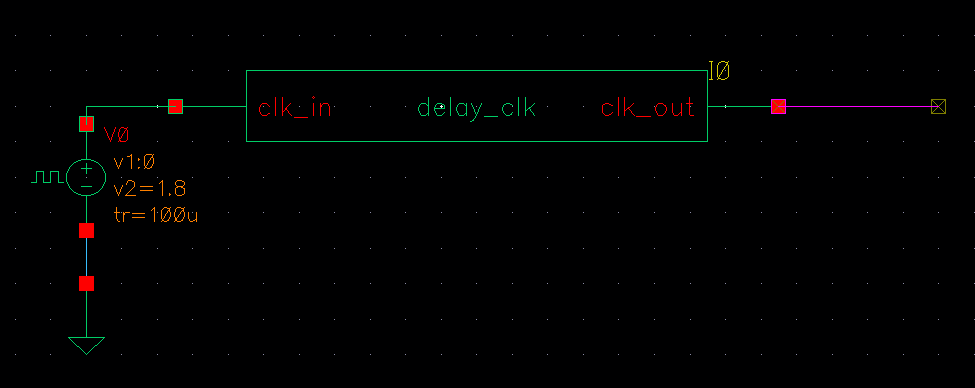

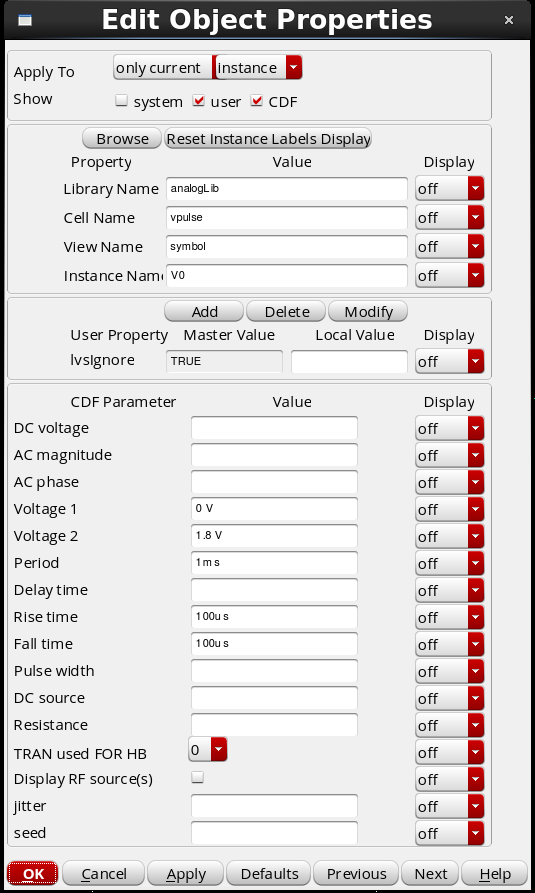

三、 测试环境

将写好的Verilog-A代码进行仿真,并且使用一个Vplus进行仿真,如图所示,参数设置如下。

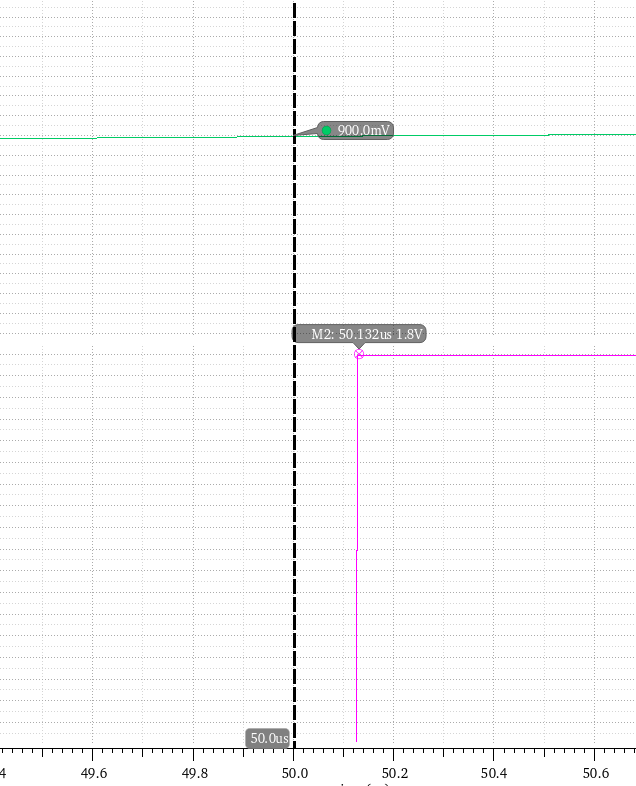

四 、仿真结果

仿真结果显示与预定功能一致:

最后

以上就是靓丽钻石最近收集整理的关于【Verilog-A】延迟波形代码测试与仿真前言一、延迟波形功能需求二、Verilog-A 代码及解读三、 测试环境四 、仿真结果的全部内容,更多相关【Verilog-A】延迟波形代码测试与仿真前言一、延迟波形功能需求二、Verilog-A内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复