4 - 时序逻辑代码设计和仿真

计数器

-

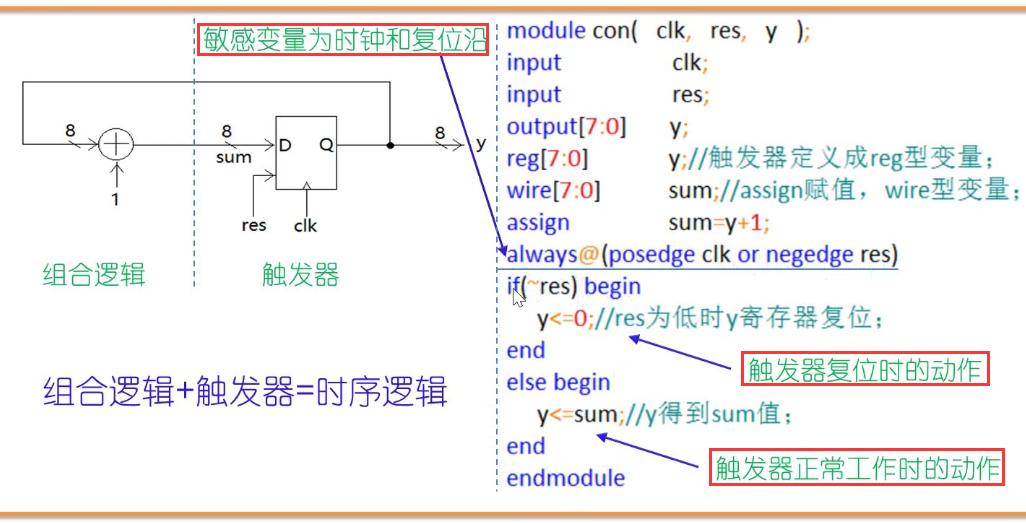

always 块理解:

- 触发器的敏感变量是时钟信号的上升沿和复位信号的下降沿【这是时序逻辑电路的特点】。敏感信号的意思是:只有到达时钟信号的上升沿和复位信号的下降沿时,always 才会动,即去判断引起 always 变化的是不是复位信号。

- if() 里面是触发器复位时的动作【res 为0】,else 是触发器正常工作时的动作。

- 触发器复位就是清零,正常工作就是把 sum 送给 y。

-

之前的组合逻辑中也用到过 always 和 reg 型变量,但它们都不是触发器,触发器必须要有时钟信号和复位信号,且是边缘触发。这里的 y 是 8 位触发器(register)

-

时序逻辑 = 组合逻辑 + 触发器

计数器的组合逻辑部分是:sum = y + 1

代码:

//2021.11.18 lyw

//counter

`timescale 1ns/10ps

module counter (

clk,

res,

y

);

input clk;

input res;

output[7:0] y;

reg [7:0] y;

//the result of +1

//wire[7:0] sum;

//Combinatorial logic part

//assign sum=y+1;

always @(posedge clk or negedge res) begin

if (~res) begin

y<=0;

end

else begin

// y<=sum;

y<=y+1;

end

end

endmodule

//----testbench of counter-----

module counter_tb;

reg clk,res;

wire [7:0] y;

counter counter (

.clk(clk),

.res(res),

.y(y)

);

initial begin

clk<=0;

res<=0;

#17 res<=1; //stop reset

#6000 $stop;

end

always #5 clk=~clk; //clock=10ns

endmodule

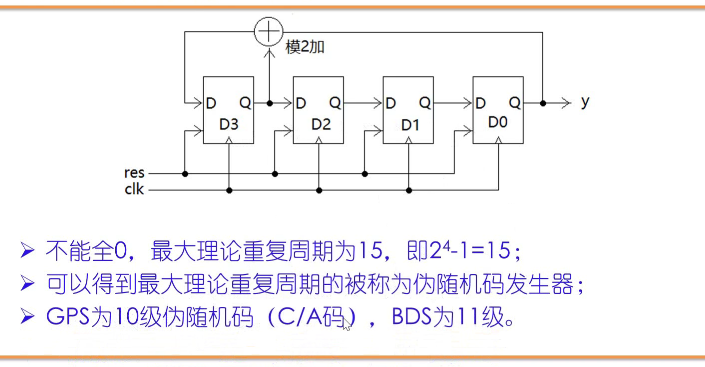

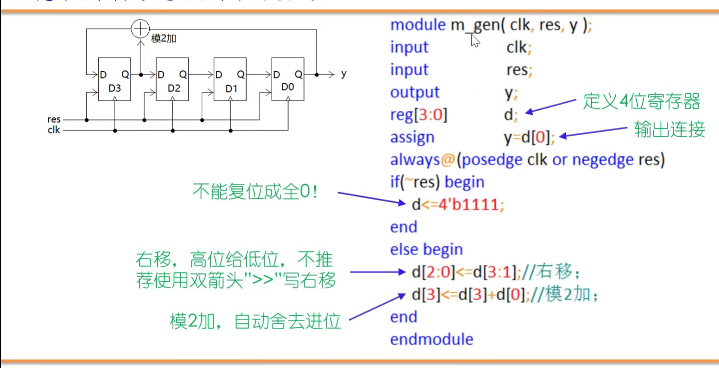

关键:寄存器右移的写法,模 2 加的写法。

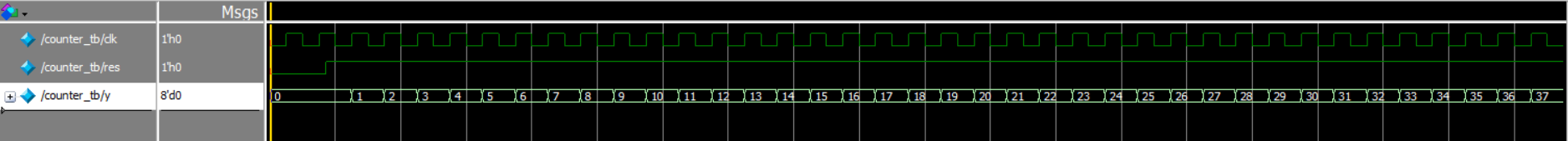

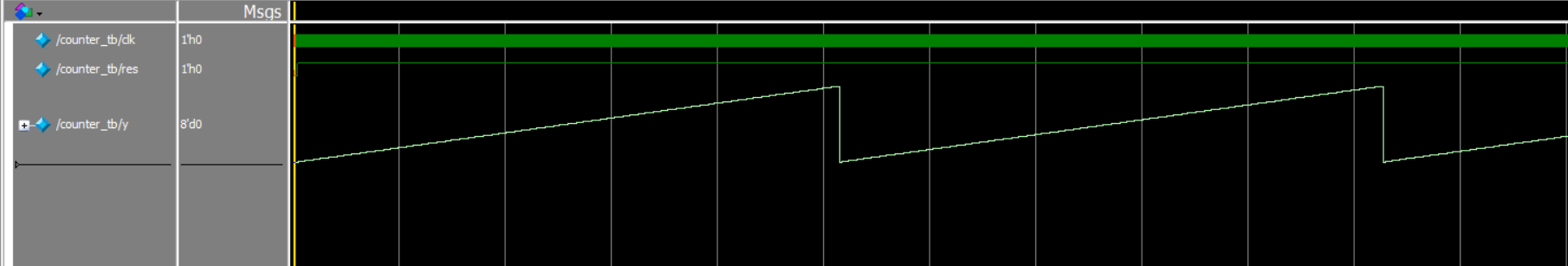

仿真波形:

模拟显示(format-analog(automatic))

4 级伪随机码发生器

4 级伪随机码发生器由 4 个触发器构成,理论上 16 个状态,但实际只有15个。

原因:触发器的结构是时钟到来时,数据向右移动。第一个触发器的输入来源于它自己的输出与最后一个输出的模 2 加。所以不能出现全 0 状态,全 0 模 2 加以后还是0。

BDS:北斗。

代码:

//2021.11.18 lyw

//4-level pseudo-random code generator

`timescale 1ns/10ps

module m_gen (

res,

clk,

y

);

input res;

input clk;

output y;

reg [3:0] d;

assign y=d[0];

always @(posedge clk or negedge res) begin

if (~res) begin

d<=4'b1111; //can't be 0000

end

else begin

d[2:0]<=d[3:1]; //right shift 1 bit

d[3]<=d[3]+d[0]; //addition modulo 2

end

end

endmodule

//----testbench of m_gen_tb----

module m_gen_tb;

reg res,clk;

wire y;

m_gen m_gen (

.res(res),

.clk(clk),

.y(y)

);

initial begin

res=0;

clk=0;

#15 res=1;

#300 $stop; //15*10ns=150ns,run 2 times

end

always #5 clk=~clk;

endmodule

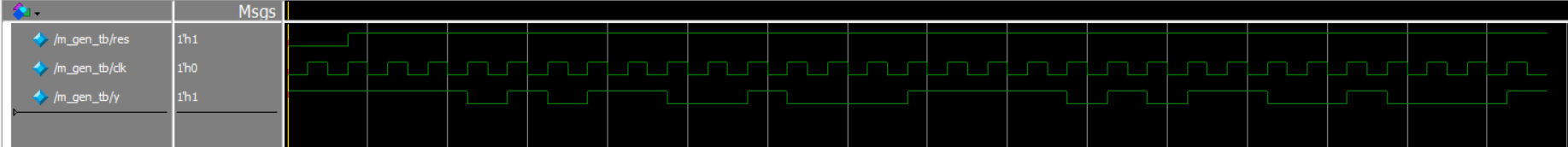

仿真波形:

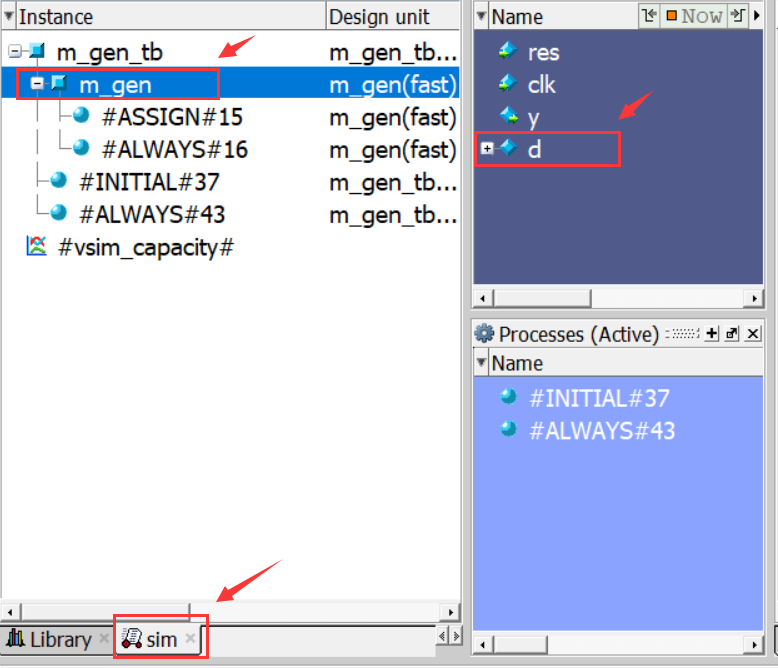

若想看内部 4 个寄存器,去 sim 那加进来,注意要选【selected signals】而不是【signals in region】,即单独加一个不全加进来。

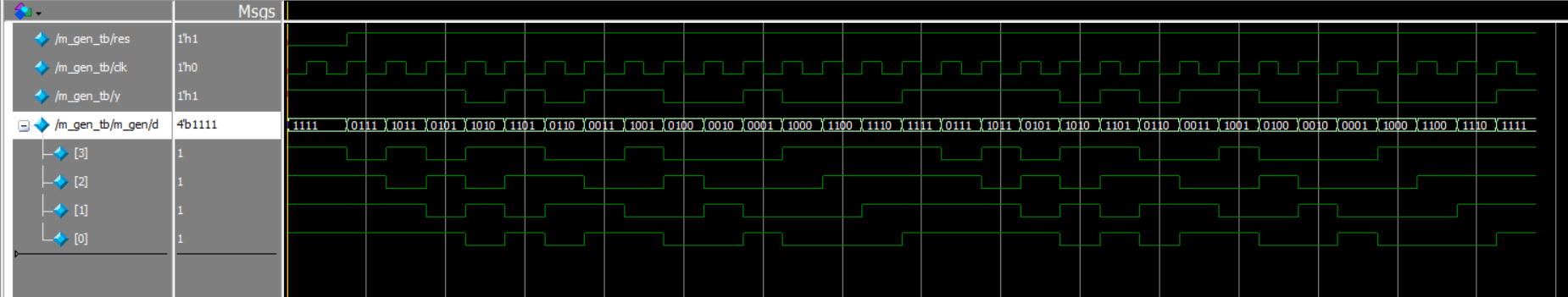

仿真结果:

可以清晰看到几个信号的移位关系。

PS:内容总结自网络。

最后

以上就是成就冰淇淋最近收集整理的关于4 - 时序逻辑代码设计和仿真4 - 时序逻辑代码设计和仿真的全部内容,更多相关4内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复