需求说明:IC设计基础

内容 :浮点运算定点化处理

来自 :时间的诗

原文:http://blog.csdn.net/mccrocodile/article/details/6754929

通常在FPGA中做信号处理为达到比较高的fMax和较少的资源占用,通常使用定点化数字信号处理,虽然FPGA厂商和IP提供商提供了一些浮点IP,但是目前大多数应用还是趋向定点化处理。这里主要介绍在设计滤波器中使用工具中的定点化选项,实现滤波器的定点化,为后面一节的HDL代码生成做铺垫。

这儿还是使用前面的例子,来实施定点化。

FDAtool中定点化

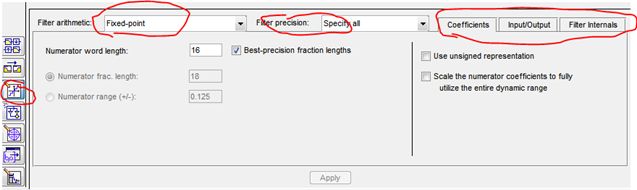

如下图所示为FDATool中的定点化过程中截图,选择左侧设置量化参数(Set Quantization Parameters )按钮,在滤波器结构栏选择定点,滤波器精度有最高精度和指定精度,通常使用指定精度这样比较节约资源,最后部分为对滤波器的参数,输入数出和滤波器内部进行定点化设计。

在设置滤波器内部的参数,如乘法器,累加器的精度和整数的溢出模式。在设置精度是通常开始设置较大的精度和动态范围,满足要求后再优化。整数溢出的模式Wrap模式占用资源最少,但是如果正式部分动态范围不够会带来糟糕情况,而且不利于整体的稳定性;Staturate会占用额外的逻辑资源。

FilterBuilder中定点化

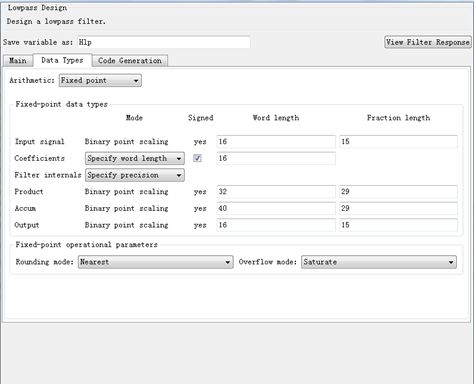

从下图可以看得出与FDATool的定点化设置是一致的。这儿就不再做介绍了。

fdesign中的定点化

(准确的应该成为使用面向对象的方式的滤波器定点化)

详细的帮助中搜索Fixed-Point Filter Design。

前面介绍的基于GUI的定点化都是一个根据经验的迭代化的优化过程,下面来详细的说下基于fdesign的定点化过程。

滤波器的定点化包含两个主要的部分:滤波器数的量化和动态范围分析。(The dynamic range analysis is a process of fine tuning the scaling of each node to ensure that the fraction lengths are set for full input range coverage and maximum precision。)

1、首先修改滤波器对象属性为定点的:(当然这儿的滤波器对象也可以来自于fdatool等设计的导出的滤波器对象)

Hf=hd;

Hf.Arithmetic='fixed';

2、初步设置滤波器系数的字长

set(Hf, 'CoeffWordLength', 9);%设置滤波器系数的字长

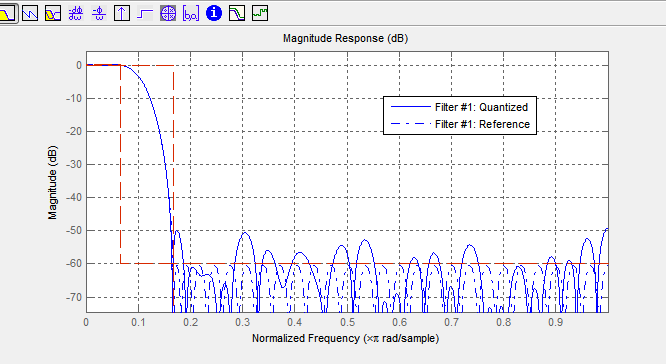

fvtool(Hf)%,比较不同字长设置

屏幕剪辑的捕获时间: 2011/8/30 22:22

可以清晰的观察到定点化和浮点的幅频响应的区别,通过观察是否满足要求进一步优化滤波器系数的字长,增加字长达到更高的性能,缩减字长节约资源减小面积。如在Altera的QII中,如果乘数是固定且位宽比较小(比如小于10bit时),综合时会使用移位和加法实现乘法(有点类似于RAG算法),但当乘数比较大时则需要使用硬件乘法器。如果较小片子硬件乘法器不足就是个糟糕的事情了。

3、设置滤波器内部的位宽:累加器,乘法器,输出信号

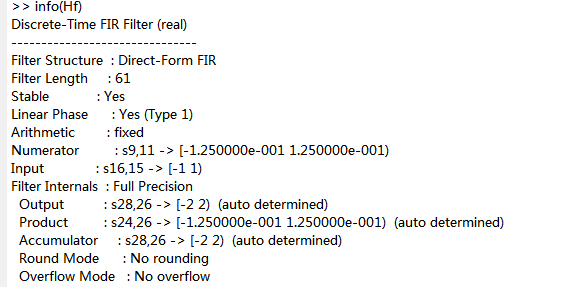

info(Hf) %有观察到的信息可以看出位宽过宽

屏幕剪辑的捕获时间: 2011/8/30 22:32

如图所示可以看到,自动设置的位宽以及其动态范围,这些自动设置的位宽通常是首先满足精度,还需要根据硬件(DSP,FPGA)特性做修改。下面针对Altera的CIII片子给出一个设置:

set (Hf, 'InputWordLength', 10);%输入ADC位宽

set (Hf, 'FilterInternals', 'SpecifyPrecision');%设置滤波器内部参数

set (Hf, 'ProductWordLength', 18);%如Altera的CIII片子的乘法器为9的倍数,这儿选18bit

set (Hf, 'AccumWordLength', 22);%累加器的字长,通常累加器比乘法器多4比特作为保护位宽

set (Hf, 'OutputWordLength', 16);%输出数据总线

输入信号位宽通常和ADC是保持一致的,乘法器的位宽通常设置9的倍数(某些高档片子含有DSP40,那就设置为40)。诸如硬件乘法器资源,如果想要充分利用,那么你就需要参考器件的硬件特性。累加器通常要比乘法器宽4bit作为保护比特。如果设置得过宽会造成累加器的时延过大,得不到一个较大的fMax。

到这里滤波器的基本设置算是完成了,但是还是有可能在使用的使用发生溢出等错误。动态分析将进一步优化滤波器的定点化设置,以降低溢出的发生。

4、动态分析:进一步精细调整系数的比例(Scaling)。

系数最好是又能覆盖所有输入信号,同时保持最大的精度,但这是互相矛盾的。所以在动态分析过程中用于测试的输入数据的选择是非常重要的。如果设置较大的动态范围,可以覆盖输入信号的范围,但是精度会损失;如果设置较窄的动态范围,可以保持较好的精度,但是输入信号可能超出范围引起溢出。

最坏情况测试法:

1)源代码和报告如下,首先使用脉冲响应的取符号函数,设置信号最大幅度,作为信号的激励。

2)以测试激励自动调整动态范围,如果不使用这个选项观察一下3中的报告时什么样子的。

3)创建fipref对象开启记录模式,定点化滤波,观察定点化滤波过程的报告。

tx = 2*sign(fliplr(impz(Hf)));%激励

Hf2 = autoscale(Hf, tx);%自动调整动态范围

fipref('LoggingMode', 'on', 'DataTypeOverride', 'ForceOff');%创建fipref对象打开记录

y = filter(Hf2, tx);

fipref('LoggingMode', 'off');

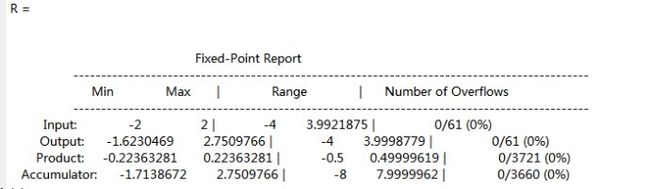

R = qreport(Hf2)%查看报告,报告最近的顶点滤波计算报告

屏幕剪辑的捕获时间: 2011/9/5 21:29

下面是对信号分离的定点化测试:

%% 对信号分离的定点化测试

fipref('LoggingMode', 'on', 'DataTypeOverride', 'ForceOff');%创建fipref对象打开记录

y = filter(Hf2, x);

fipref('LoggingMode', 'off');

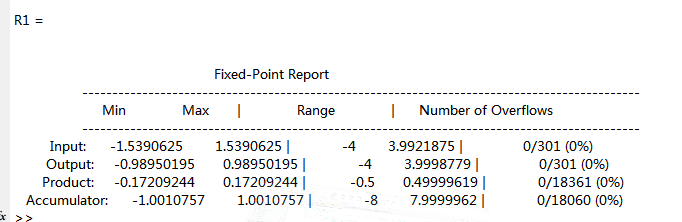

R1 = qreport(Hf2)%查看报告,报告最近的顶点滤波计算报告

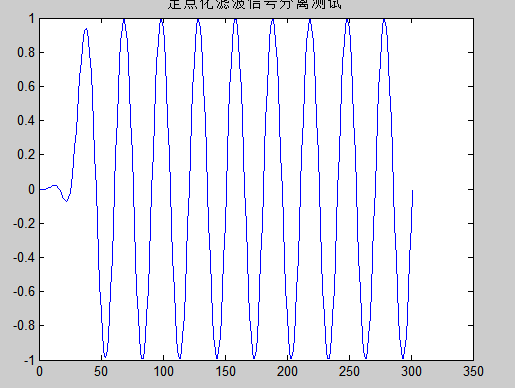

figure;plot(y);title('定点化滤波信号分离测试')

屏幕剪辑的捕获时间: 2011/9/5 21:39

屏幕剪辑的捕获时间: 2011/9/5 21:39

通过上面的报告和滤波结果观察可以看出,定点化达到了效果。这就为后面HDL代码生成做好基本的准备。

总结:

通过上面的例子,可以得知使用面向对象方式实现定点化是一个更优秀的方式。根据测试的激励可以自动调整滤波器的精度以达到不同的动态范围,达到精度和动态范围(过小会引起溢出)的权衡,那么也就看出合适的测试激励的重要性。这种滤波器的定点化方法对IIR滤波器的定点化优势尤其明显。这里先不介绍,由于IIR的定点化有时比较复杂,放到后面单独讨论。

所以建议亲自试试使用fdesign的方式。

最后

以上就是昏睡歌曲最近收集整理的关于如何将MATLAB中得到的数据点化成线,FPGA基础知识16(Matlab中滤波器的定点化 浮点运算转换为定点运算)...的全部内容,更多相关如何将MATLAB中得到的数据点化成线,FPGA基础知识16(Matlab中滤波器的定点化内容请搜索靠谱客的其他文章。

发表评论 取消回复