我们一提到时序逻辑电路,就会想到触发器

-

先讲讲时序逻辑电路:时序逻辑电路(常简称为时序电路)内部包含存储器,用于记忆电路的工作状态和输入变化情况,其输出由当前的输入和存储信息共同确定的一种电路。

-

再讲讲几种最基本的触发器

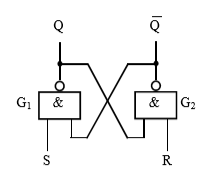

1.RS触发器

Q ‾ overline{Q} Q=1称为触发器的0状态, Q ‾ overline{Q} Q=0称为触发器的触发状态(1状态)

-

RS=01,触发器状态为0

-

RS=10,触发器状态为1,若s变为1,结果也是1

-

RS=11,触发器状态为1

-

保存在RS=00,破坏了两个触发器输出信号应该相反的规则

总结: 所谓稳定状态,是指当输入信号 为无效电平时(这里是RS 11 ),触发器的状态稳定不变。

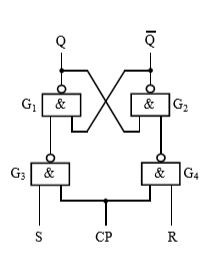

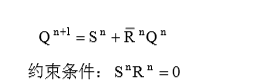

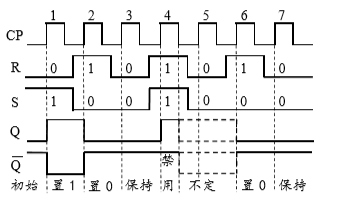

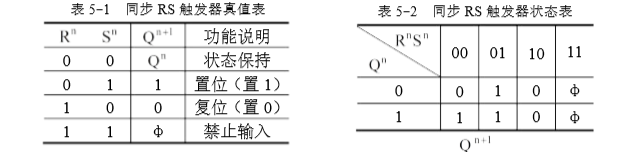

同步RS触发器

特点:当CP为高电平时,G3G4的输出分别为 S ‾ overline{S} S R ‾ overline{R} R

最后

以上就是大胆项链最近收集整理的关于深入浅出时序逻辑电路(1)的全部内容,更多相关深入浅出时序逻辑电路(1)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复