任务描述

本关需要你根据所学的组合逻辑及数字电路的知识完成三人表决电路的设计,实现少数服从多数的表决规则,根据逻辑真值表和逻辑表达式完成表决功能。

运用Verilog HDL进行设计,完善三人表决电路的功能描述风格代码,具备组合逻辑电路的设计仿真和测试的能力。

逻辑原理

三人表决电路中, 当表决某个提案时,多数人同意,则提案通过;同时有一个人具有否决权。若全票否决,也给出显示。

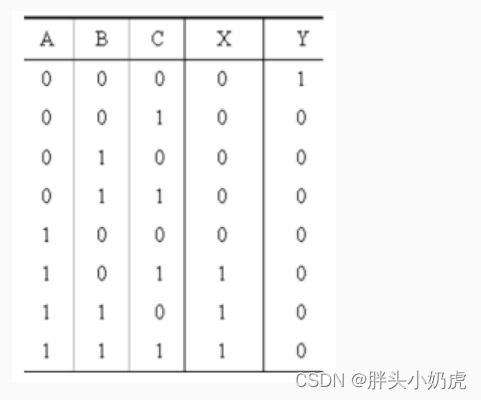

设输入为 A、 B、 C,且 A 具有否决权。同意用1 表示,不同意用 0 表示;输出 X 为 1 时表示提案通过; Y 为 1 时表示提案全票否决。 则三人表决电路的真值表如下表所示。

三人表决器真值表

编程要求

根据真值表,在右侧编辑器完善模块设计代码,你编写的程序要能根据不同的输入完成三人表决功能。

题目代码

module JG3(ABC,X,Y);

//input Port(s)

input [2:0] ABC;

//output Port(s)

output X, Y;

reg X, Y;

//Additional Module Item(s)

always@(ABC)

// 请在下面添加代码,实现满足三人表决器真值表;

/********** Begin *********/

/********** End *********/

endmodule

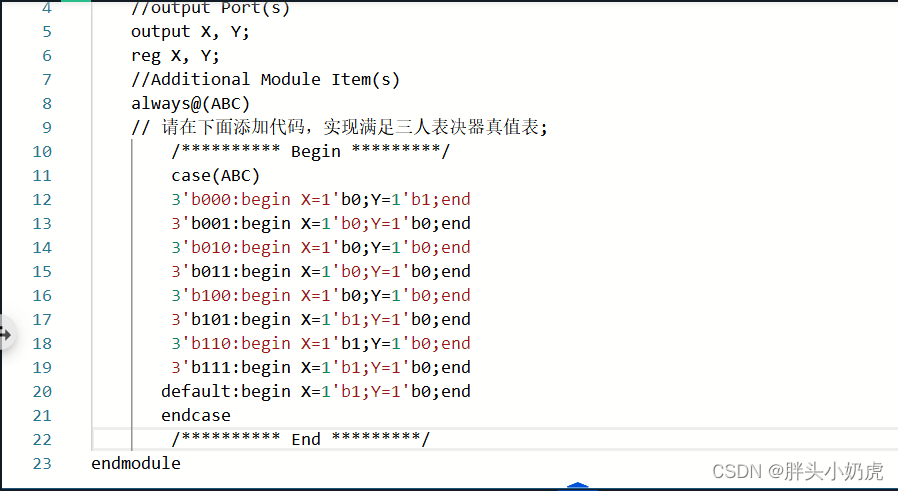

参考答案

case(ABC)

3'b000:begin X=1'b0;Y=1'b1;end

3'b001:begin X=1'b0;Y=1'b0;end

3'b010:begin X=1'b0;Y=1'b0;end

3'b011:begin X=1'b0;Y=1'b0;end

3'b100:begin X=1'b0;Y=1'b0;end

3'b101:begin X=1'b1;Y=1'b0;end

3'b110:begin X=1'b1;Y=1'b0;end

3'b111:begin X=1'b1;Y=1'b0;end

default:begin X=1'b1;Y=1'b0;end

endcase

最后

以上就是甜蜜水池最近收集整理的关于头歌平台:三人表决电路的全部内容,更多相关头歌平台内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复