我是靠谱客的博主 动听花生,这篇文章主要介绍verilog实现三人表决器要求一、38译码器的实现并封装成IP核二、蜂鸣器的简易实现三、用封装好的38译码器IP核来实现三人表决器(自己添加的功能是:用数码管显示赞成人数,以及蜂鸣器提示投票开始或结束) 四、FPGA板上验证补充:数码管显示数字原理,现在分享给大家,希望可以做个参考。

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 要求

- 一、38译码器的实现并封装成IP核

- 二、蜂鸣器的简易实现

- 1.引入库

- 2.读入数据

- 三、用封装好的38译码器IP核来实现3人表决器

- 四、FPGA板上验证

- 总结

要求

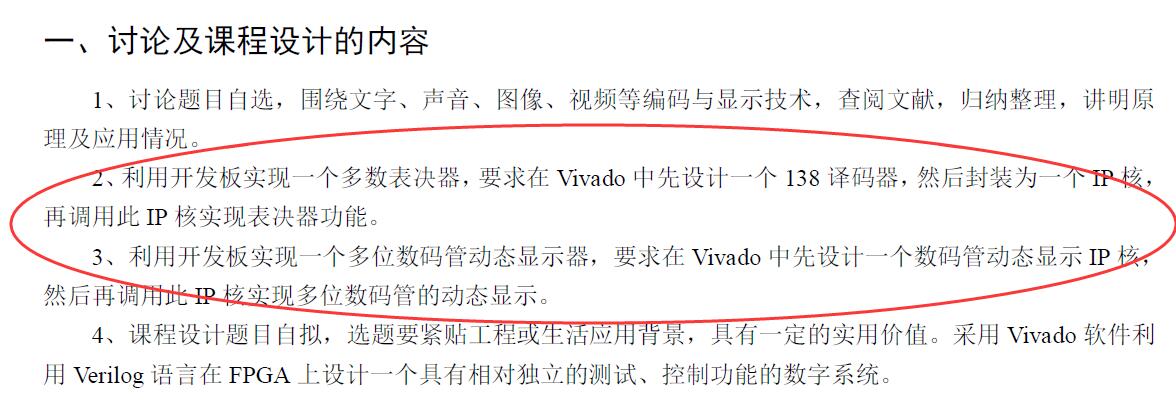

一、38译码器的实现并封装成IP核

module v74x138(g1, g2a_l, g2b_l,a,y_l) ;

input g1,g2a_l,g2b_l;

input[2:0] a;

output[7:0] y_l;

reg[7:0] y_l=0;

always@(*)

begin

if(g1&&~g2a_l&&~g2b_l)

case(a)

7:y_l=8'b01111111;

6:y_l=8'b10111111;

5:y_l=8'b11011111;

4:y_l=8'b11101111;

3:y_l=8'b11110111;

2:y_l=8'b11111011;

1:y_l=8'b11111101;

0:y_l=8'b11111110;

default:y_l=8'b11111111;

endcase

else

y_l=8'b11111111;

end

endmodule

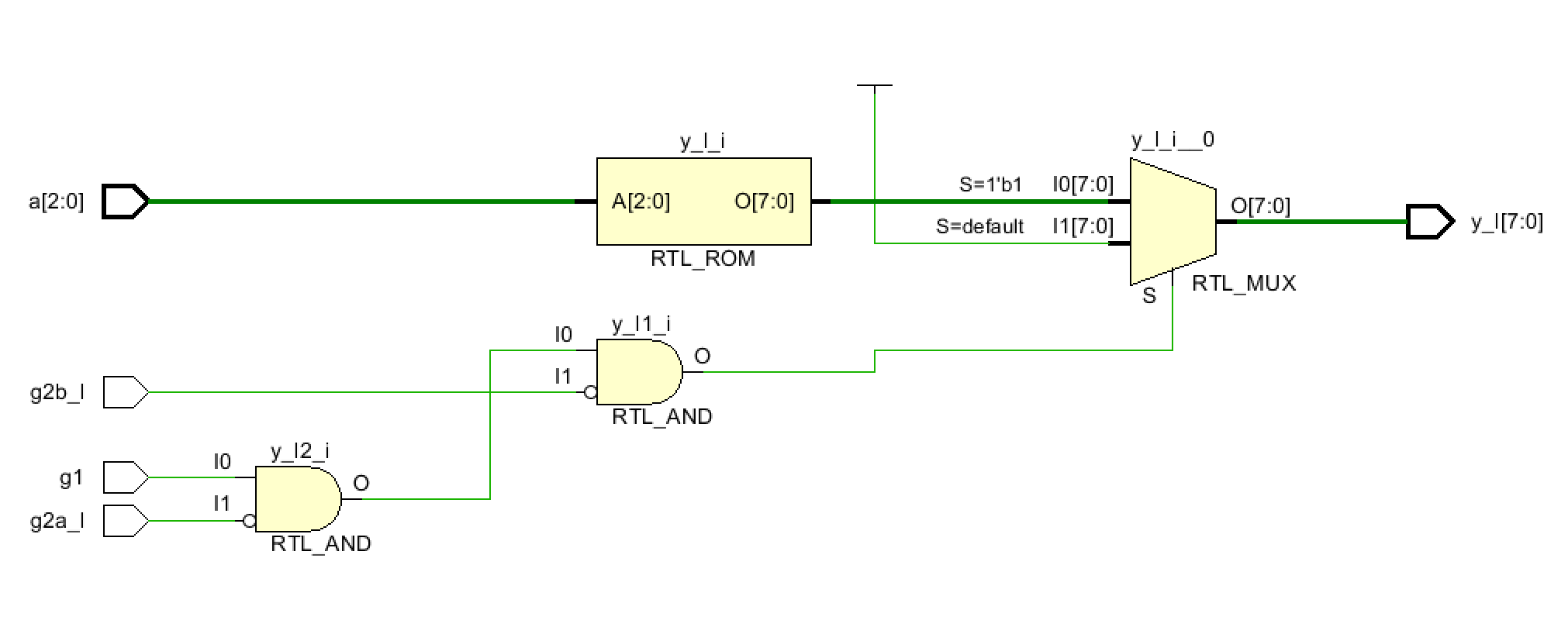

封装成IP核并再调用它的详细步骤:

https://www.icourse163.org/learn/UESTC-1002525007?tid=1463513442#/learn/content?type=detail&id=1241758007&sm=1

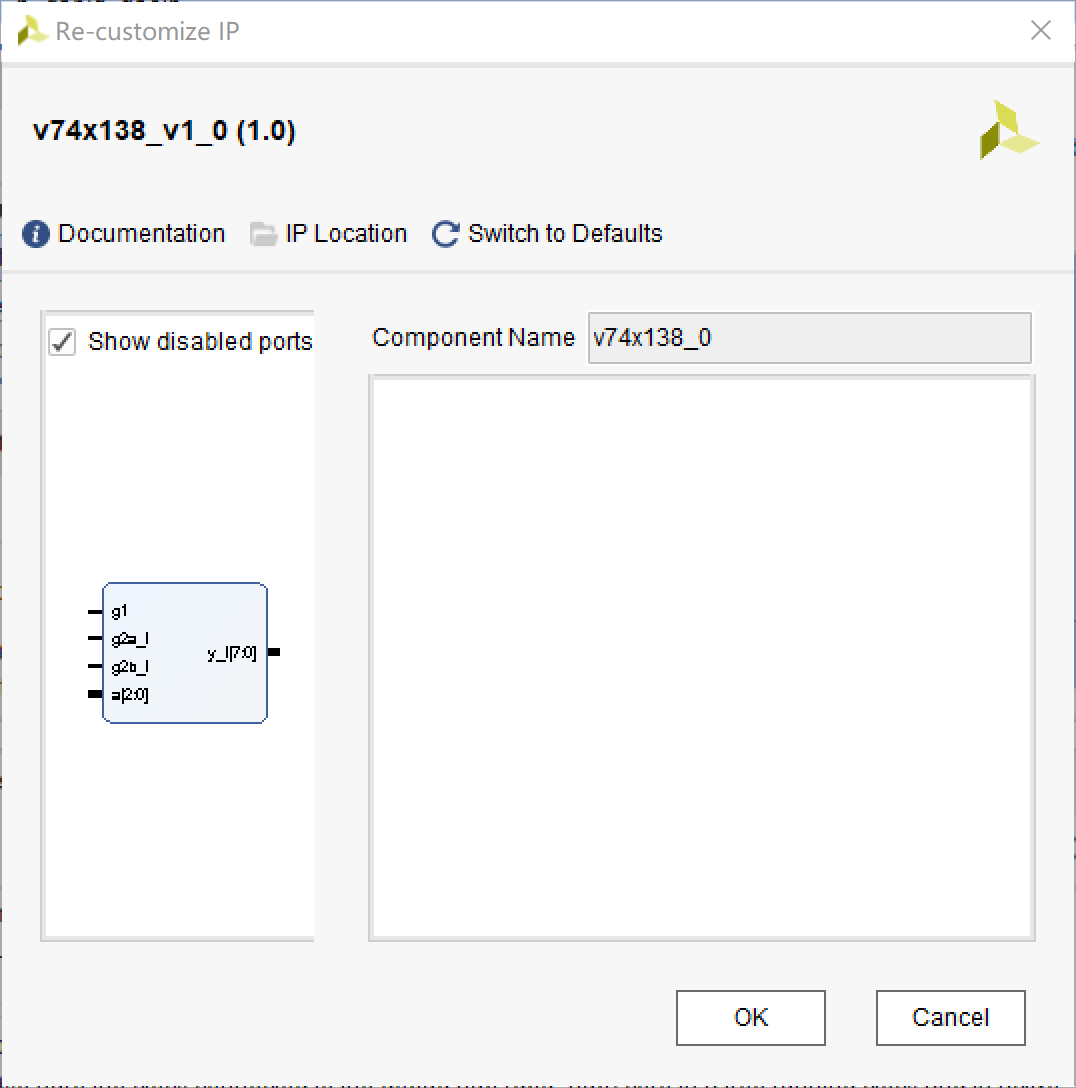

二、蜂鸣器的简易实现

module beep(ext_clk_25m, ext_rst_n, buzzer);

input ext_clk_25m;

input ext_rst_n;

output reg buzzer;

reg [19:0] cnt; //20 bit get the maximum number of 1048575;

//计数模块,计数达到1000 000次,计数器清零

always @ (posedge ext_clk_25m or posedge ext_rst_n)

begin

if(!ext_rst_n)

cnt <= 20'b0;

else if(cnt < 20'd999_999)

cnt <= cnt + 1'b1;

else

cnt <= 20'b0;

end

always @ (posedge ext_clk_25m or posedge ext_rst_n)

begin

if(!ext_rst_n)

buzzer <= 1'b0;

else if(cnt < 500_000)

buzzer <= 1'b1;

else

buzzer <= 1'b0;

end

endmodule

本来想实现的功能是: 按下按键——蜂鸣器第一次响(表示投票开始)、松开按键——蜂鸣器停止

待三人都做出投票动作后,再次 按下按键——蜂鸣器第二次响(表示投票结束)、松开按键——蜂鸣器停止

整个过程结束。

但实际的是:按下按键,蜂鸣器不响;时序逻辑还没有搞清楚........

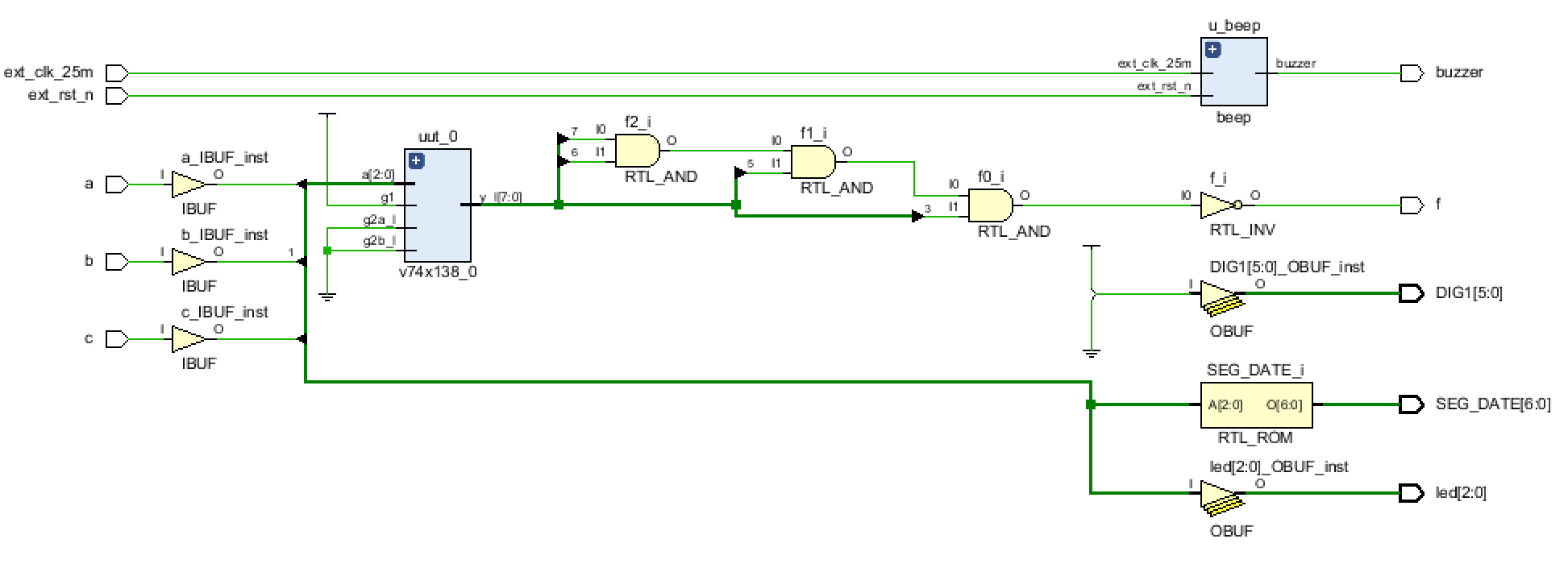

三、用封装好的38译码器IP核来实现三人表决器(自己添加的功能是:用数码管显示赞成人数,以及蜂鸣器提示投票开始或结束)

module dsbiq_useip(a, b,c,f,SEG_DATE,DIG1,led,

ext_clk_25m, ext_rst_n, buzzer);

input a;

input b;

input c;

output f;

output reg[5:0] DIG1;//片选数码管

//蜂鸣器对应IO口

input ext_clk_25m;

input ext_rst_n;

output wire buzzer;

output reg[2:0]led; //三盏灯表示三人的投票情况

output reg[6:0]SEG_DATE; //载入三个输入的值

parameter

SEG_NUM0=7'h3f, //数码管显示0

SEG_NUM1=7'h06, //数码管显示1

SEG_NUM2=7'h5b, //数码管显示2

SEG_NUM3=7'h4f; //数码管显示3

always@(*)

begin

led[2]=a; //亮灯

led[1]=b;

led[0]=c;

DIG1=6'b111110 ; //选中第一个数码管

end

always@(*) //七段码实现

begin

case({a,b,c})

3'b000:SEG_DATE=SEG_NUM0;

3'b001:SEG_DATE=SEG_NUM1;

3'b010:SEG_DATE=SEG_NUM1;

3'b011:SEG_DATE=SEG_NUM2;

3'b100:SEG_DATE=SEG_NUM1;

3'b101:SEG_DATE=SEG_NUM2;

3'b110:SEG_DATE=SEG_NUM2;

3'b111:SEG_DATE=SEG_NUM3;

//defalut:SEG_DATE=SEG_NUM0;

endcase

end

wire [7:0]y_l;

assign f=~(y_l[7]&y_l[6]&y_l[5]&y_l[3]); //f为1 即通过

//IP核v74x138的调用

v74x138_0 uut_0

(

.g1(1),

.g2a_l(0),

.g2b_l(0),

.a({c,b,a}),

.y_l(y_l)

);

//调用beep模块

beep u_beep(

.ext_clk_25m (ext_clk_25m),

.ext_rst_n (ext_rst_n),

.buzzer (buzzer)

);

endmodule

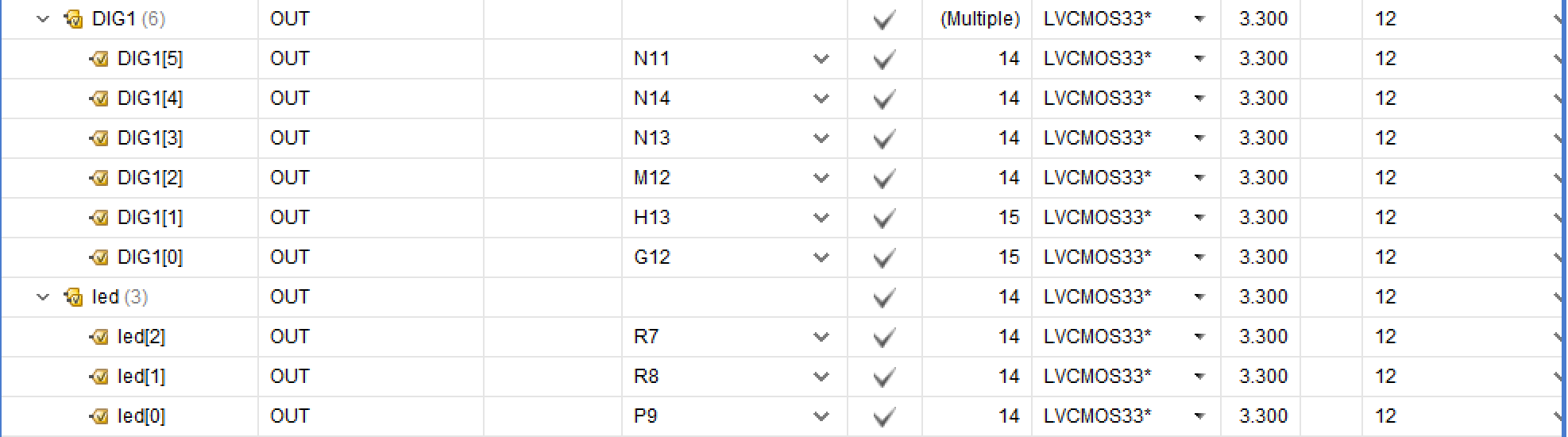

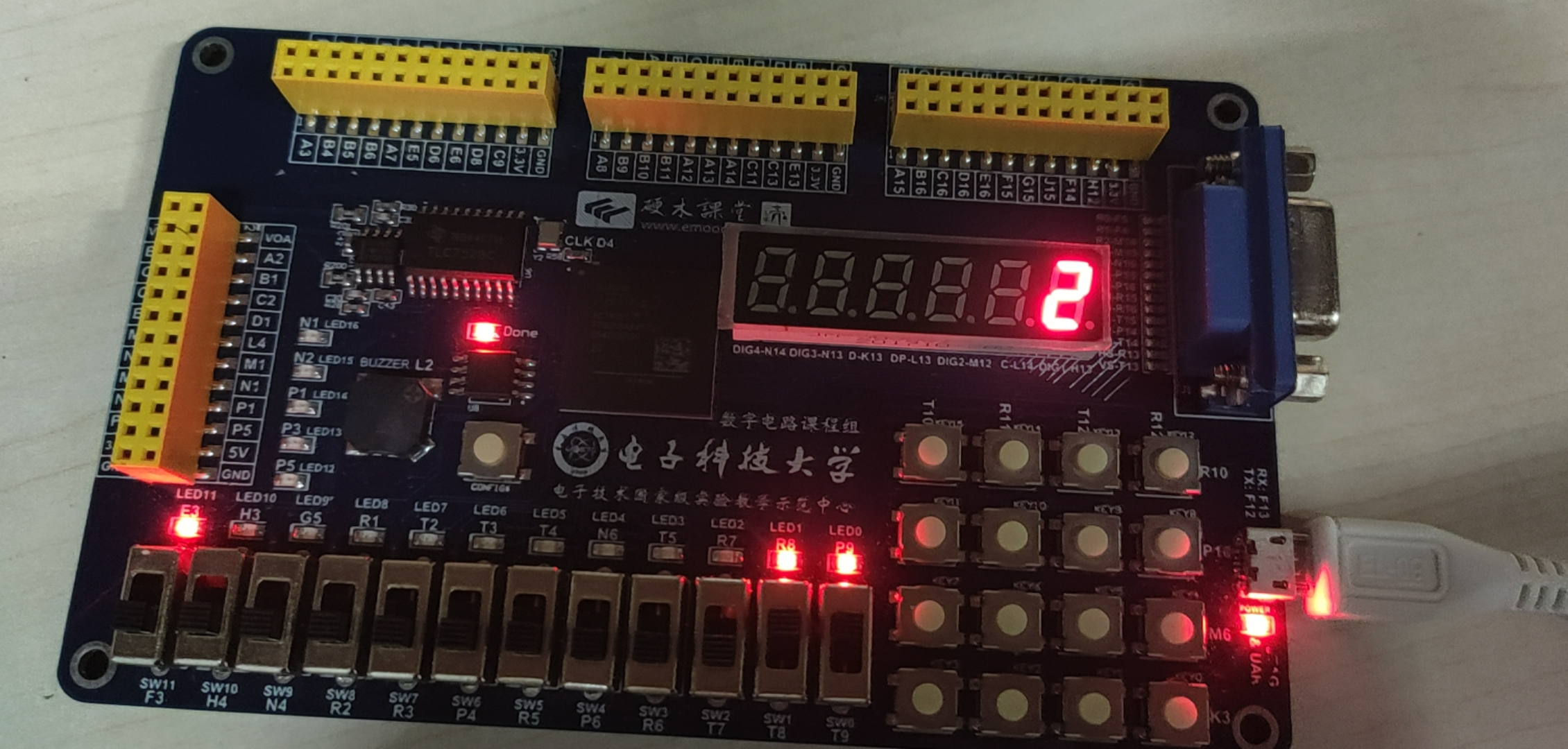

四、FPGA板上验证

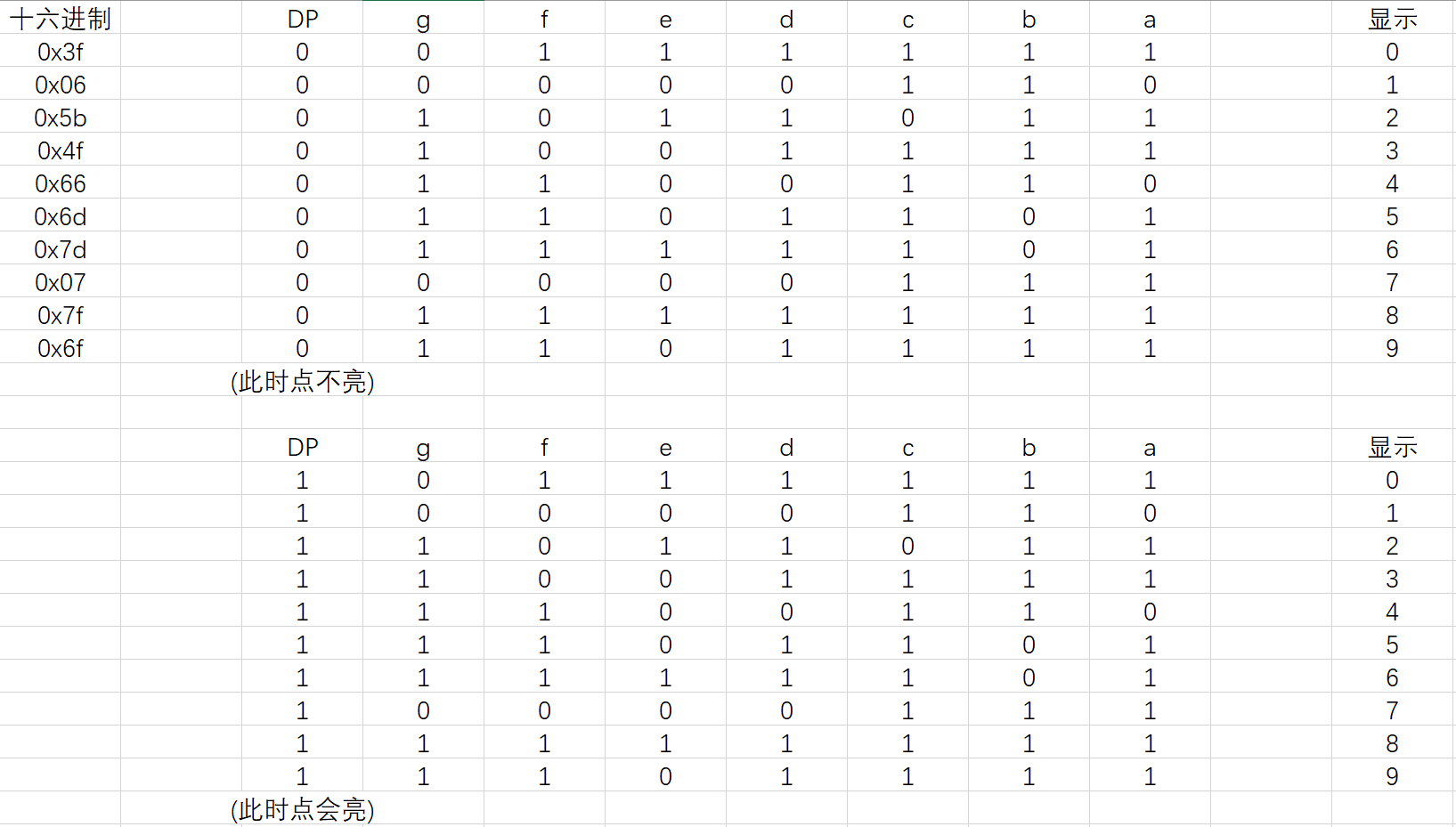

补充:数码管显示数字原理

![]()

其中,高位到低位依次是:DP_G F E _D C B A, 共阴极数码管——输入为高电平亮!

下图为,共阴极数码管的编码表

最后

以上就是动听花生最近收集整理的关于verilog实现三人表决器要求一、38译码器的实现并封装成IP核二、蜂鸣器的简易实现三、用封装好的38译码器IP核来实现三人表决器(自己添加的功能是:用数码管显示赞成人数,以及蜂鸣器提示投票开始或结束) 四、FPGA板上验证补充:数码管显示数字原理的全部内容,更多相关verilog实现三人表决器要求一、38译码器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复