1、基本概念

时序逻辑一般由锁存器、触发器、寄存器构成。

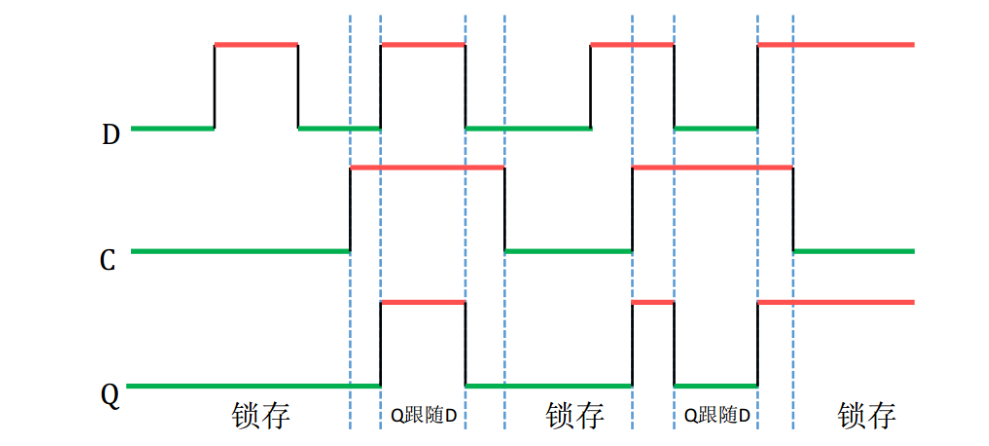

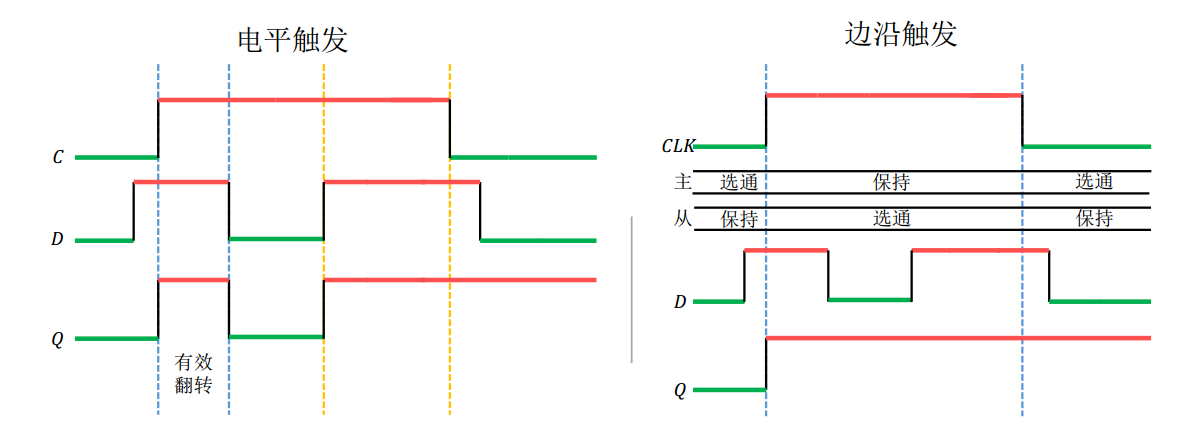

锁存器(latch):锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或使能信号)信号的电平值,即当锁存器处于使能状态时,输出才会随着数据的输入发生变化。

触发器(flipflop):触发器是边沿敏感的存储单元,数据存储的动作由某一信号的上升沿或下降沿进行同步的·。(钟控D触发器其实就是D锁存器,边沿触发器才是真正的D触发器)

寄存器(register):寄存器是用来暂时存放参与运算的数据与运算结果。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称之为寄存器。

2、区别

触发器和寄存器的区别:

由于触发器内由记忆功能,因此可以利用触发器方便的构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

从寄存数据的角度来讲,寄存器和锁存器的功能是相同的,他们的区别在于寄存器是同步时钟控制,而锁存器是电位信号控制。

3、详细介绍

(1)锁存器

锁存器是电平触发存储单元,锁存器的分类包括RS锁存器、门控RS锁存器和D锁存器,此处详细介绍D锁存器。

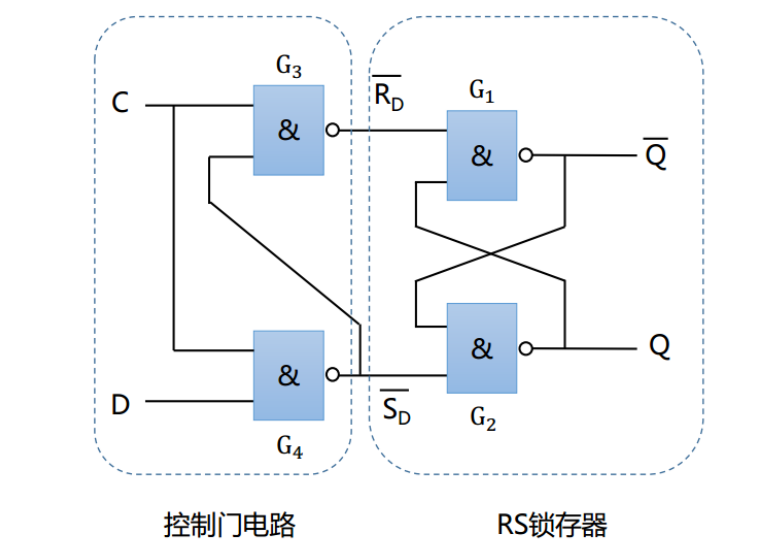

D锁存器的电路图主要由两部分组成,第一部分是由G1、G2两个与非门组成的RS锁存器,第二部分是由G3、G4两个与非门组成的控制电路。C为控制信号,用来控制G3、G4的激励输入。

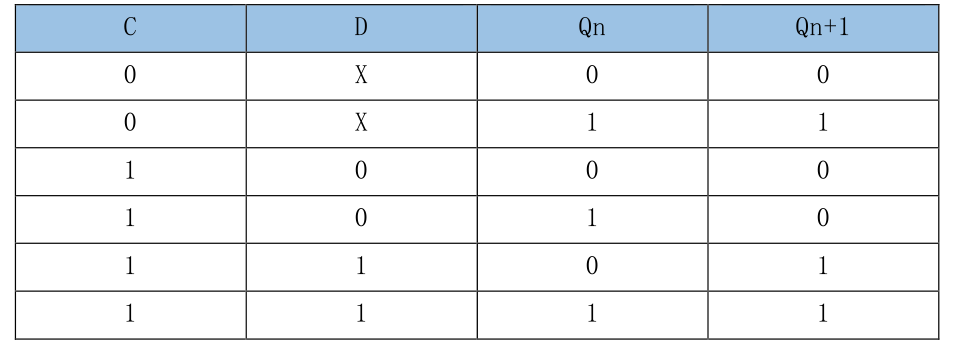

工作原理:当控制信号C等于0时,无论D输入什么信号,RD和SD的信号同时为1。根据与非门组成RS 锁存器的逻辑定律,RD和SD都同时等于1的话,锁存器的输出Q将维持原状不变。

当控制信号C等于1时,如果此时D=0,SD就等于1,RD就等于0,根据RS锁存器的逻辑规律,电路的结果就为0状态;如果D=1,那么RD就等于1,SD也就等于0,锁存器的结果就为1状态,也就是说此时的状态由激励输入端D来确定,并且D等于什么,锁存器的状态就是什么,这就是我们前面上所说的将单路数据D存入到锁存器之中。

当C为1时,D的状态和Qn+1的状态完全一样,当D=0时,Qn+1=0,当D=1时,Qn+1=1。

锁存器的坏处:锁存器最大的危害在于不能过滤毛刺和影响工具进行时序分析。在设计中要避免产生锁存器。

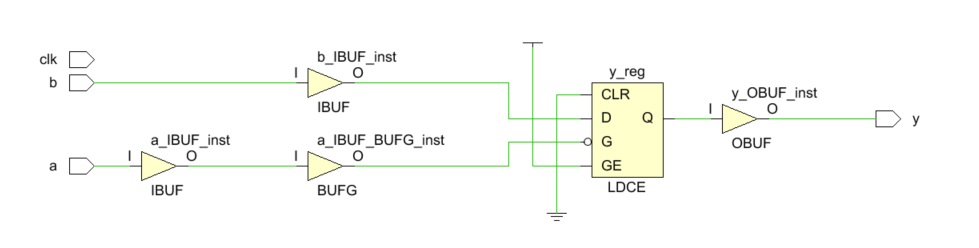

锁存器的产生原因:在组合逻辑中,if 或else语句不完整的描述,比如 if 缺少else分支,case缺少default分支,导致代码在综合过程中出现了latch。解决办法就是if 必须带else,case必须带default分支。(只有不带时钟的的always语句才如此)

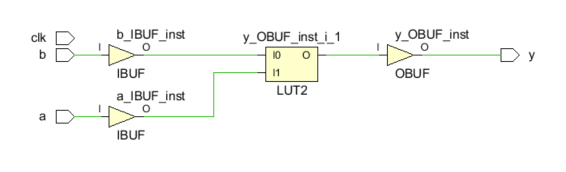

以不带default的case语句为例。

`timescale 1ns / 1ps

module case_latch(

input clk,

input a,

input b,

output reg y

);

always@(*)begin

case(a)

0:y=b;

endcase

end

endmodule

将case语句的default补充完整:

`timescale 1ns / 1ps

module case_latch(

input clk,

input a,

input b,

output reg y

);

always@(*)begin

case(a)

0:y=b;

default:y=0;

endcase

end

endmodule

(2)触发器

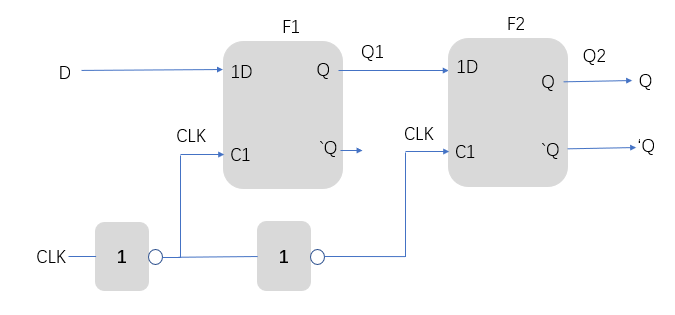

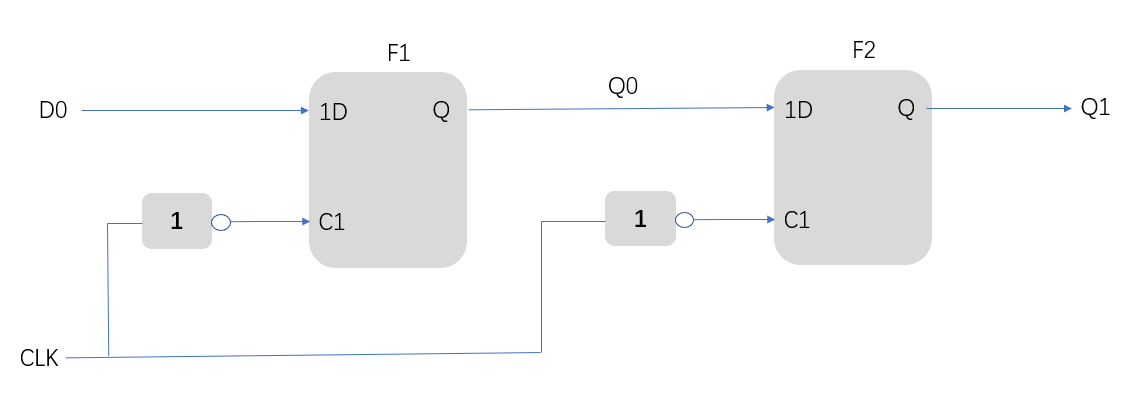

触发器是对脉冲边沿敏感的存储单元电路,它只在触发脉冲的上升沿(或下降沿)瞬间改变其状态。触发器一般包括RS触发器、JK触发器、D触发器、T触发器、T'触发器,实际应用中一般使用D触发器。D触发器的电路图如下图所示。

D触发器是由两个相同的D锁存器以及两个非门连接而成,F1为主锁存器,F2为从锁存器,两个锁存器的控制信号都是由外部时钟信号CLK提供。当时钟CLK=0时,F1选通,F2锁存,当CLK=1时,F1锁存,F2选通。CLK从0到1这样的一个变化周期内,触发器的输出状态只可能改变一次。

D触发器和D锁存器的功能是一样的,只不过触发方式不同。

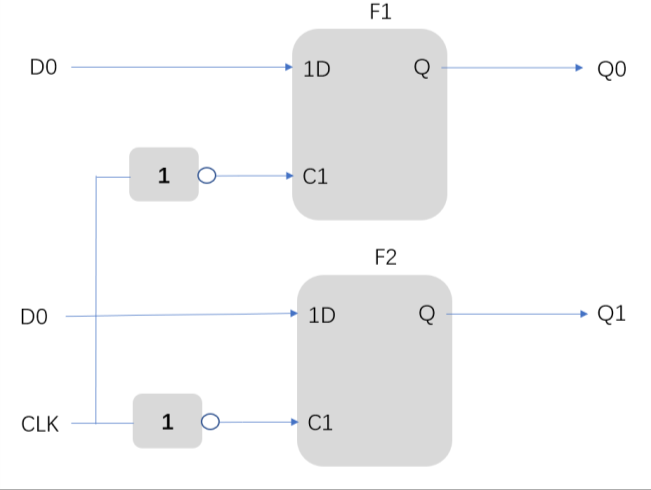

(3)寄存器

寄存器是由多个触发器构成的,因此可以存储多bit二进制的数据。寄存器包括触发器并联和触发器串联两种。

触发器并联:

触发器串联:

最后

以上就是丰富月亮最近收集整理的关于时序逻辑中的锁存器、触发器、寄存器的全部内容,更多相关时序逻辑中内容请搜索靠谱客的其他文章。

![[转]触发器-锁存器-亚稳态](https://www.shuijiaxian.com/files_image/reation/bcimg10.png)

发表评论 取消回复