1. 设计要求:

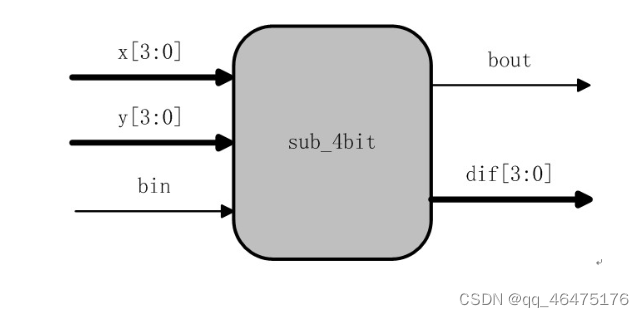

设计一个4位减法器,采用结构化设计。该设计名为sub_4bit,其顶层设计如下图所示,有三个输入量:被减数x[3:0],减数y[3:0],低位向本位的借位bin;有两个输出量本位差dif[3:0],本位向高位的借位bout。数学表达式为:(x + bout) – y – bin = diff

2. 设计实现

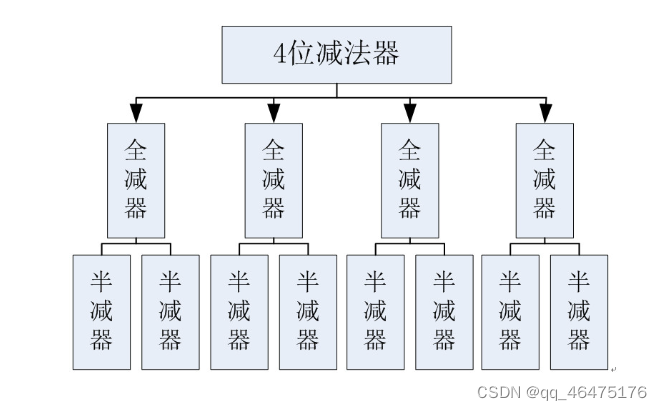

4位减法器由四个全减器构成,1位全减器由两个半减器和1个或门构成,如下图所示。

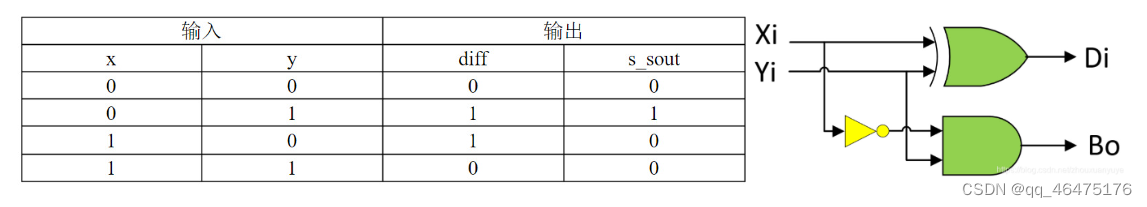

(1) 半减器:

半减器用于计算两个二进制数x和y的剑法,输出结果d和向高位的借位bo,没有考虑低位向本位的借位。

(2) 全减器

全加器有三个输入量:被减数Ai,减数Bi,低位向本位的借位Ci-1;有两个输出量本位差Si,本位向高位的借位Ci。其真值表如下所示:

最后

以上就是大胆小懒猪最近收集整理的关于基于FPGA的4位减法器设计及仿真代码的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复