不同功能D触发器的Verilog描述

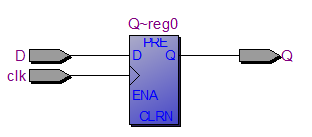

1.D触发器(本文都为上升沿触发、异步都为低复位、置数都为高)

module flip_flop(

input clk,

input D,

output reg Q

);

always@(posedge clk)

Q<=D;

endmodule

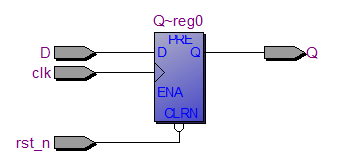

2.异步复位D触发器

module flip_flop(

input clk,

input rst_n,

input D,

output reg Q

);

always@(posedge clk or negedge rst_n)

begin

if(rst_n==1’b0)

Q<=1’b0;

else

Q<=D;

end

endmodule

异步复位D触发器RTL视图

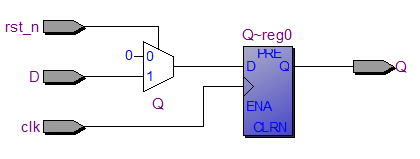

3.同步复位D触发器

module flip_flop(

input clk,

input rst_n,

input D,

output reg Q

);

always@(posedge clk )

begin

if(rst_n==1’b0)

Q<=1’b0;

else

Q<=D;

end

endmodule

同步复位D触发器RTL视图

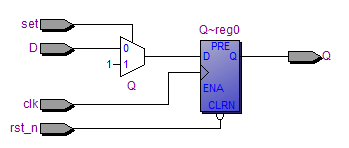

4.异步复位、同步置数

module flip_flop(

input clk,

input rst_n,

input set,

input D,

output reg Q

);

always@(posedge clk or negedge rst_n)

begin

if(rst_n==1’b0)

Q<=1’b0;

else if(set) //

Q<=1’b1;

else

Q<=D;

end

endmodule

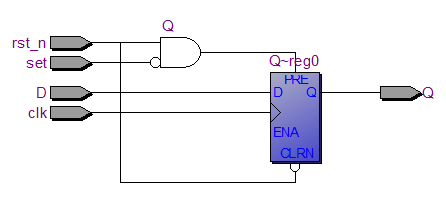

异步复位、同步置数RTL视图

5.异步复位、异步置数

module flip_flop(

input clk,

input rst_n,

input set,

input D,

output reg Q

);

always@(posedge clk or negedge rst_n or negedge set)

begin

if(rst_n==1’b0)

Q<=1’b0;

else if(~set)

Q<=1’b1;

else

Q<=D;

end

endmodule

异步复位、异步置数RTL视图

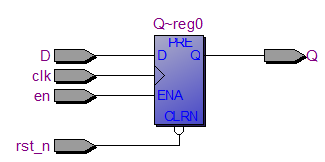

6.异步复位、时钟使能D触发器

module flip_flop(

input clk,

input rst_n,

input en,

input D,

output reg Q

);

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)

Q<=1’b0;

else if(en)

Q<=D;

end

endmodule

最后

以上就是沉静哑铃最近收集整理的关于不同功能D触发器的Verilog描述的全部内容,更多相关不同功能D触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复