第七课 Introduction to physical data

why use physical data?

- wire load model

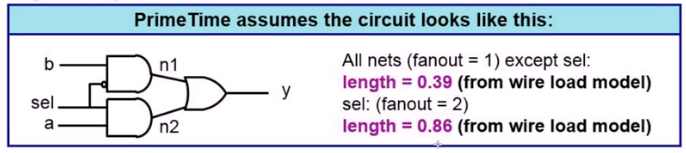

在逻辑层面(pre-layout),PT软件中的时序模型如下所示:

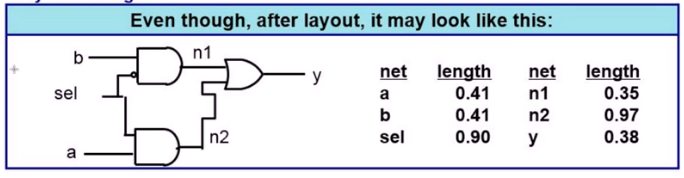

实际布线后的时序模型如下所示:

可以看到布局布线的方式会影响到很多物理参数。

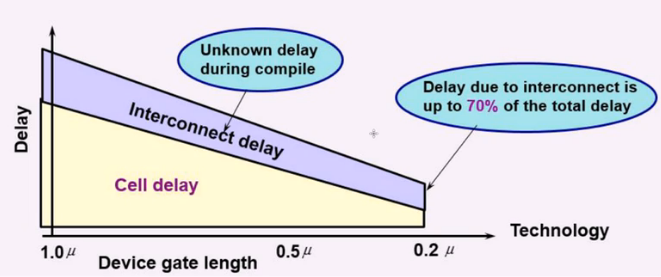

基本单元的延迟和连线延迟的占比会根据工艺大小变化:

在目前的工艺水平下,连线延迟占到了70%以上。 因此对连线延迟的准确性要求很高。

introduction to physical data

- parasitic versus SDF

物理参数分为两种:一种是用电容电阻表示的寄生参数,一种是用sdf文件表示的延时信息。

sdf文件的计算更快,它的优先级比寄生参数高。

读入的顺序:

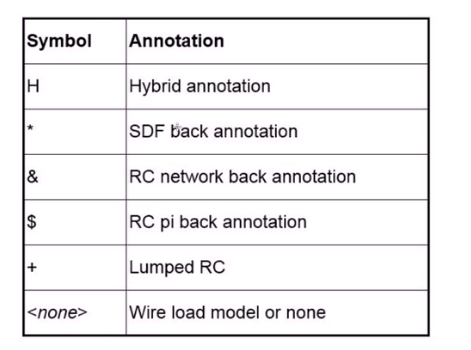

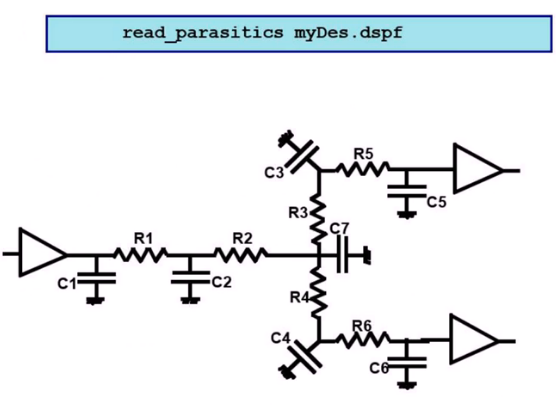

report_timing时也可用特定的符号表示到底用了哪种模型:

#sdf文件

read_sdf

report/remove_annotated_delay

report/remove_annotated_check

#寄生参数

read_parasitics

report/remove_annotated_parasitics

- parasitic back-annotation

1.set_load/set_resistance:集总RC模型

优点:简单,只有一个电阻和电容

缺点:应用范围窄,准确性低,模型悲观

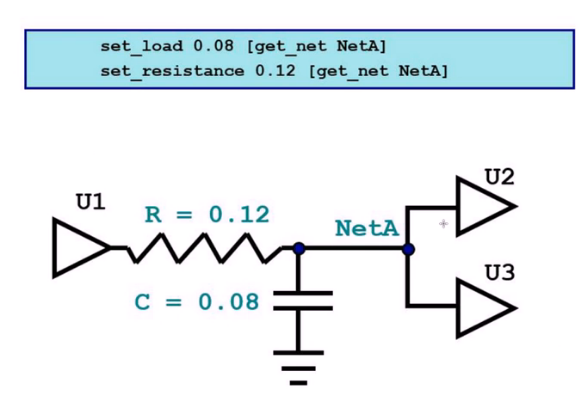

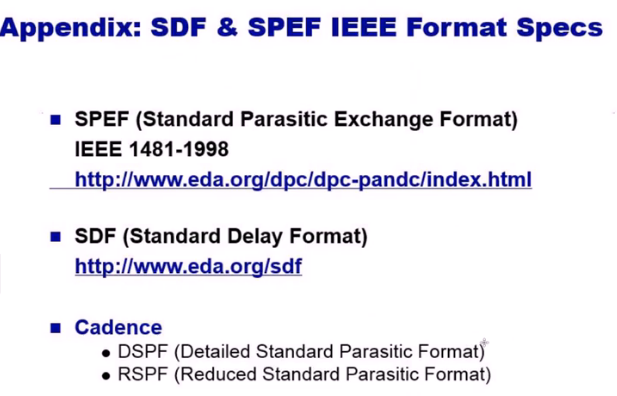

2.RSPF——reduced parasitic exchange format

RSPF(π模型)比集总模型更准确,用Cnear和Cfar模拟不同的情况

缺点:没有反映出拓扑结构

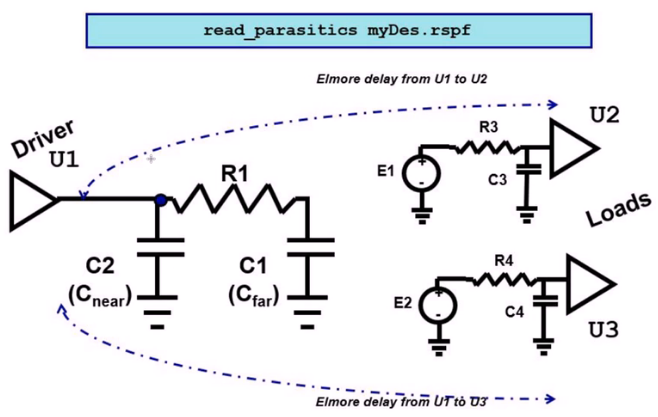

3.DSPF——detailed parasitic exchange format

(2、3都是cadence软件的格式)

反映出了拓扑结构,但是会消耗大量的计算资源

4.SPEF——standard parasitic exchange format(IEEE标准格式)

Resolve some back-annotation issues

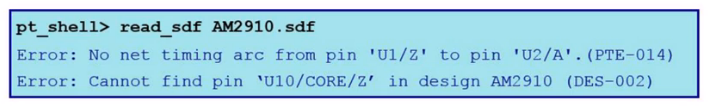

知道该如何处理在STA过程中出现的错误

- 出现时序信息的错误或者缺失

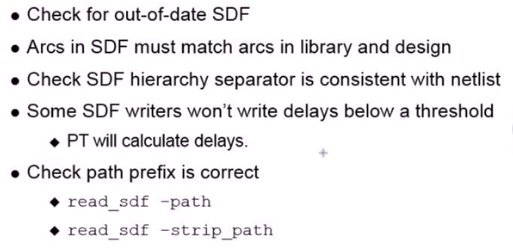

检查方式:1.看是否和上一个版本的sdf是否一致 2.设计本身是否存在问题 3.如果都没有问题则可以让PT忽略错误。

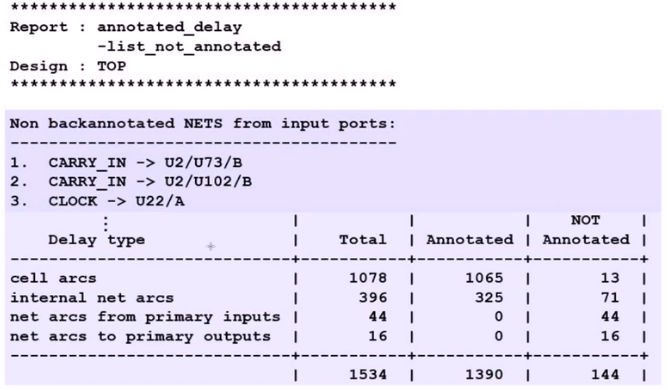

可以用以下的命令显示缺失信息的路径有哪些:

report_annotated_delay -list_not_annotated

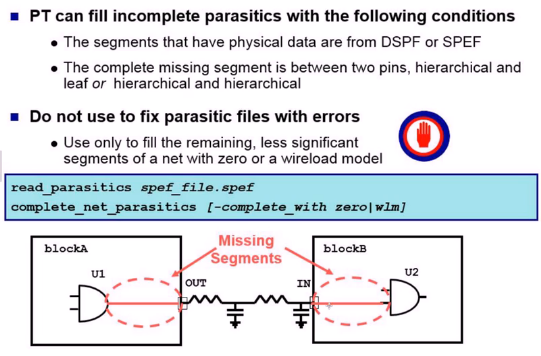

对于无法忽略的缺失,可以手动补充寄生参数,或者从线载模型计算出时序信息:

补充

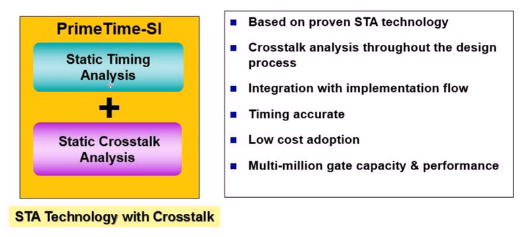

之前的学习内容中一直没有考虑细节的问题,比如噪声。Primetime-SI除了静态时序分析,还可以考虑串扰问题。

180nm以下的工艺会经常用到,只有PT和PT-SI的分析都满足时序要求才算电路通过。

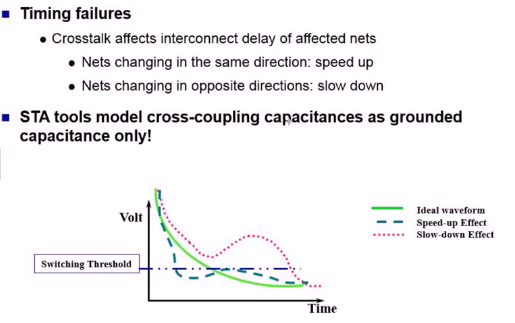

信号的串扰来源主要有:1.平行长导线 2.寄生电容 3.高频开关,被串扰的信号会出现噪声、毛刺以及延迟的不确定。

时序文件的参考信息:

最后

以上就是耍酷小白菜最近收集整理的关于PT静态时序分析 第七课的全部内容,更多相关PT静态时序分析内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复