一、TCL语言

1. TCL概述

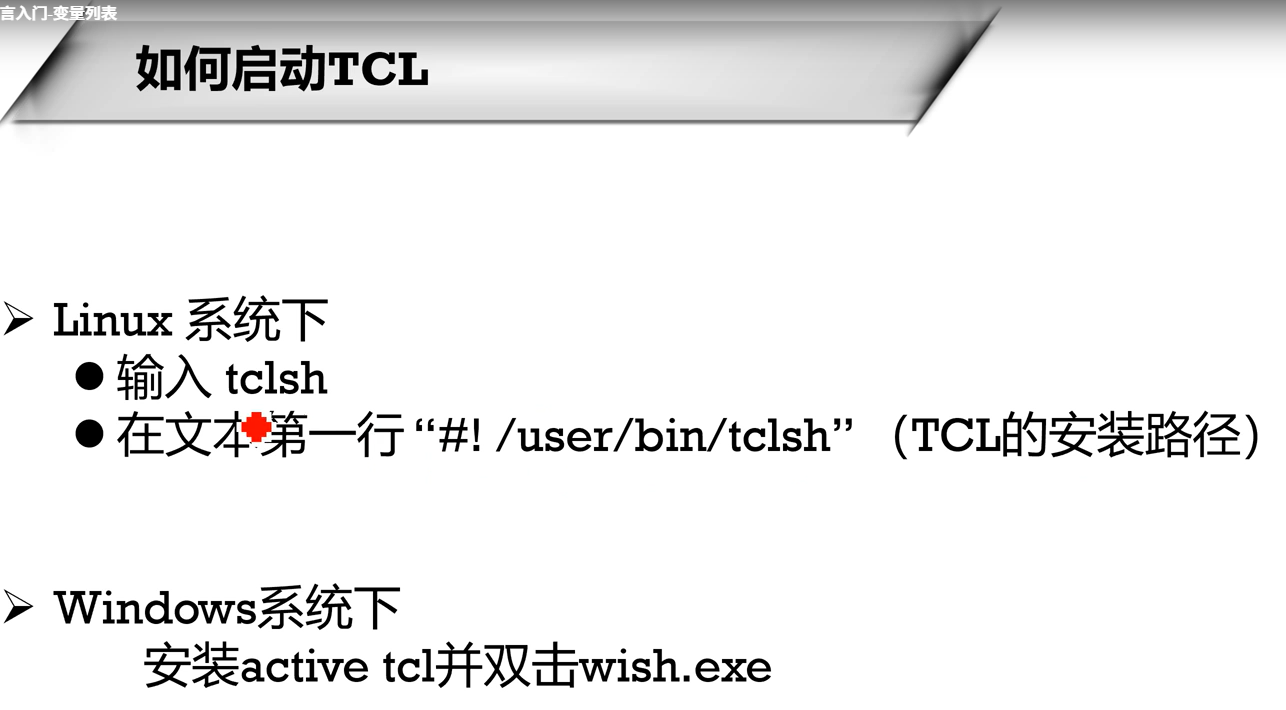

1.1 启动TCL

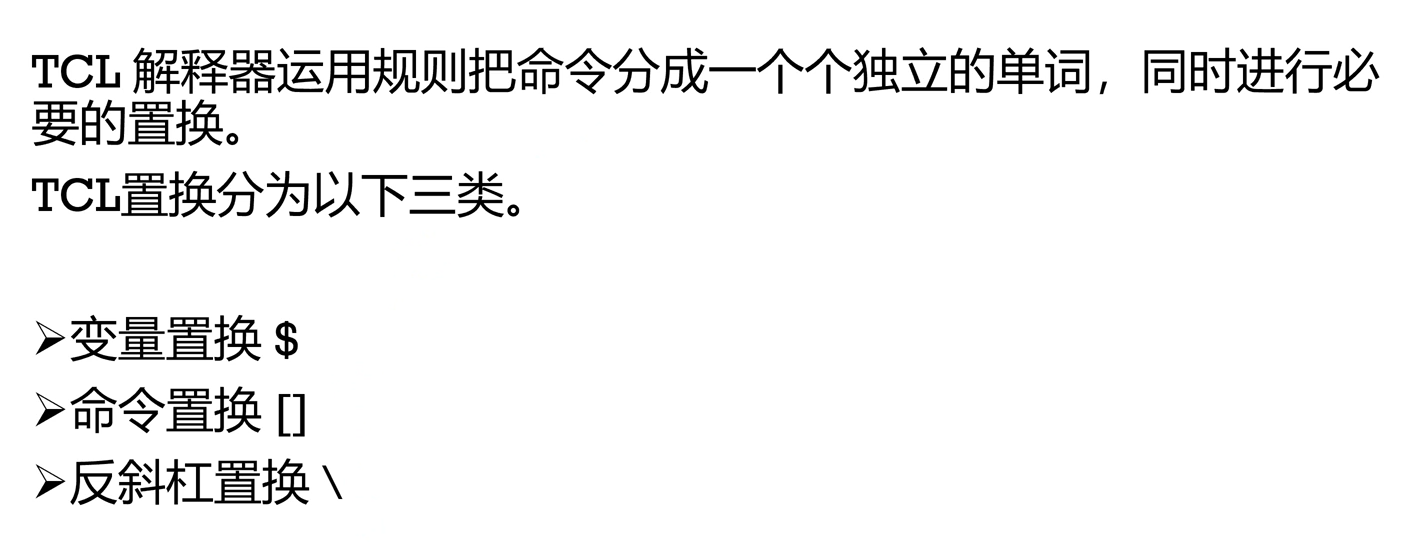

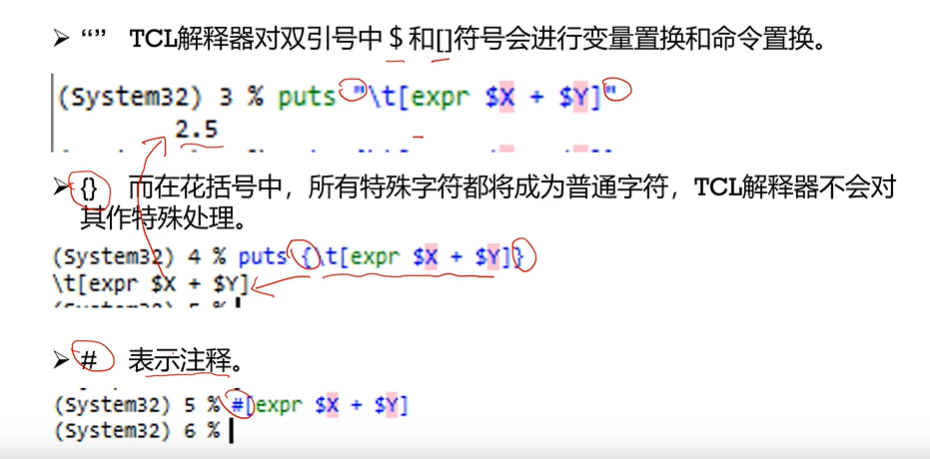

1.2 置换

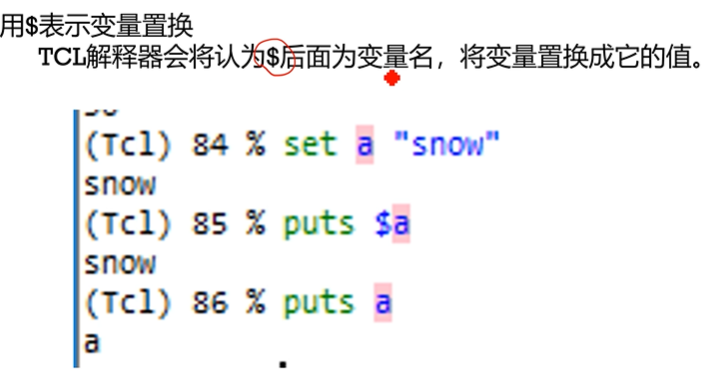

1.2.1 变量置换

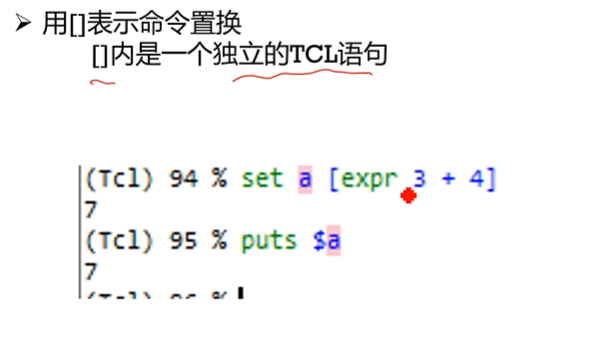

1.2.2 命令置换

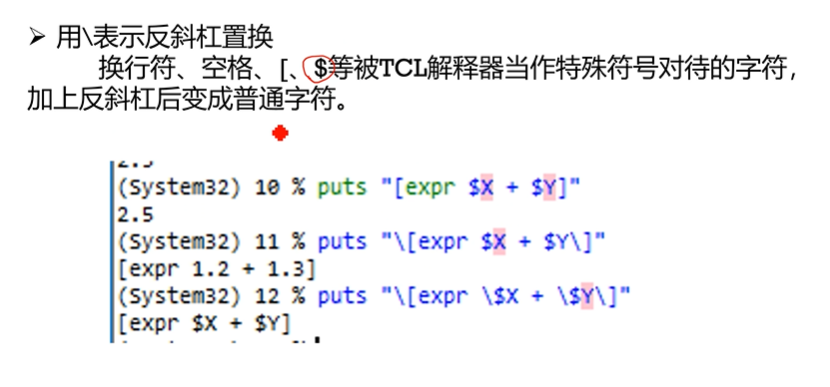

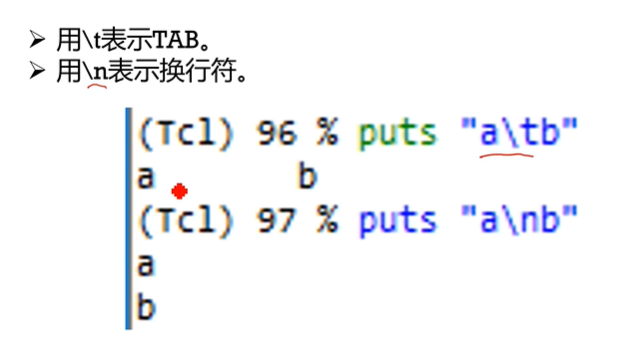

1.2.3 反斜杠置换

1.3 变量、数组和列表

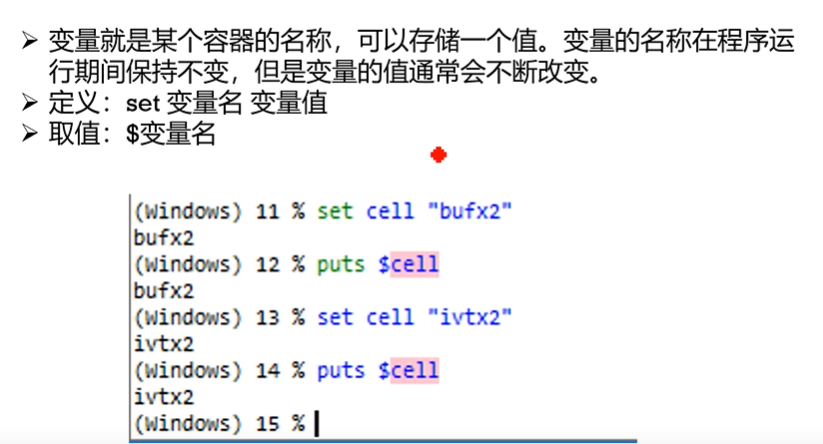

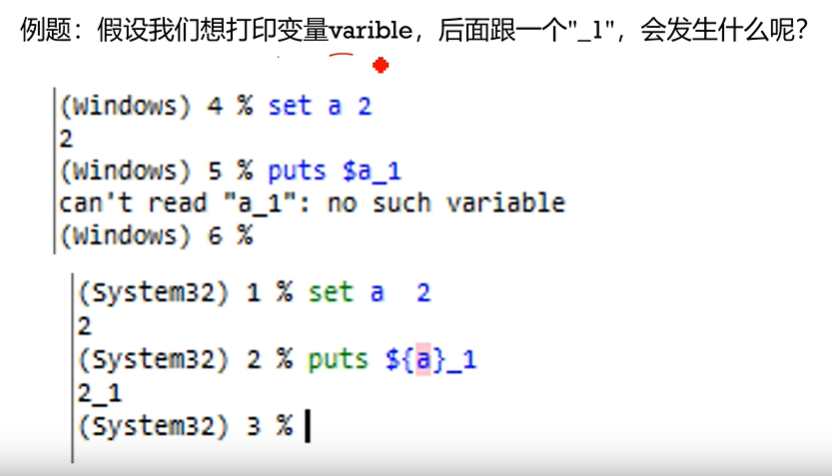

1.3.1 变量

脚本语言的变量可以存储字符串,这是脚本语言的便利

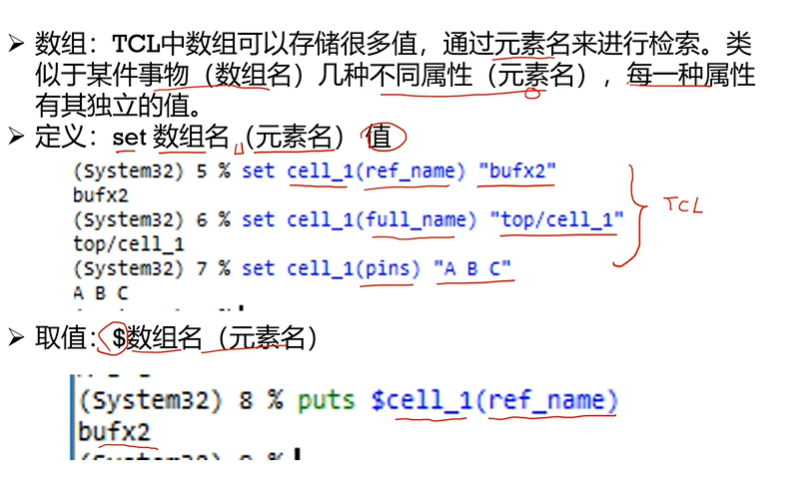

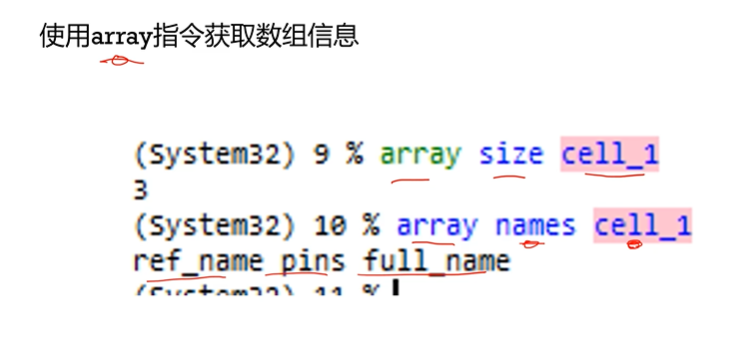

1.3.1 数组

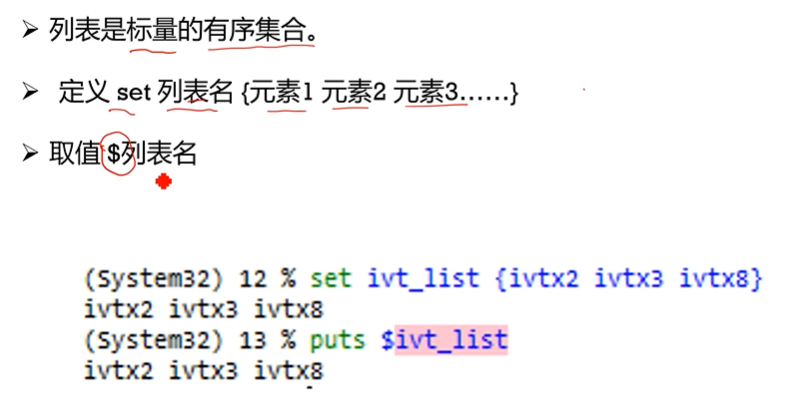

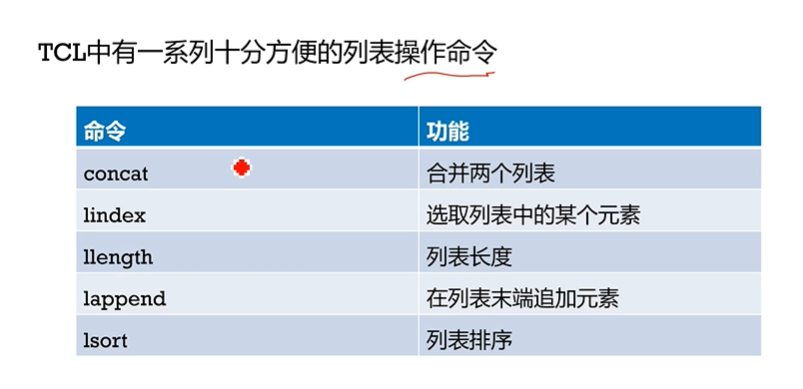

1.3.3 列表

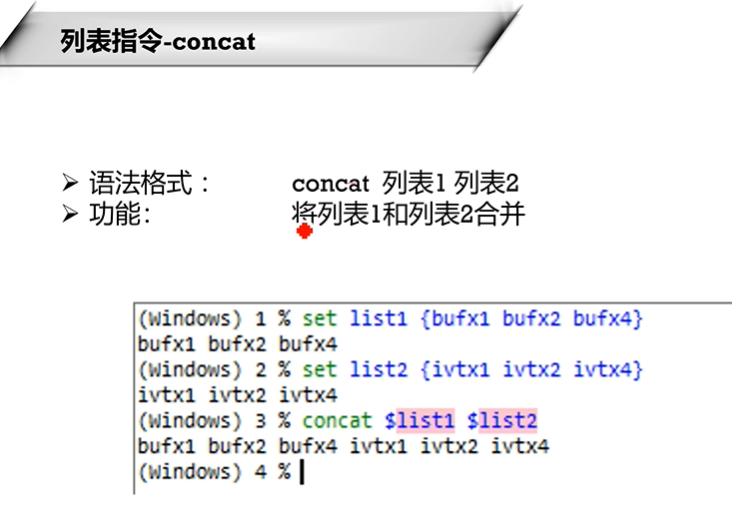

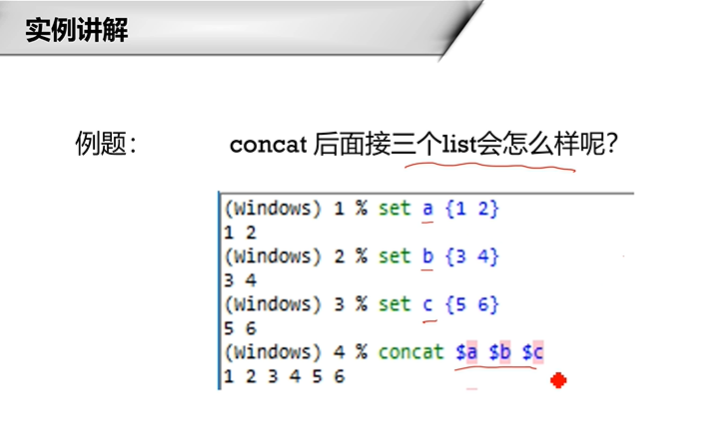

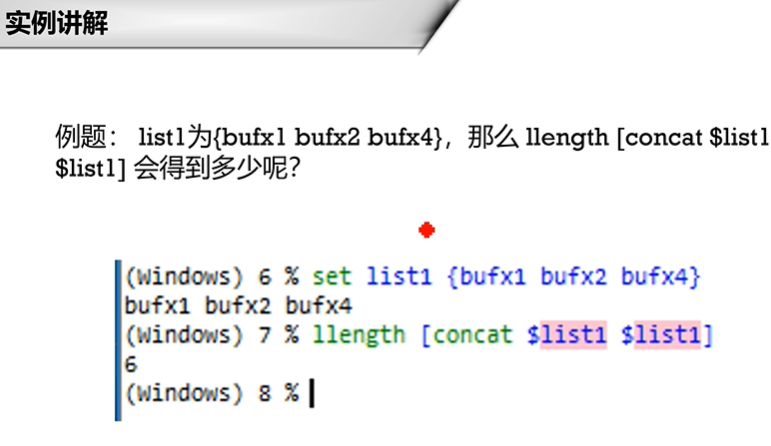

1)列表指令-concat(合并)

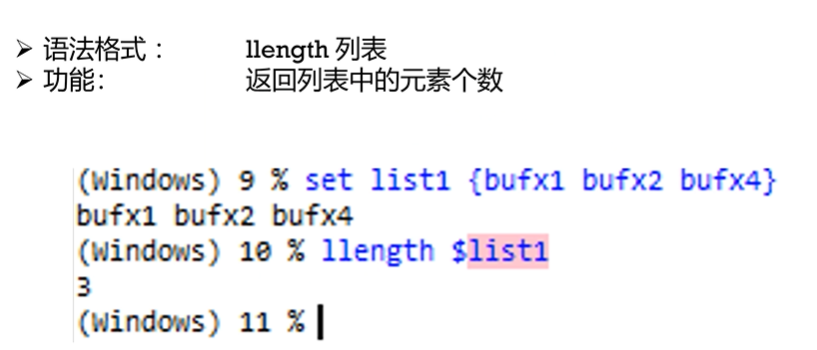

2)列表指令-llength(返回元素个数)

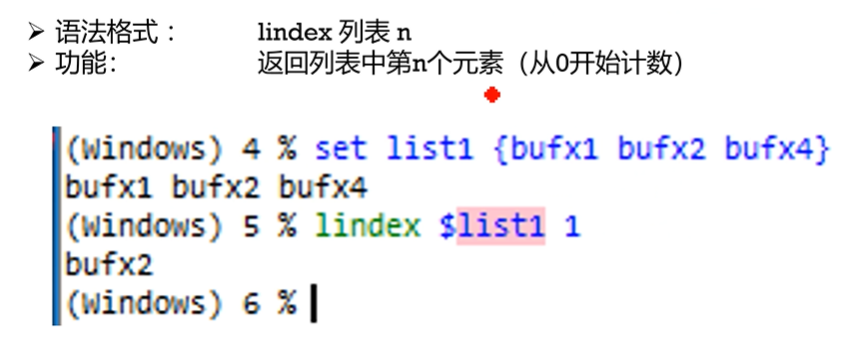

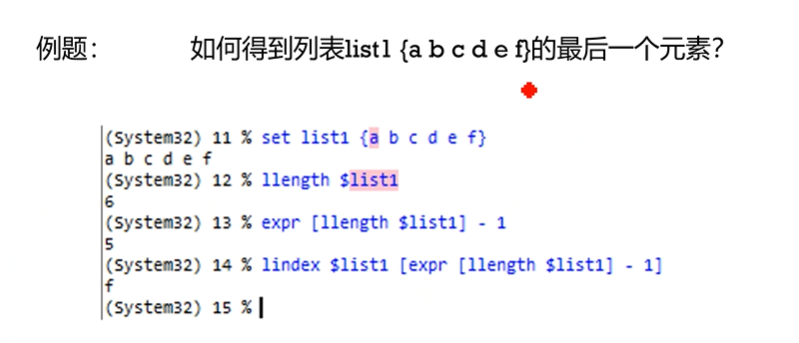

3)列表指令-lindex(返回第n个元素)

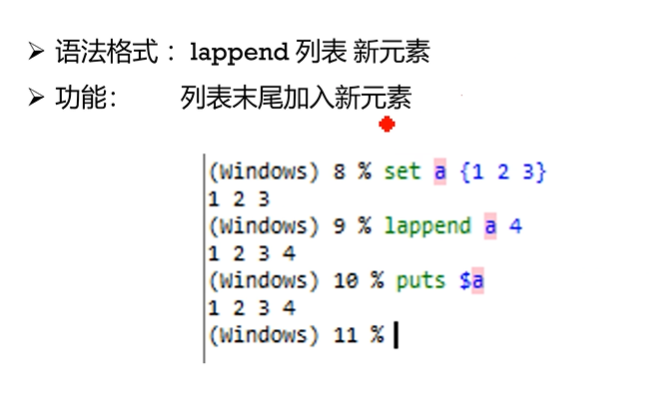

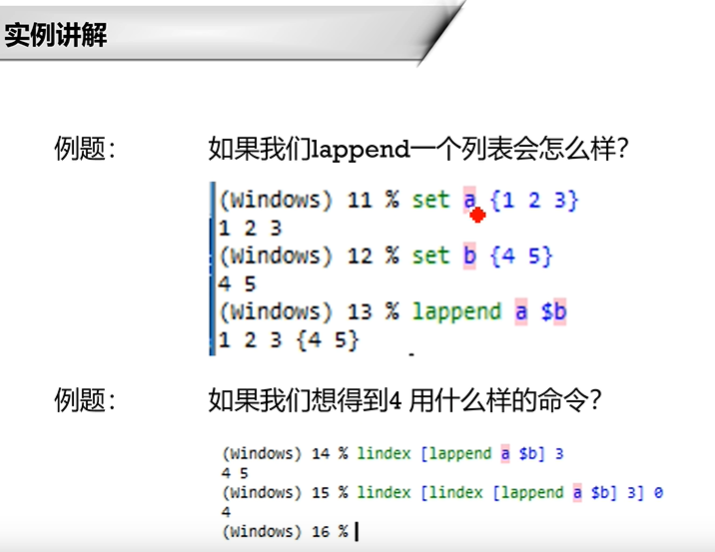

4)列表指令-lappend(列表末尾加新元素)

此处是将b当作了一个元素,值为{4 5}

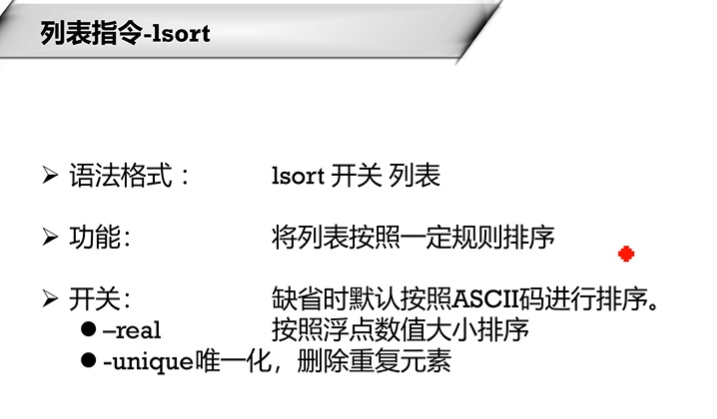

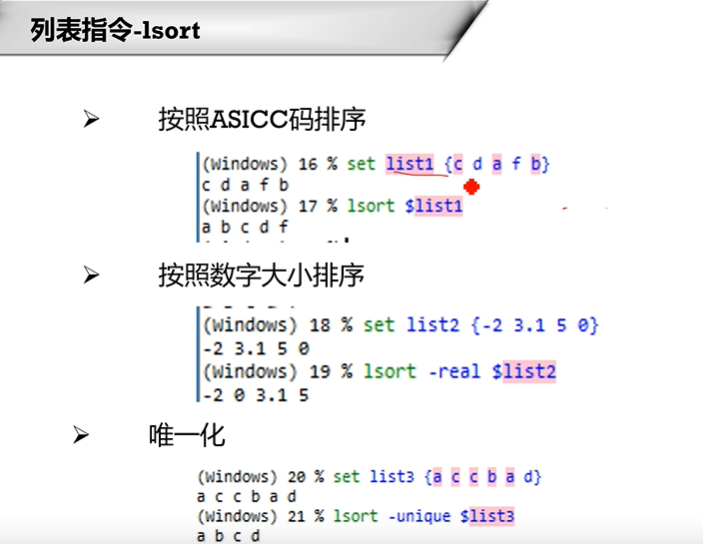

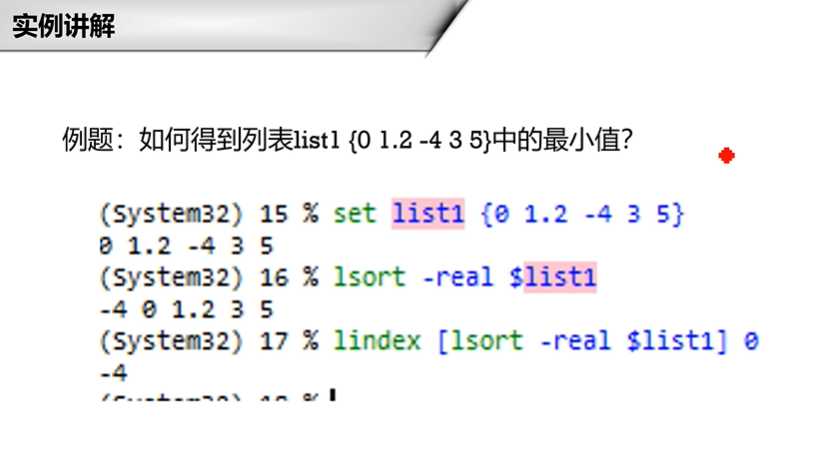

5)列表指令-lsort(列表排序)

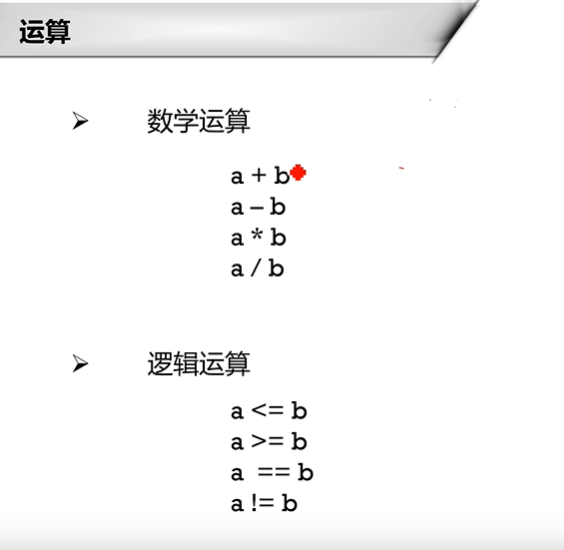

1.4 运算

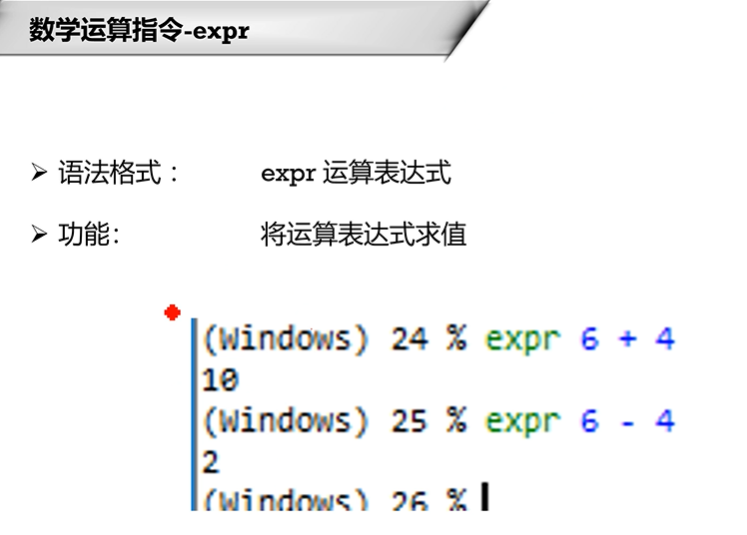

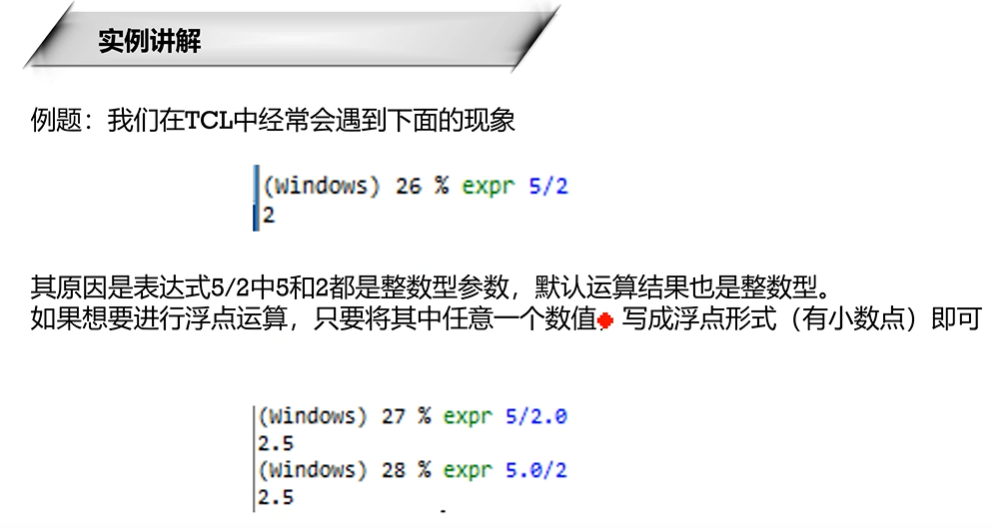

1.4.1 数学运算指令 -expr

2. 控制流

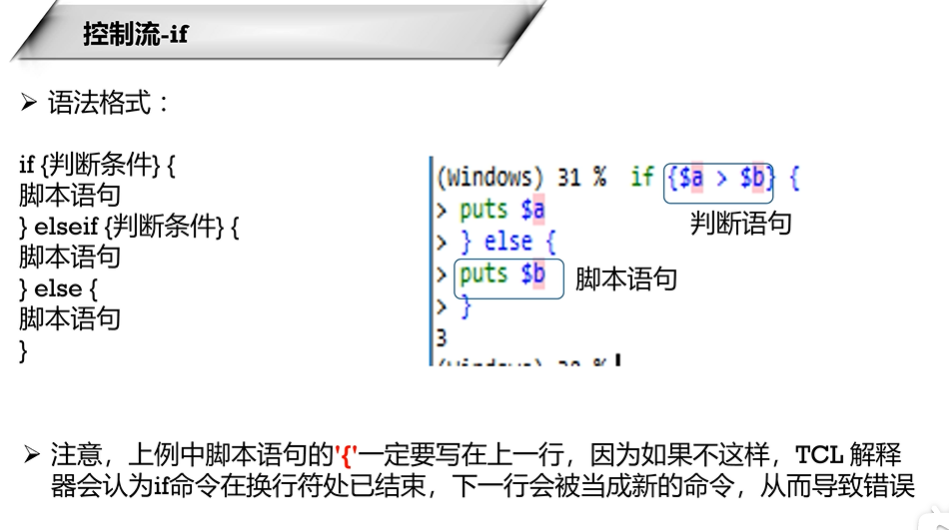

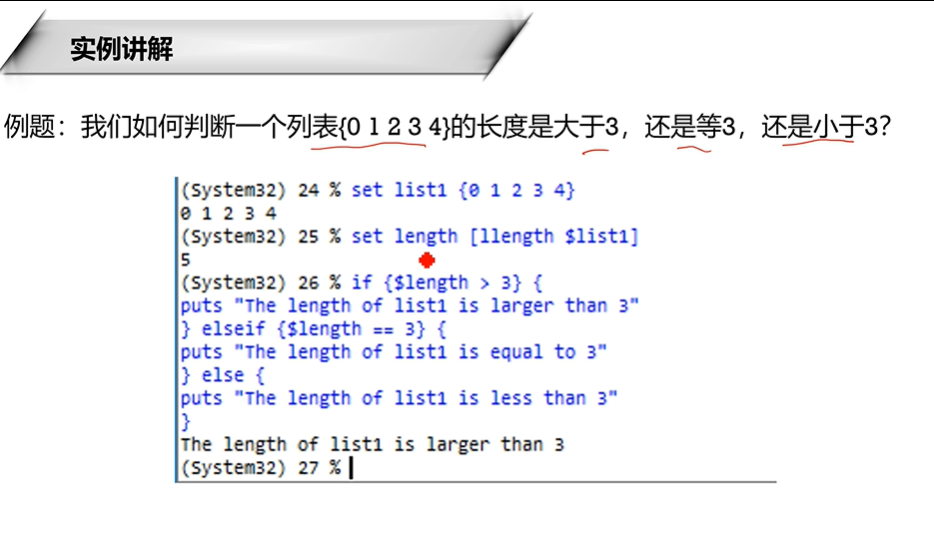

2.1 控制流 -if

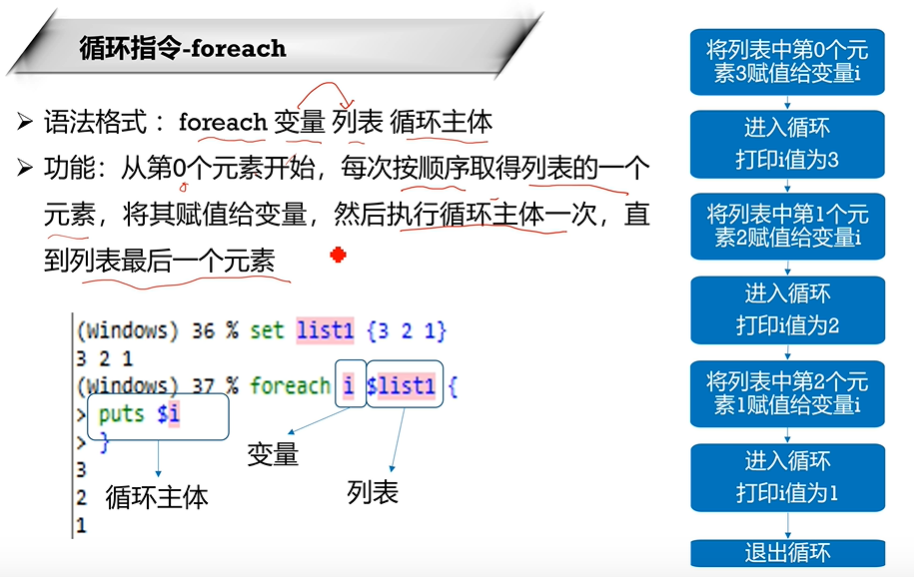

2.2 循环指令 -foreach

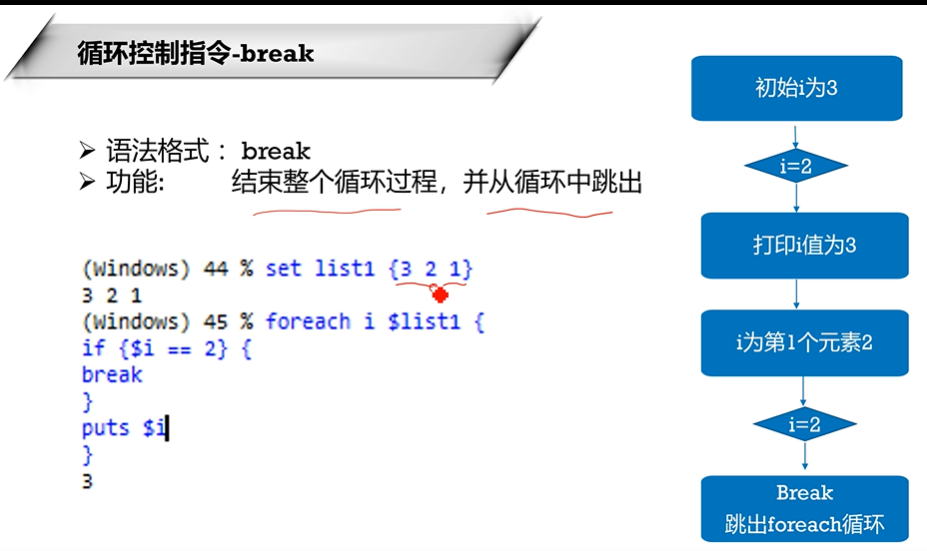

3.3 循环控制指令 -break

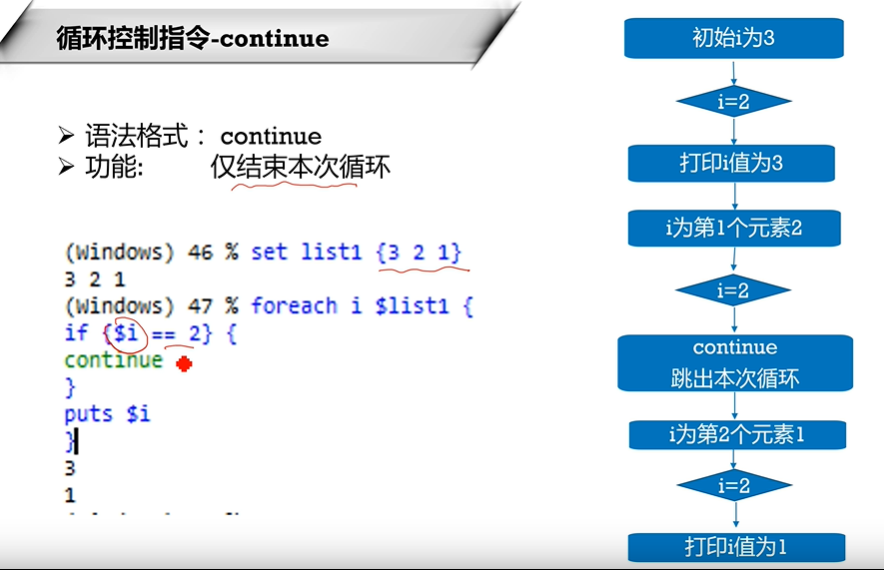

3.4 循环控制指令 -continue

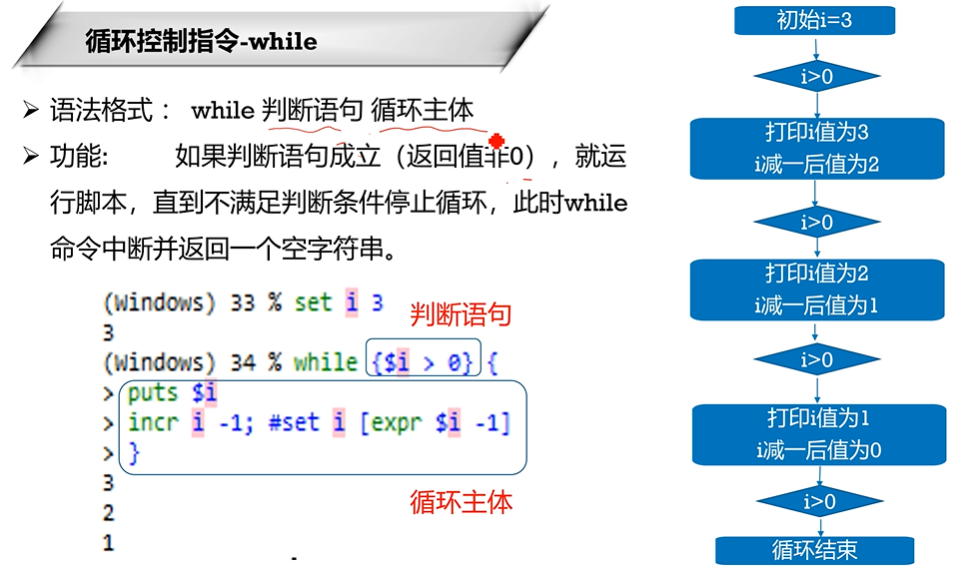

3.5 循环控制指令 -while

注意#是注释

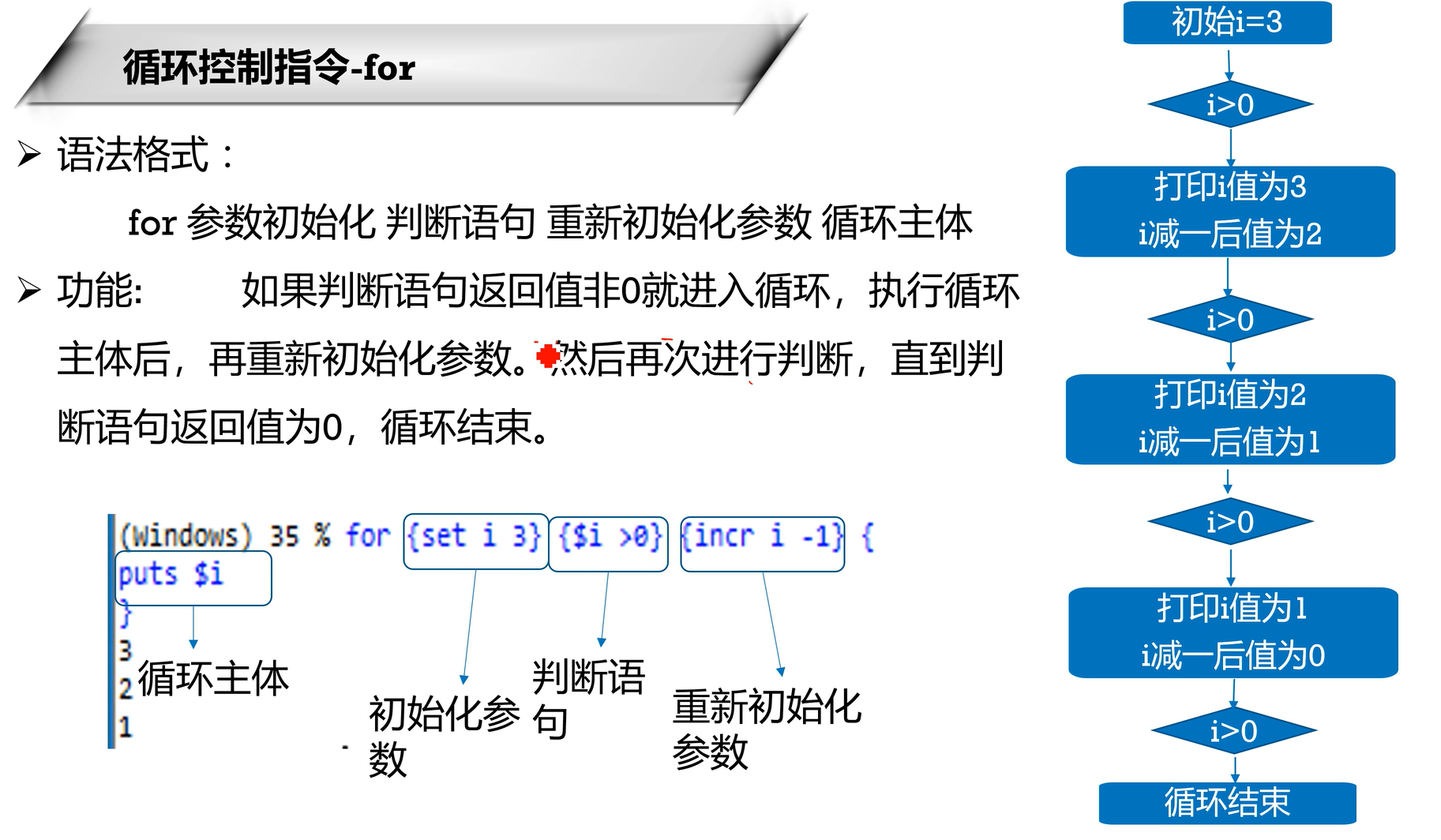

3.6 循环控制指令 -for

3. 过程函数

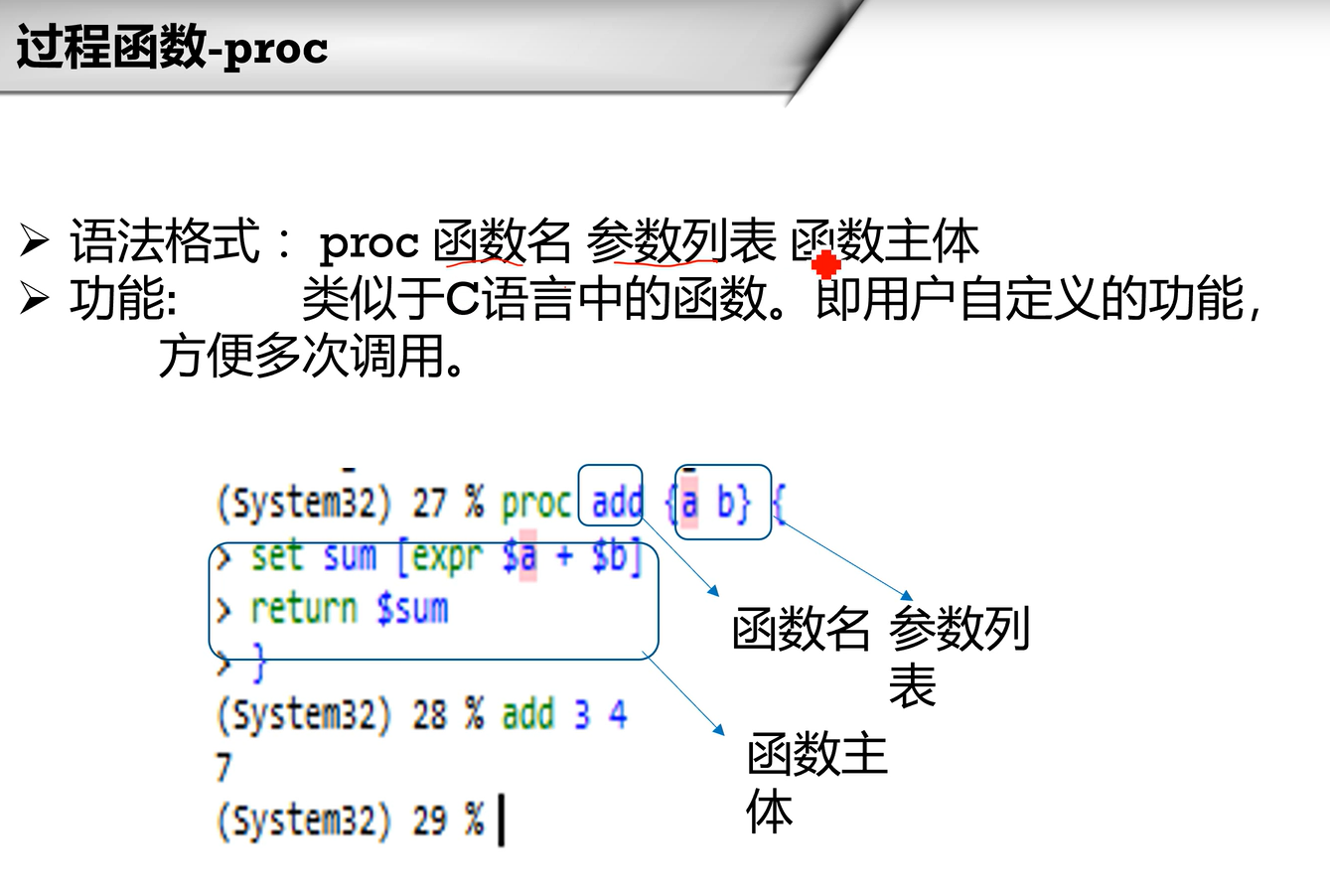

3.1 -proc

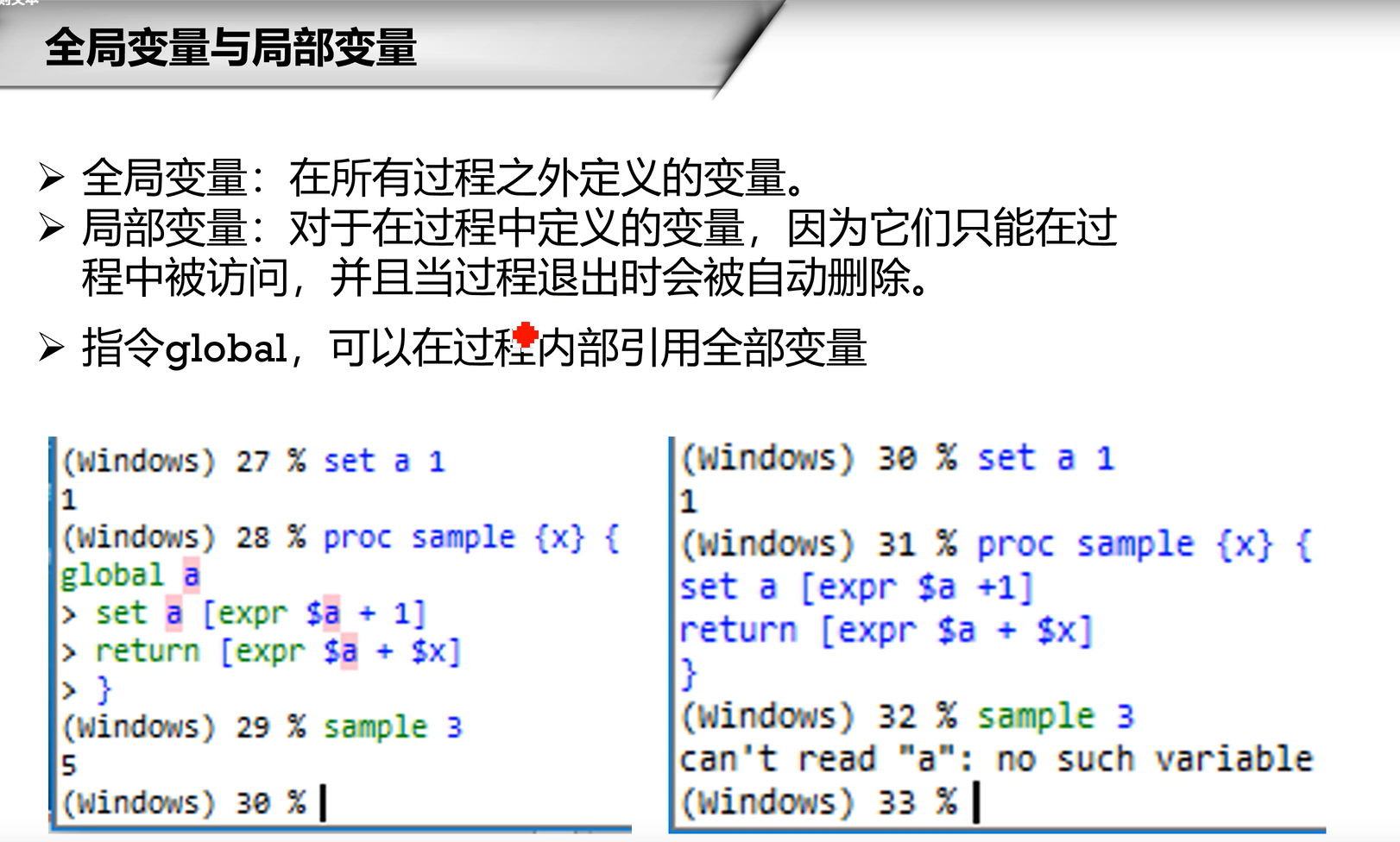

3.2 全局与局部变量

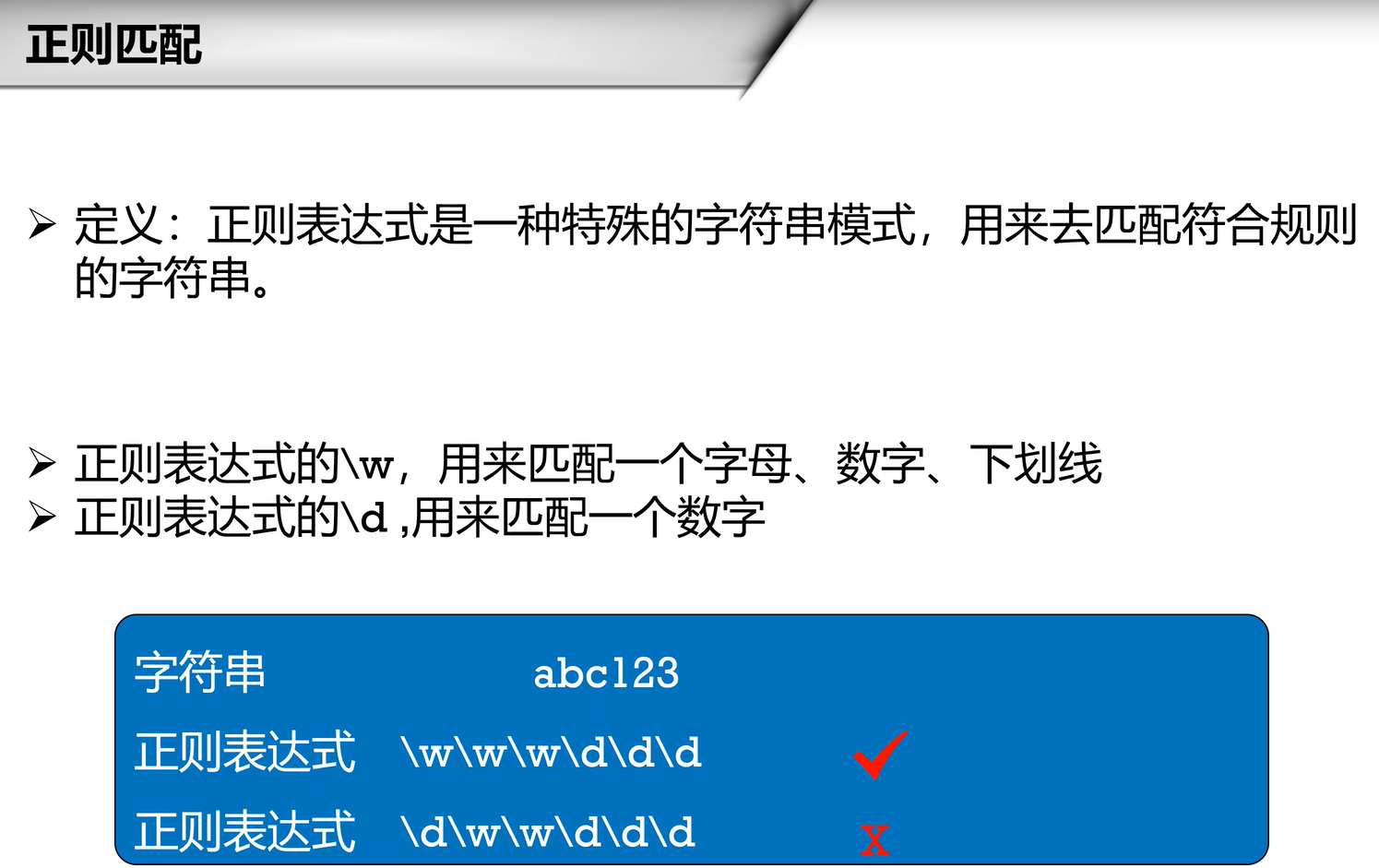

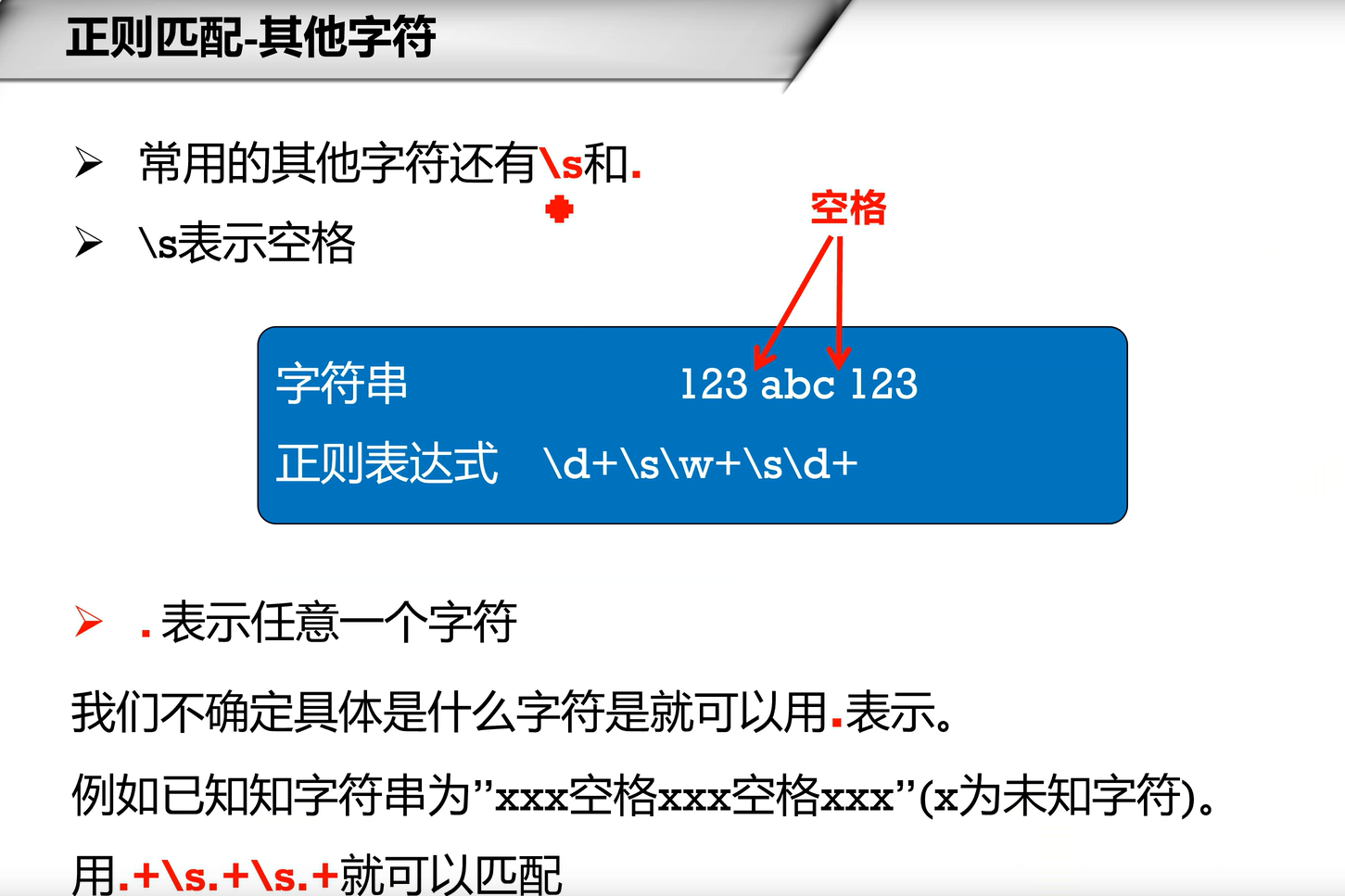

4. 正则匹配

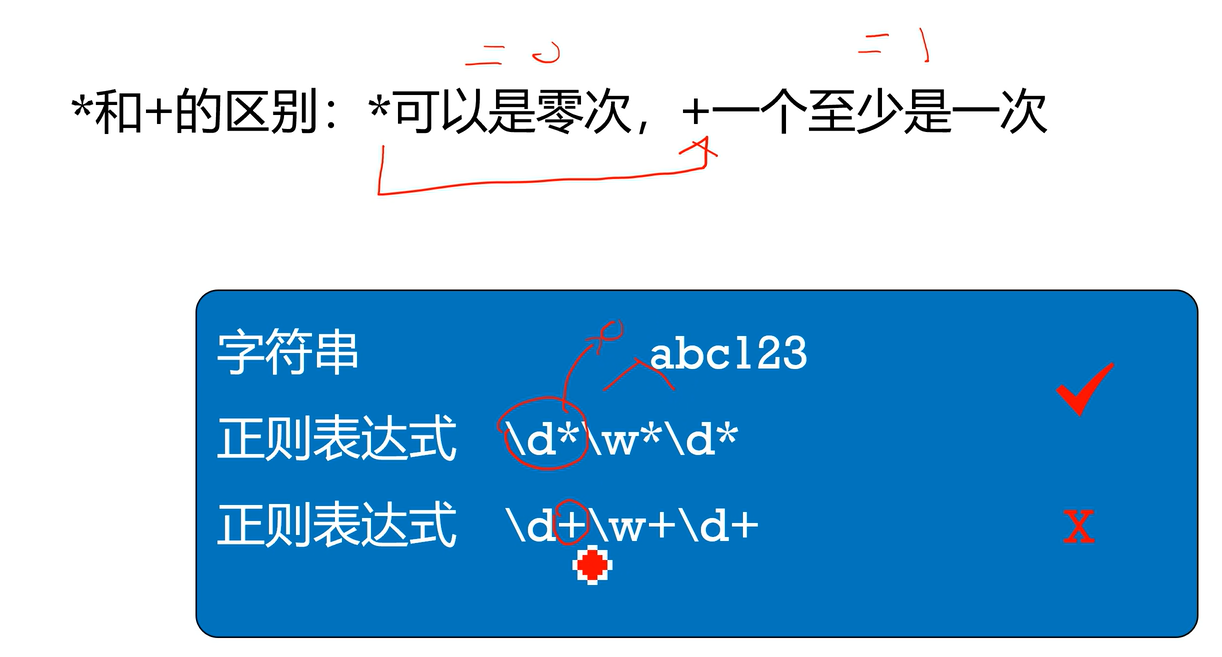

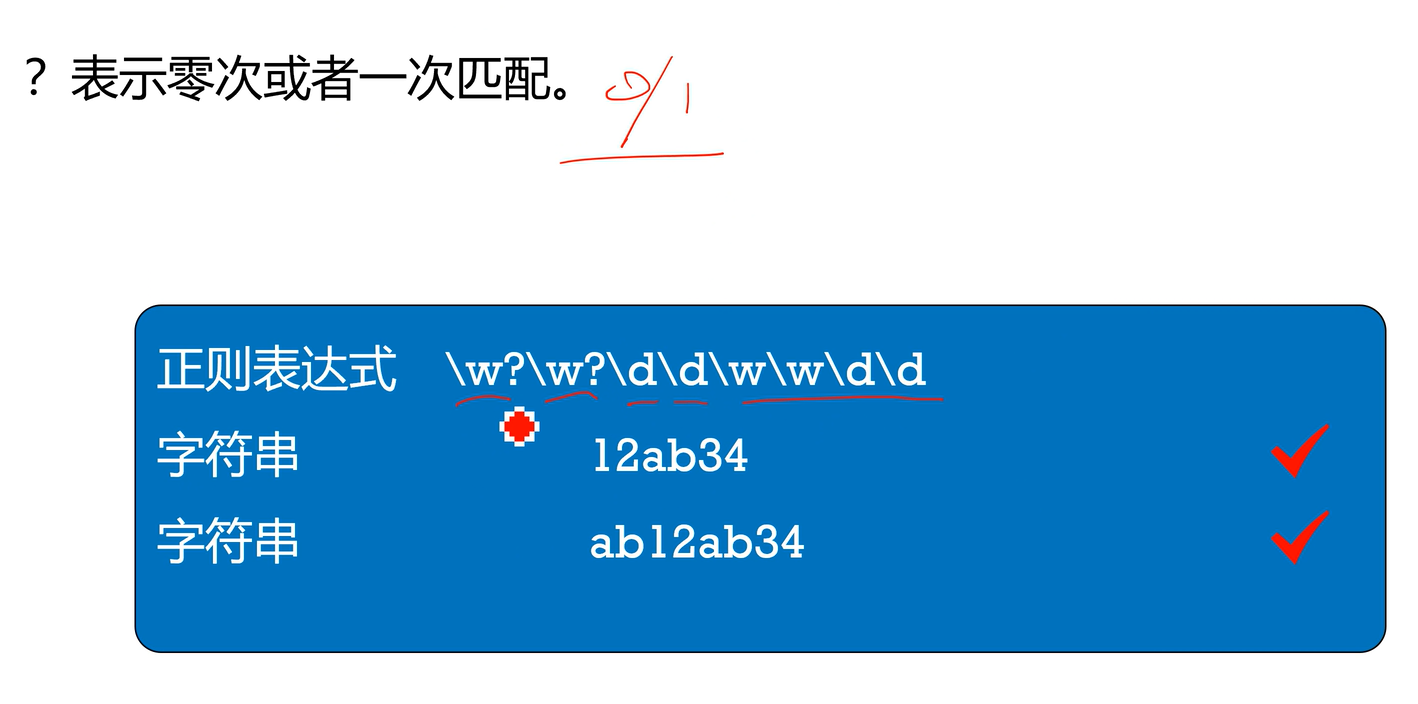

4.1 量词

d+则序列前面必须有数字才能匹配到。

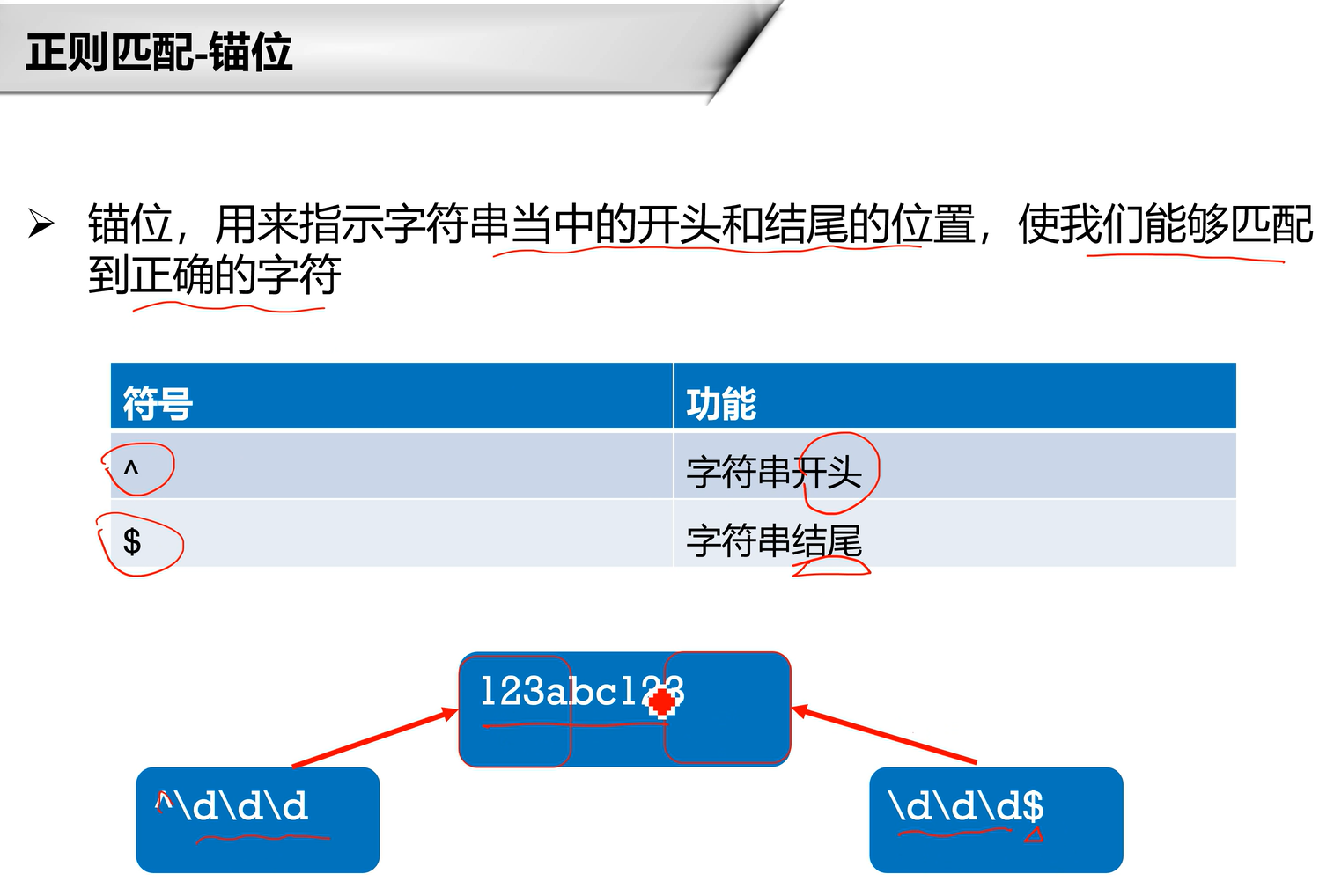

4.2 锚位

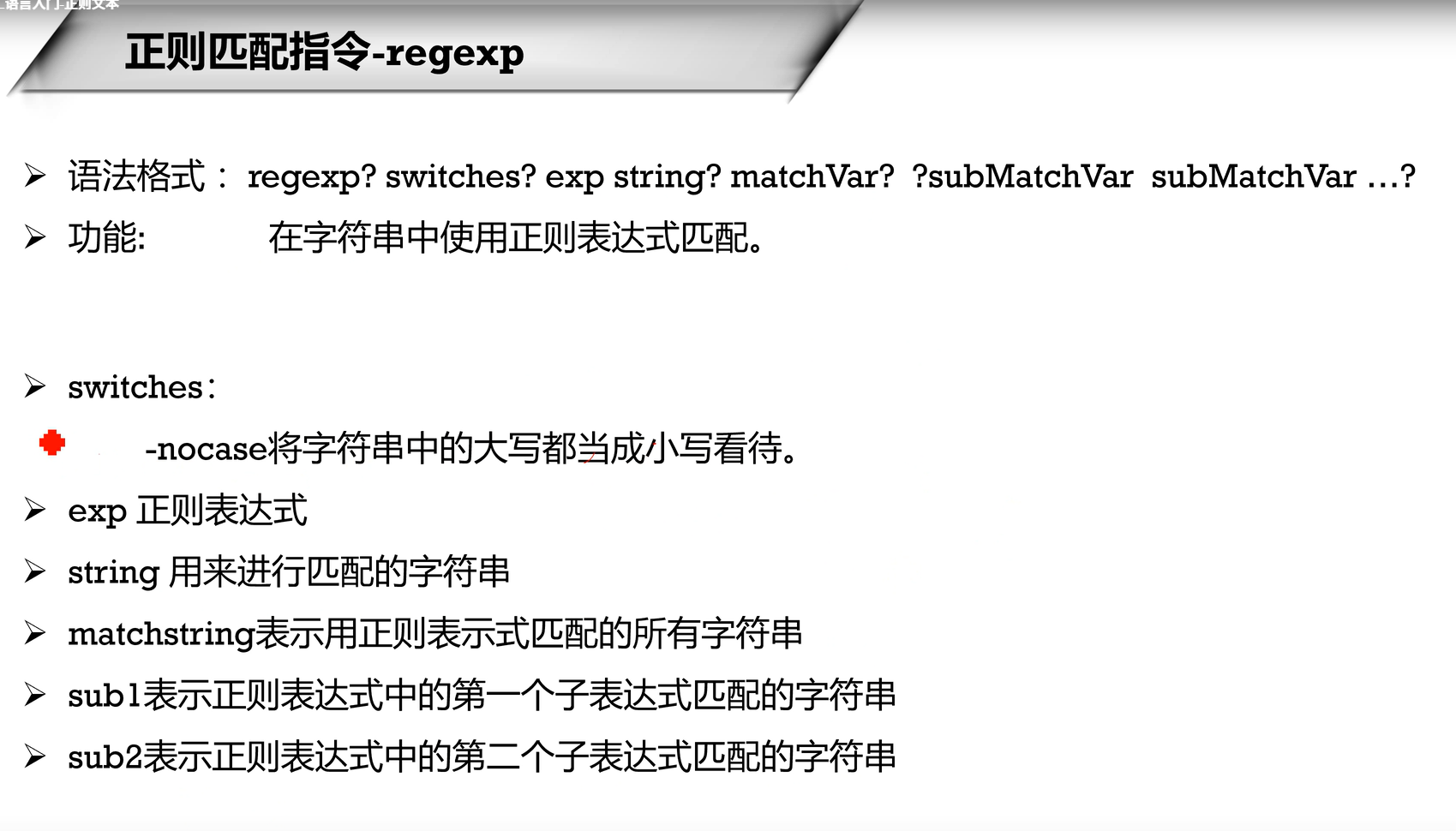

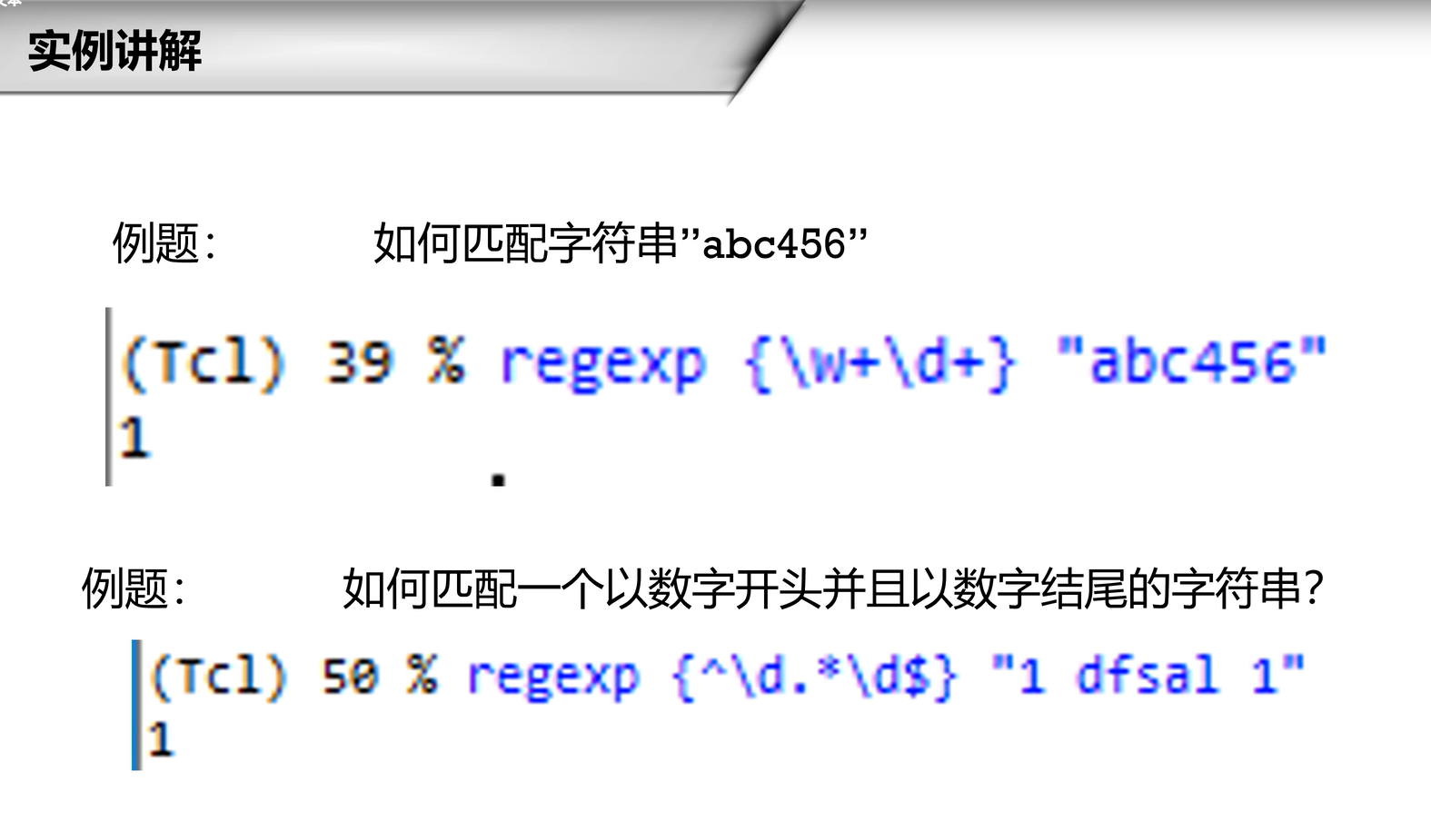

4.3 正则匹配指令 -regexp

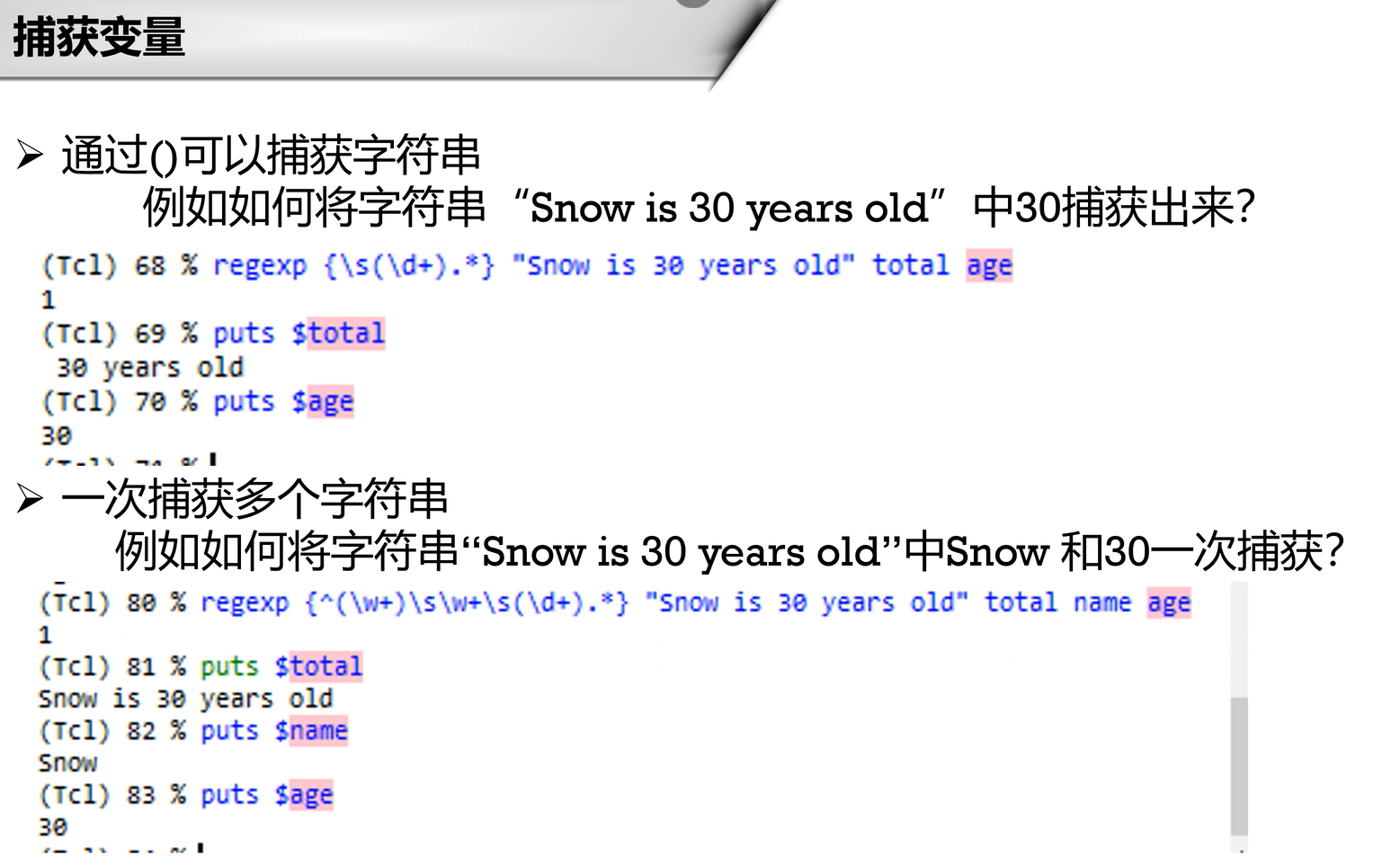

4.4 捕获变量“用()声明正则表达式中的子表达式”

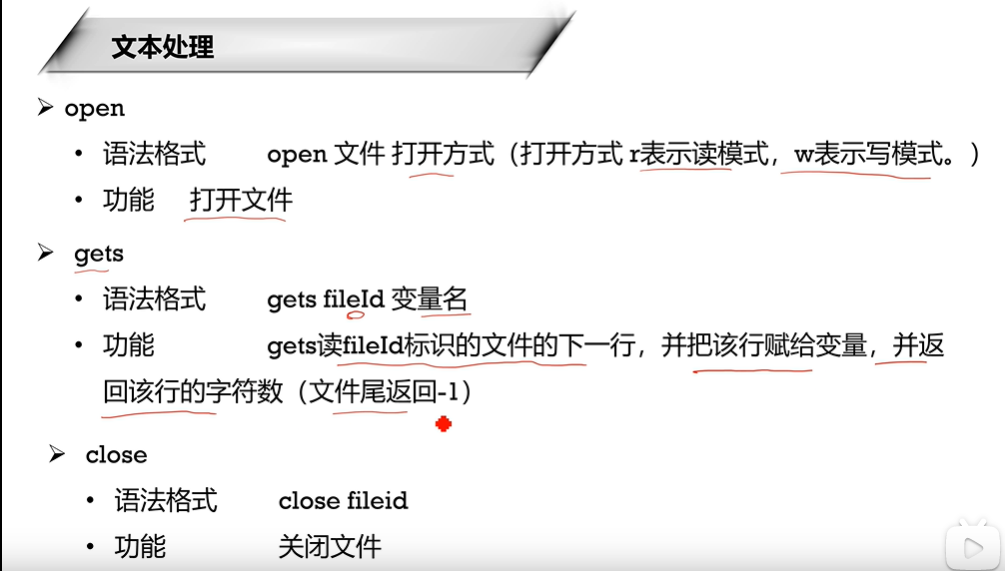

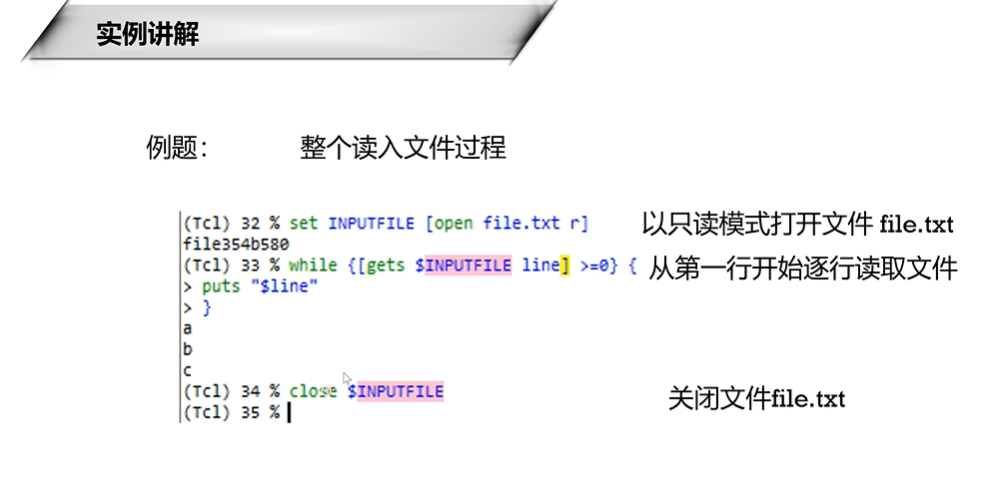

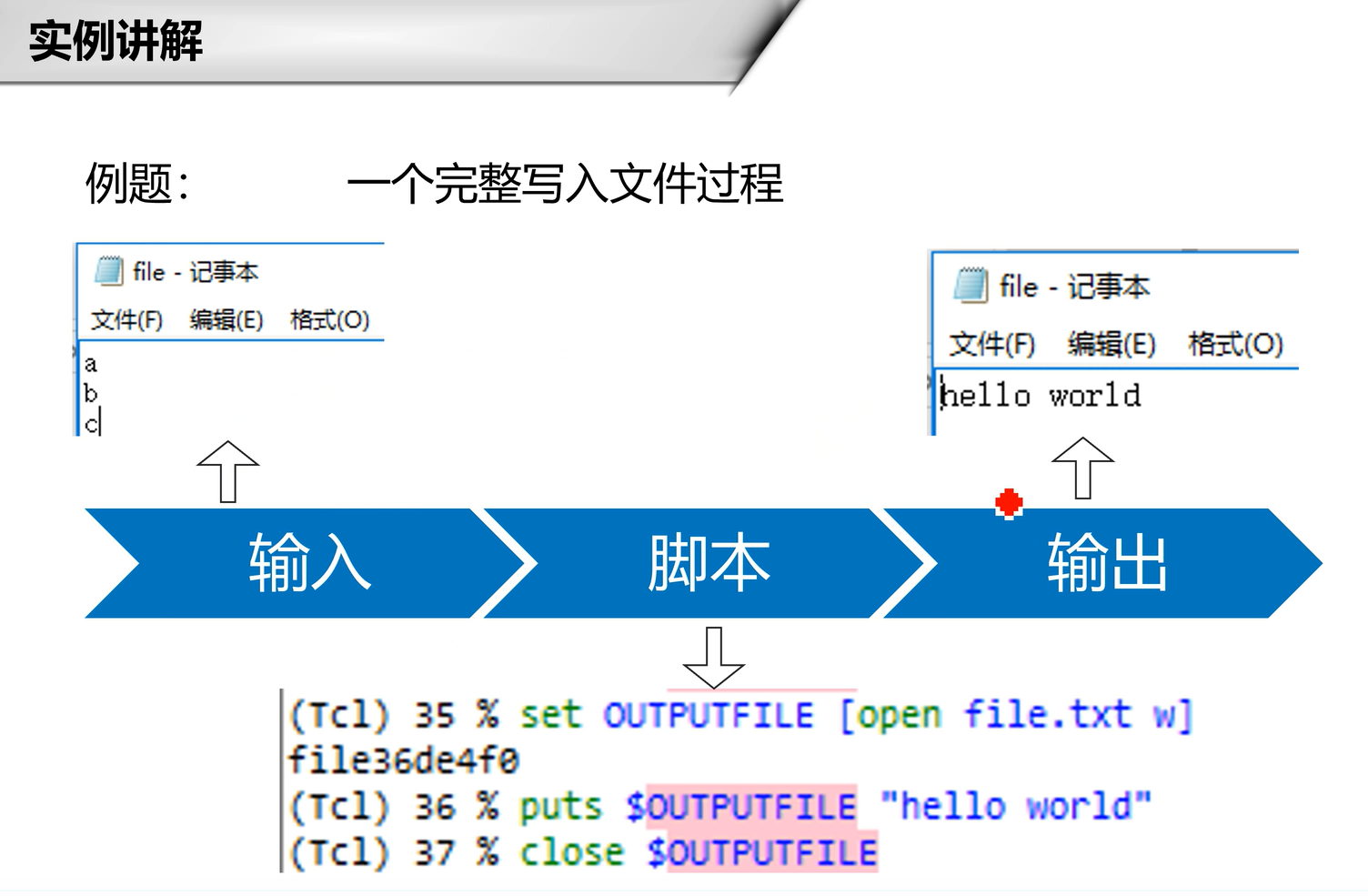

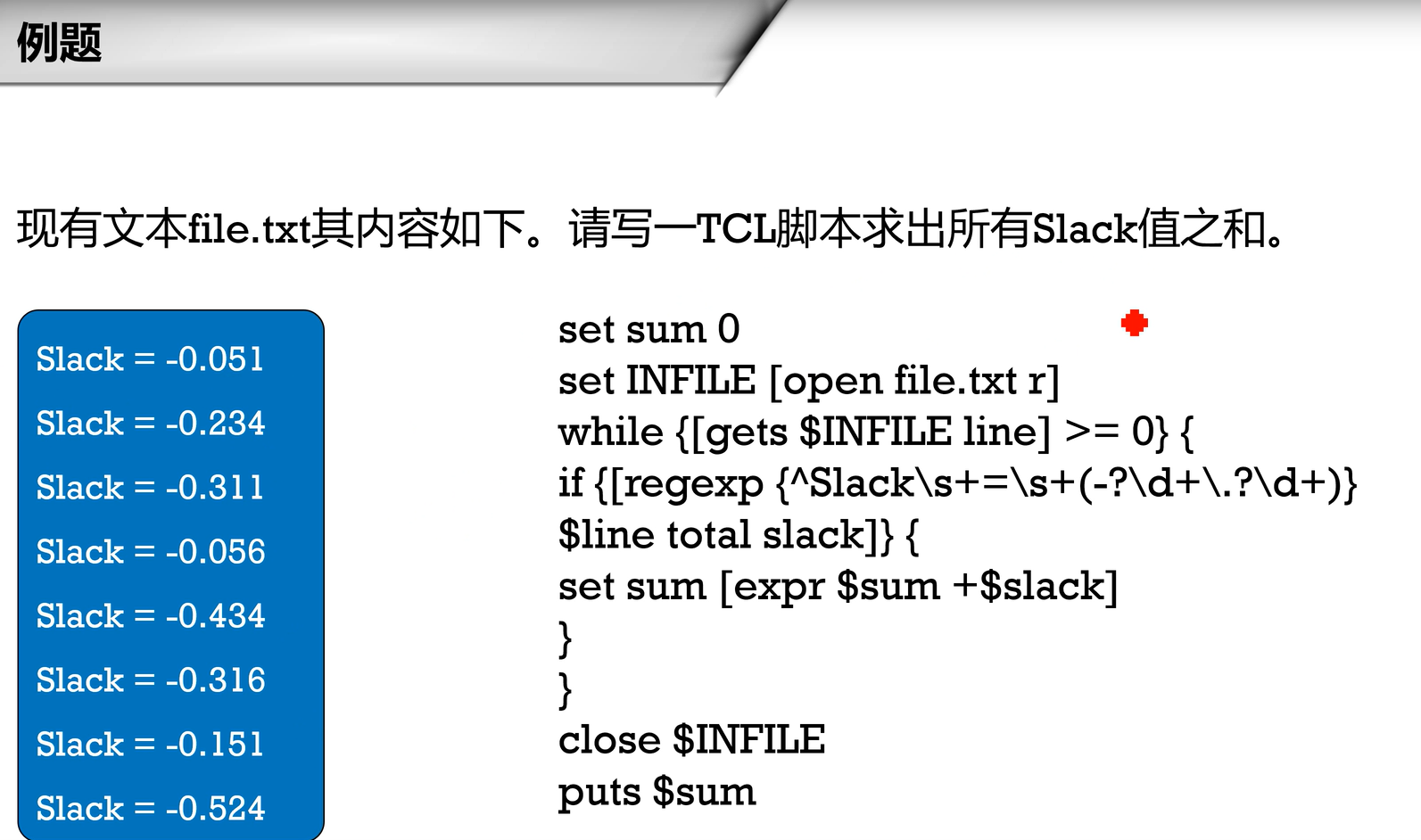

5. 文本处理

5.1 读入

5.2 写入

上面正则匹配中,$line为要匹配的字符串,total为匹配到的整体字符串,slack为匹配到的子字符串

6. TCL应用–Synopsys TCL

参考资料

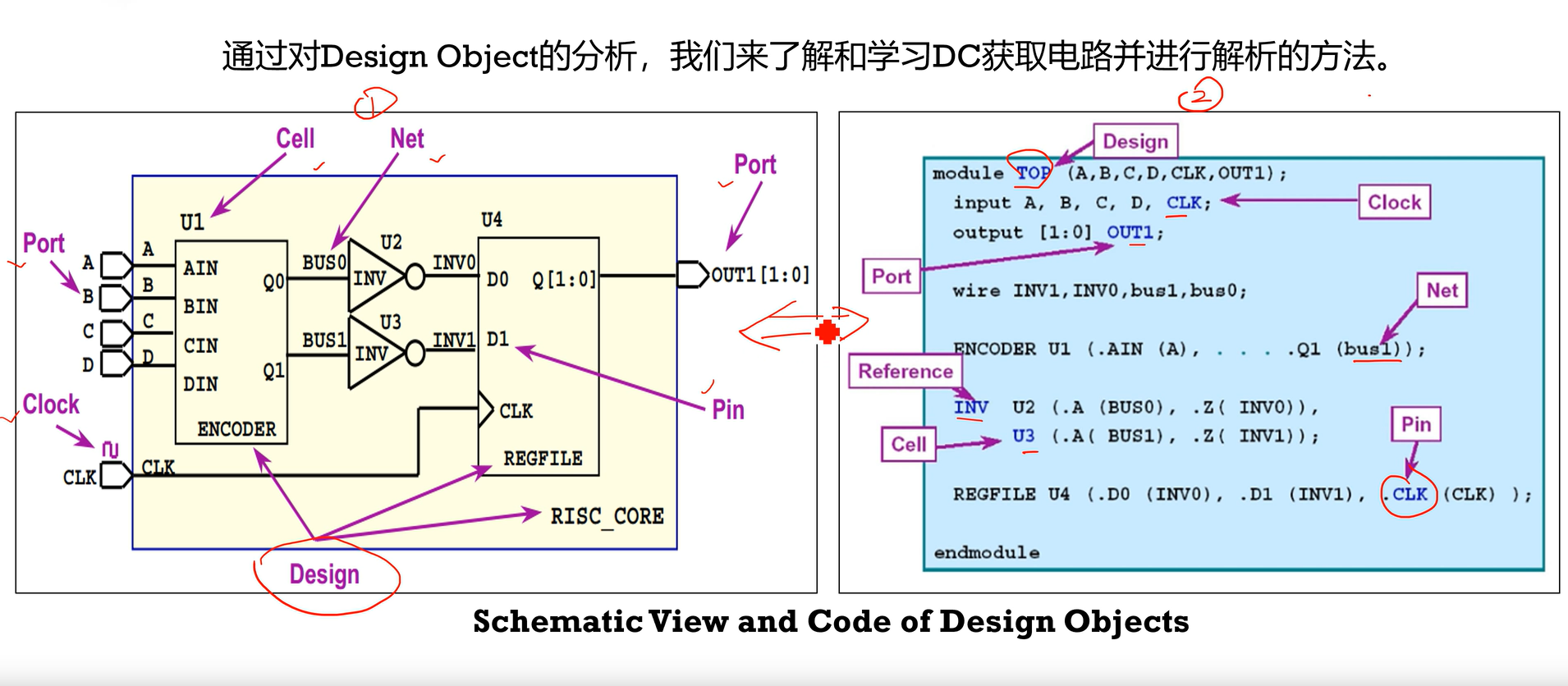

6.1 TCL在EDA工具中的扩展与应用

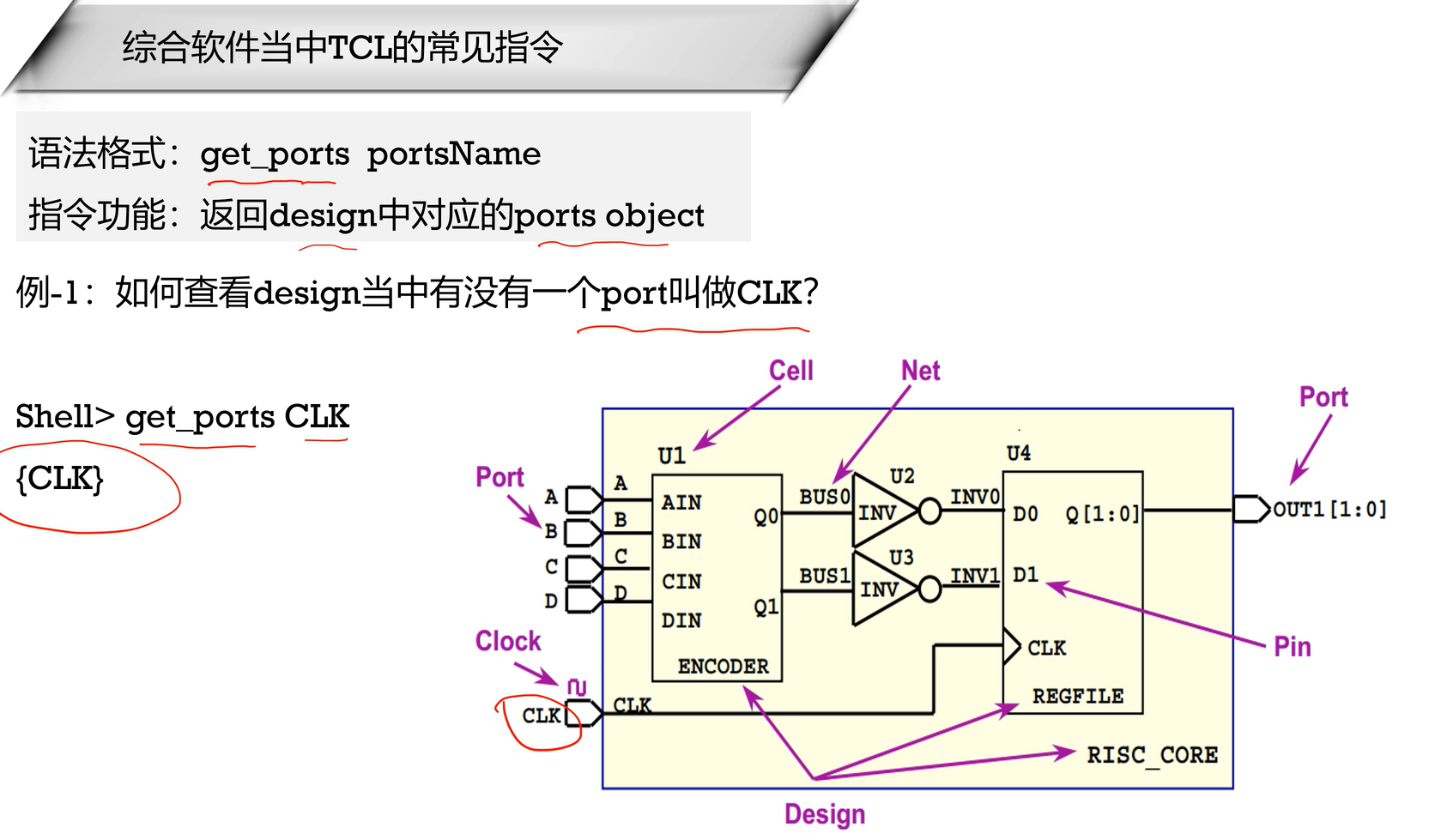

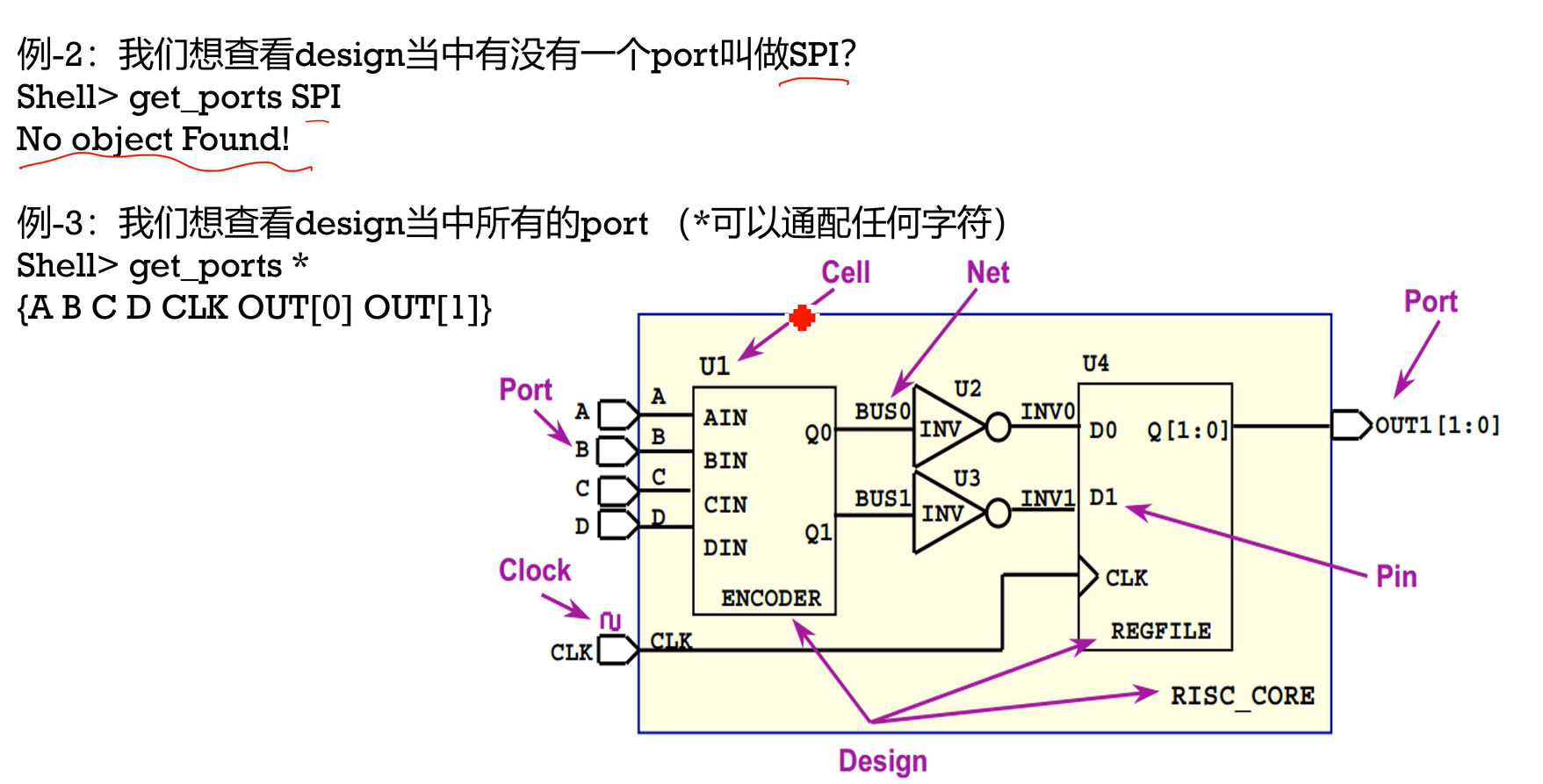

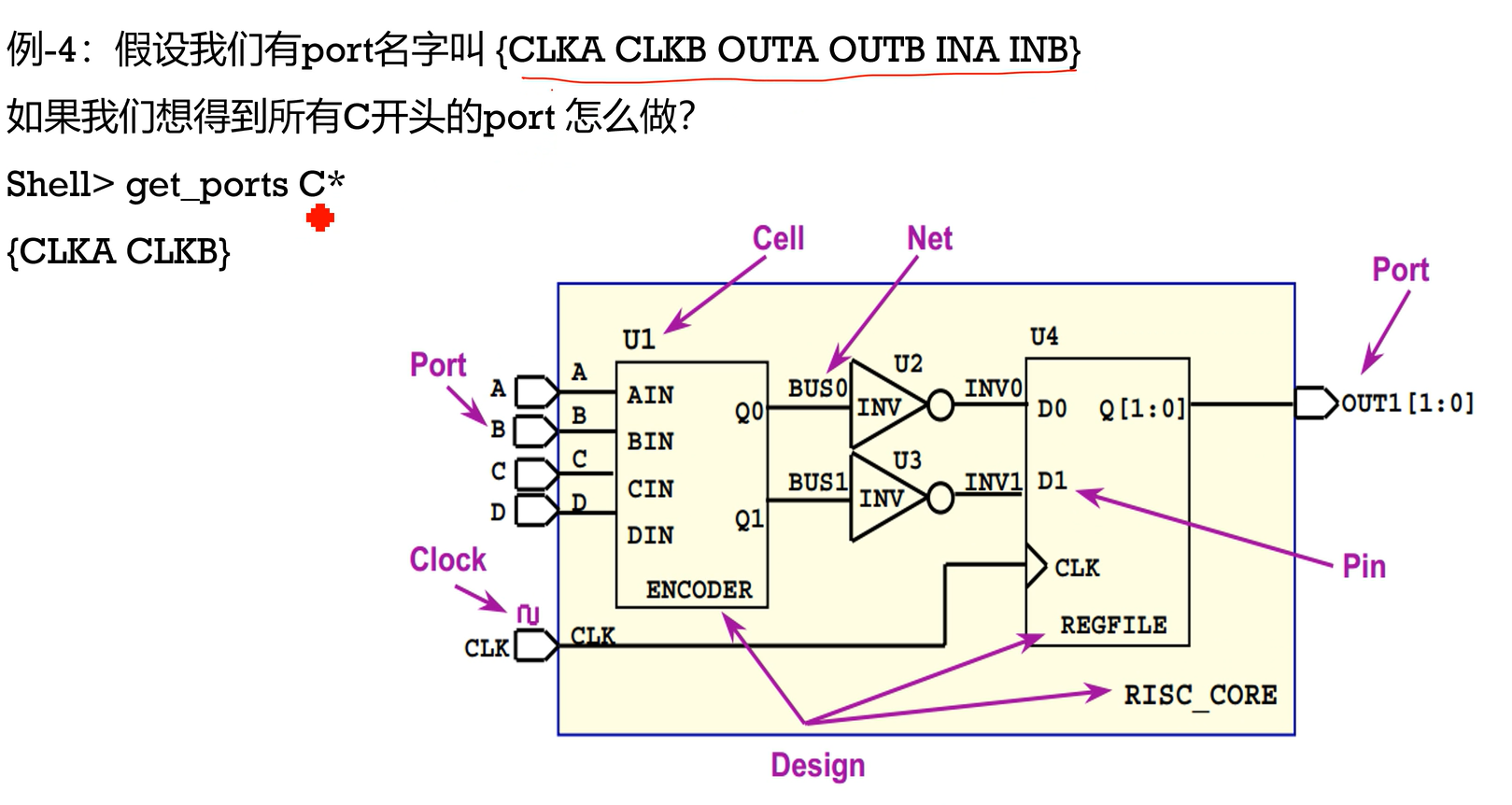

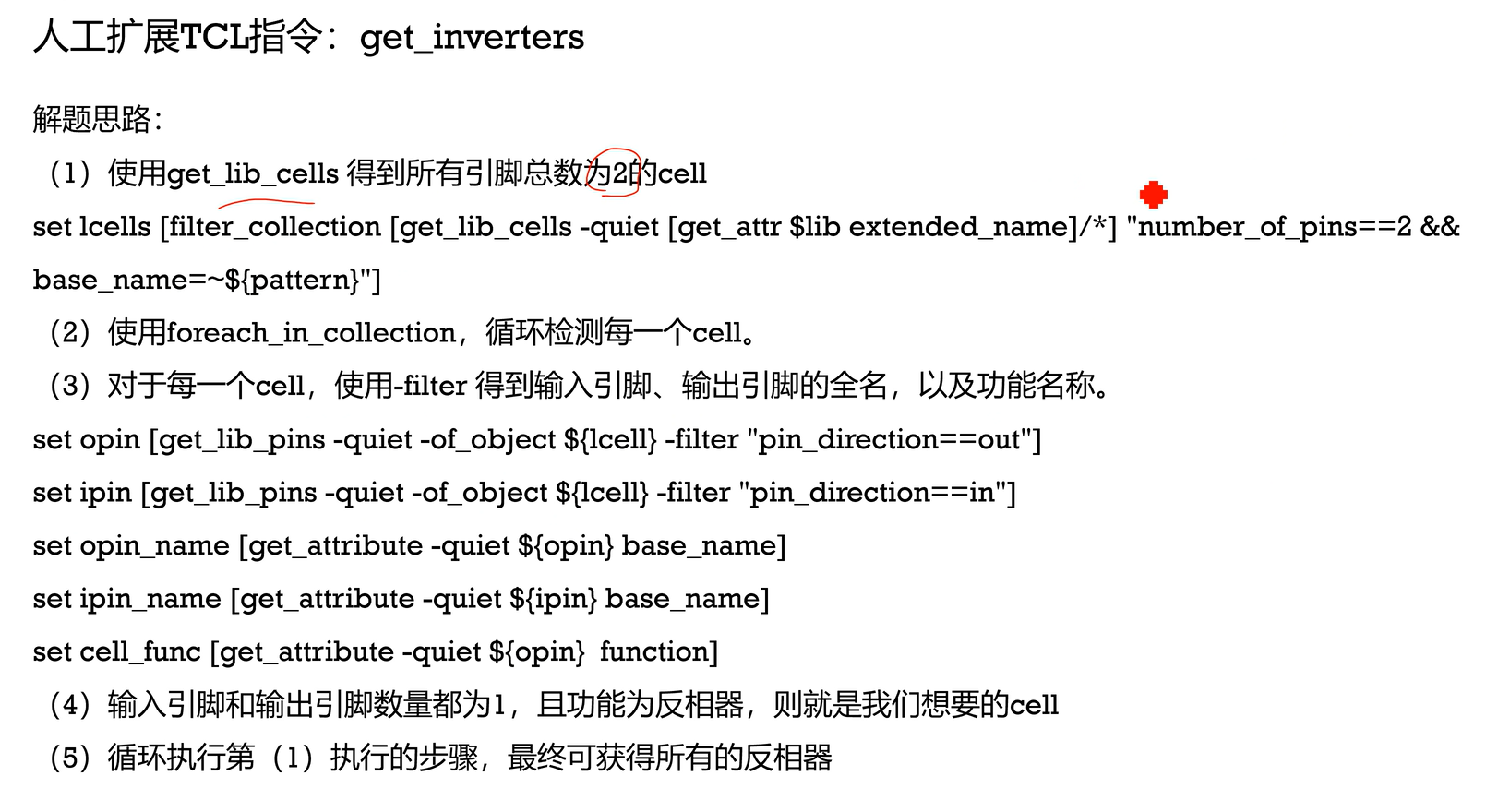

get_ports

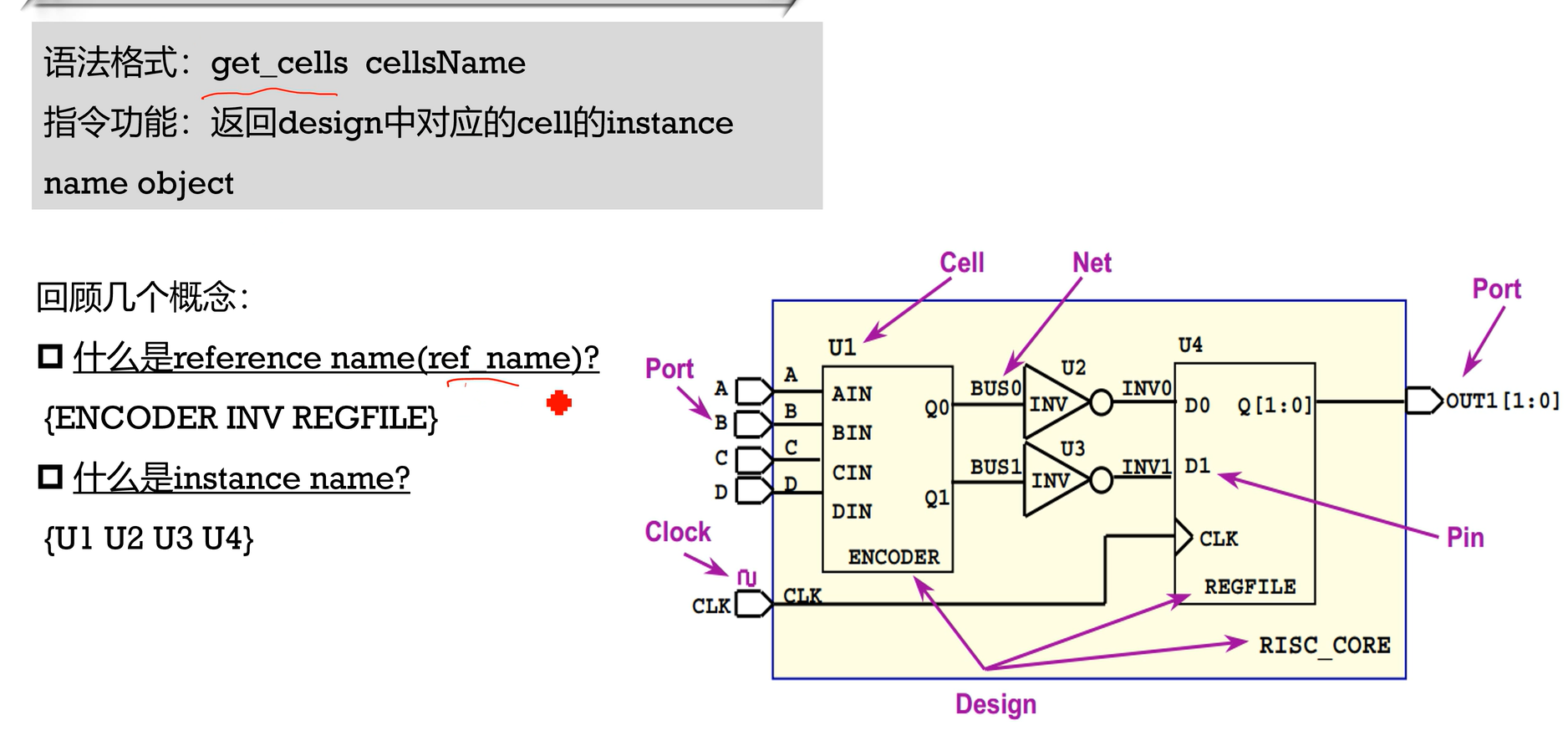

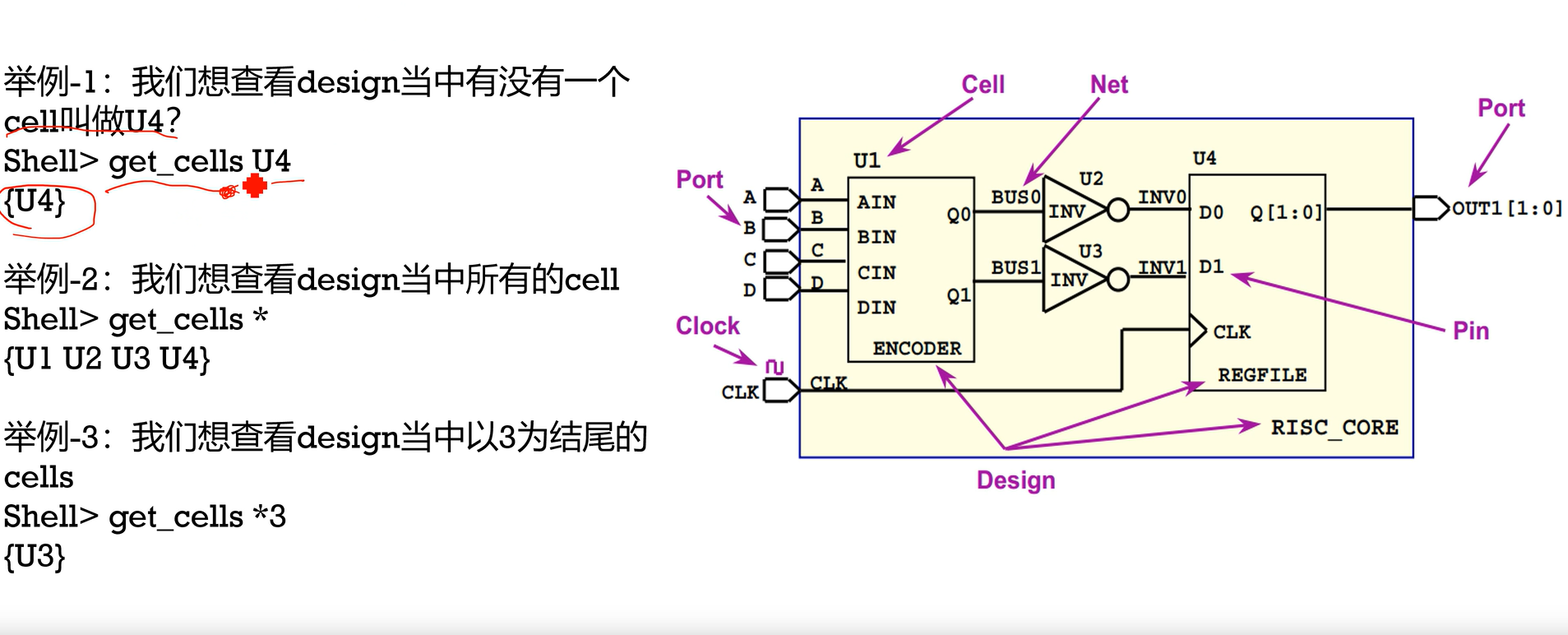

get_cells

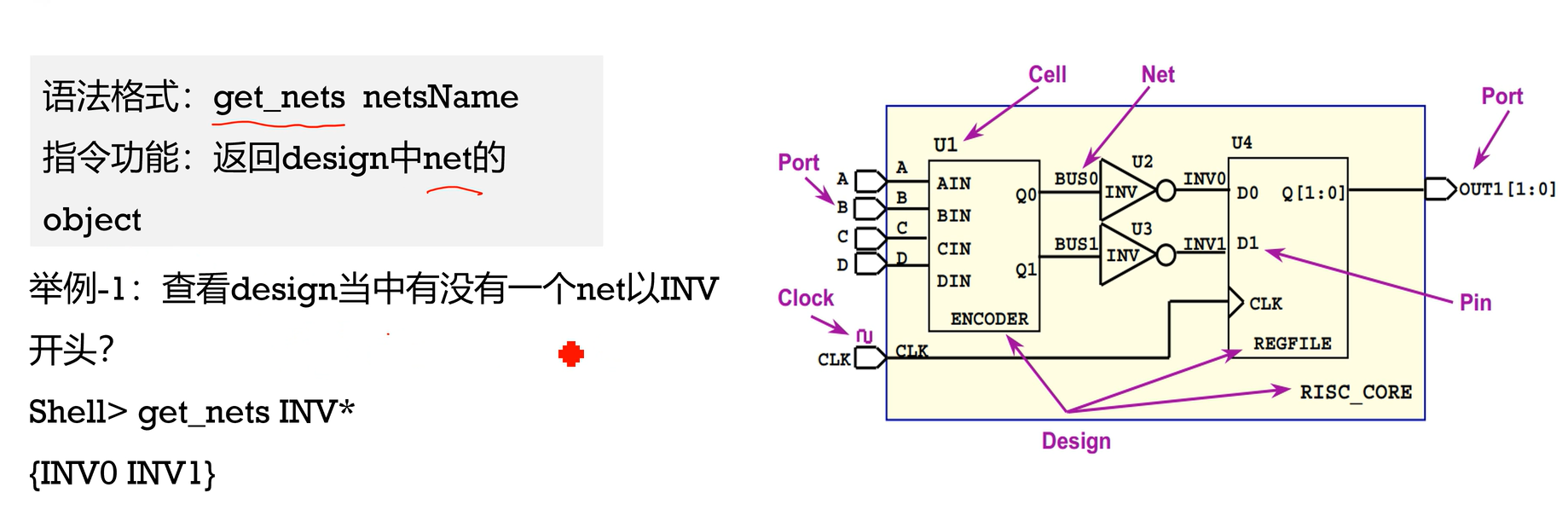

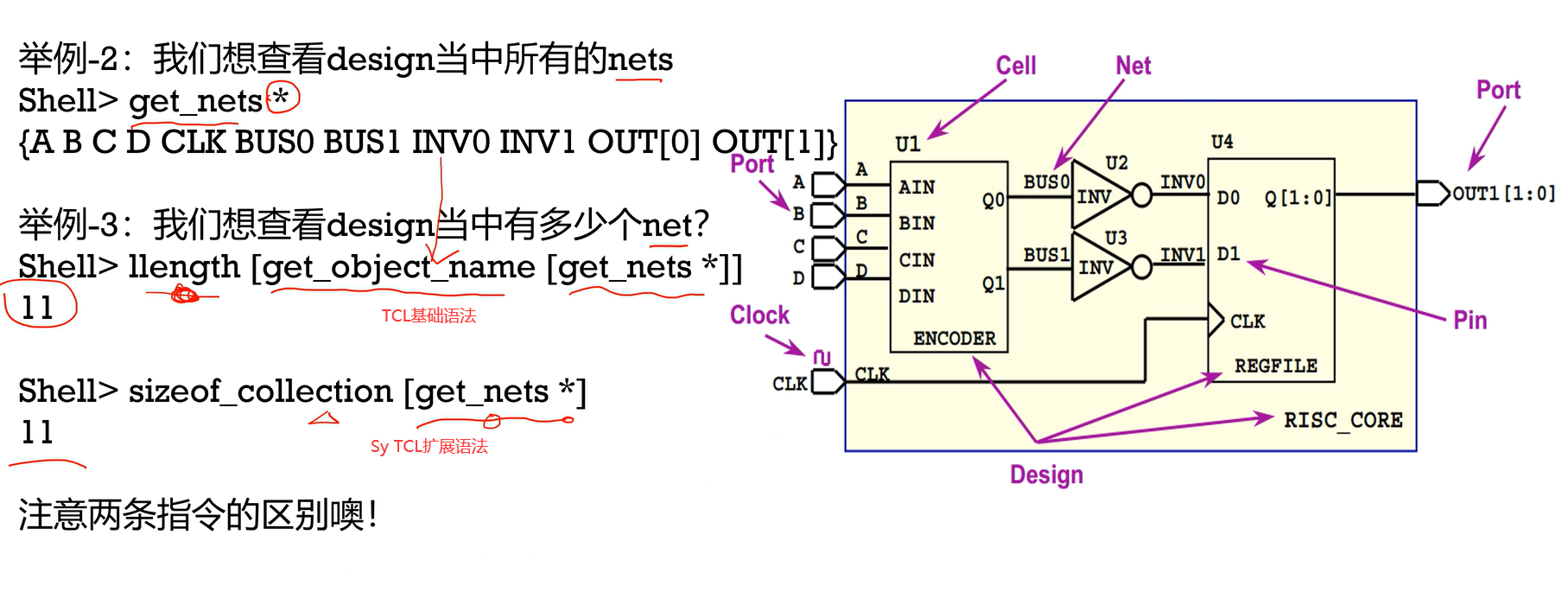

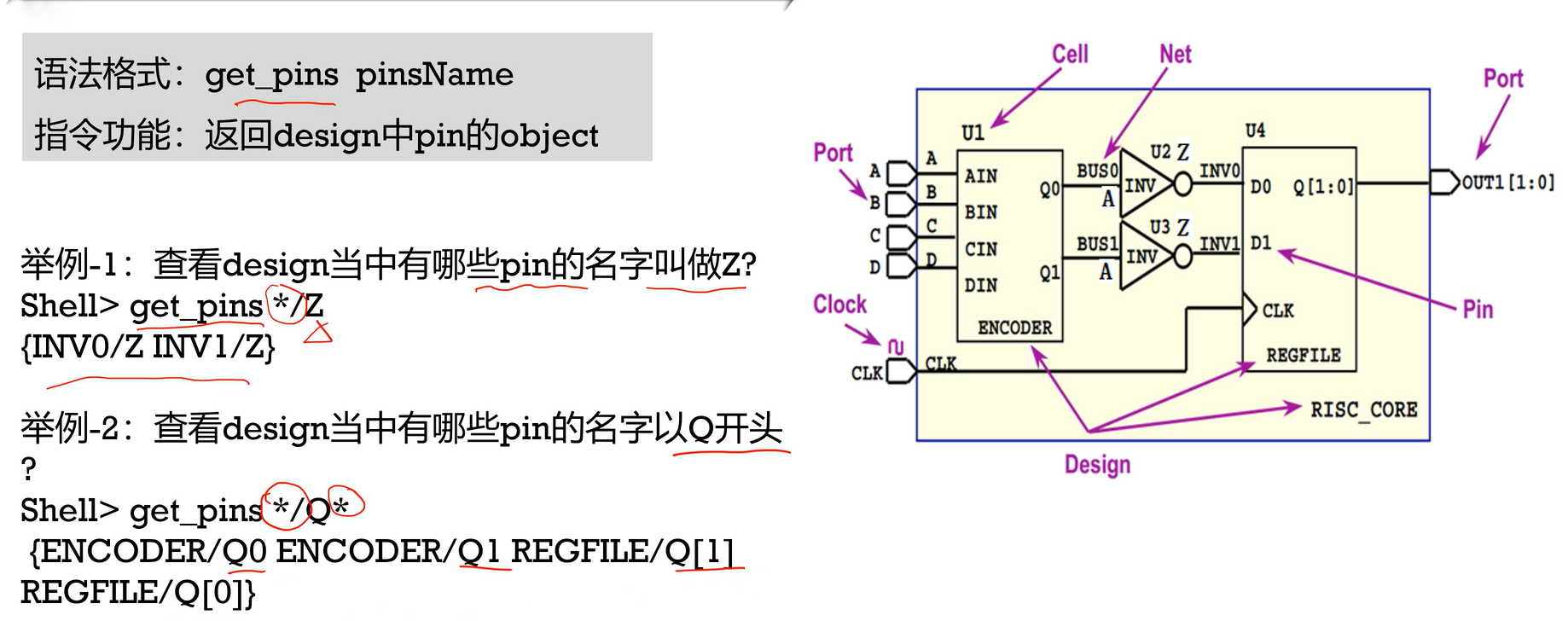

get_nets

get_pins

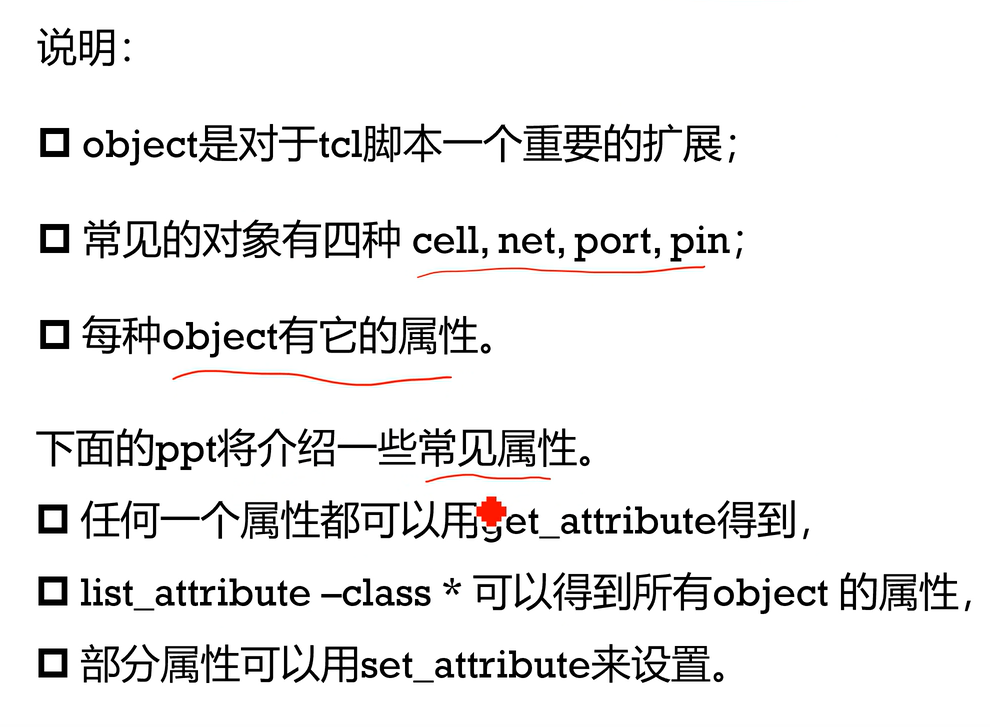

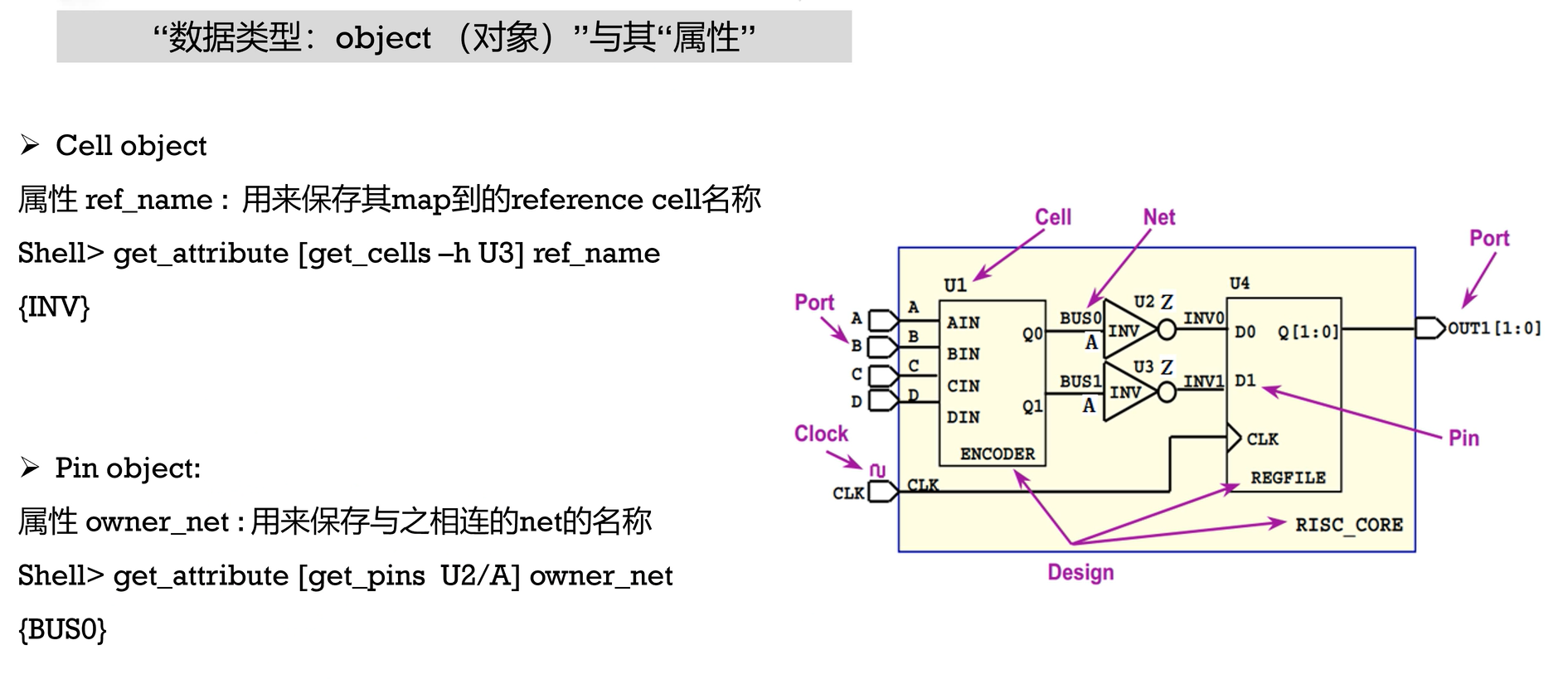

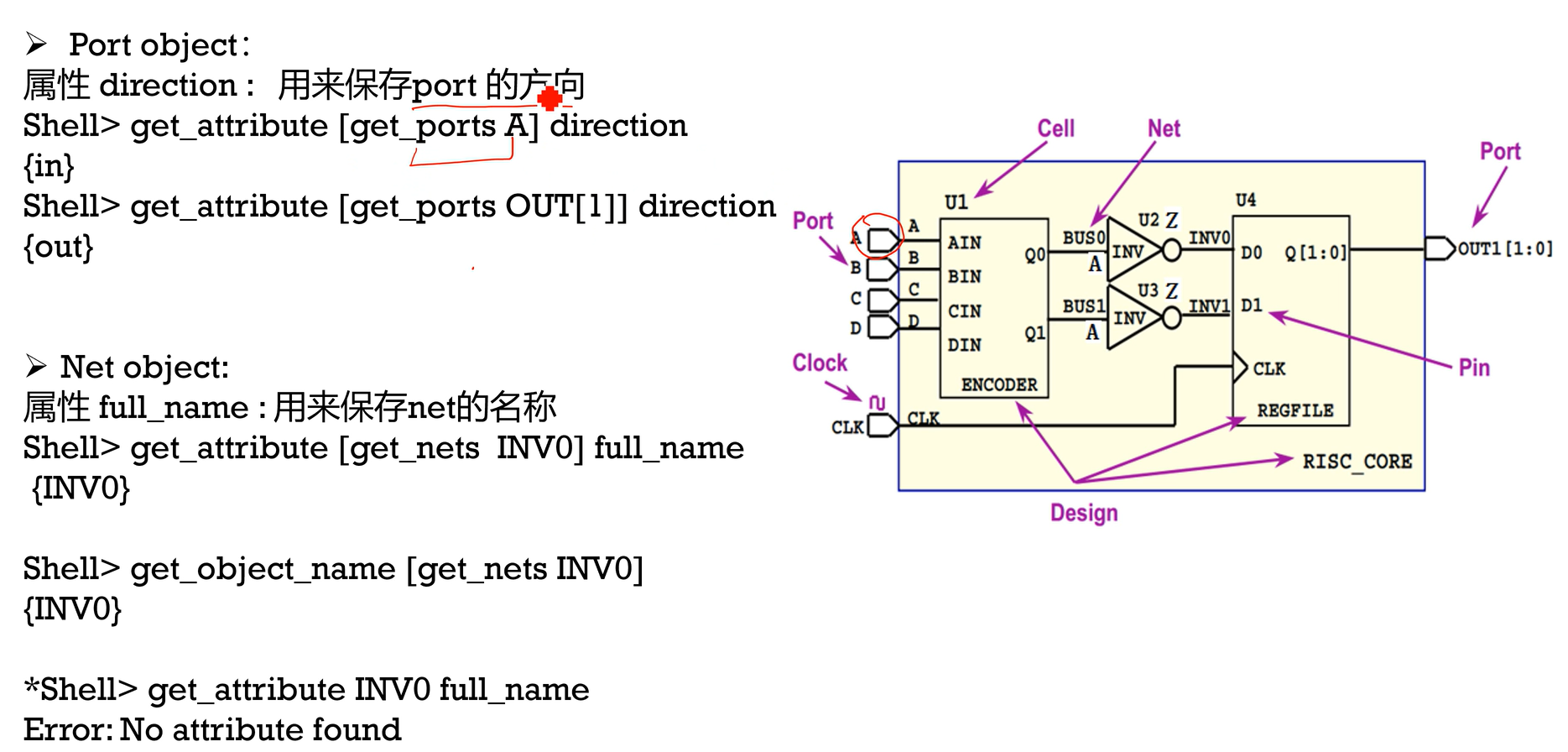

6.2 “数据类型:object(对象)”与其“属性”

object

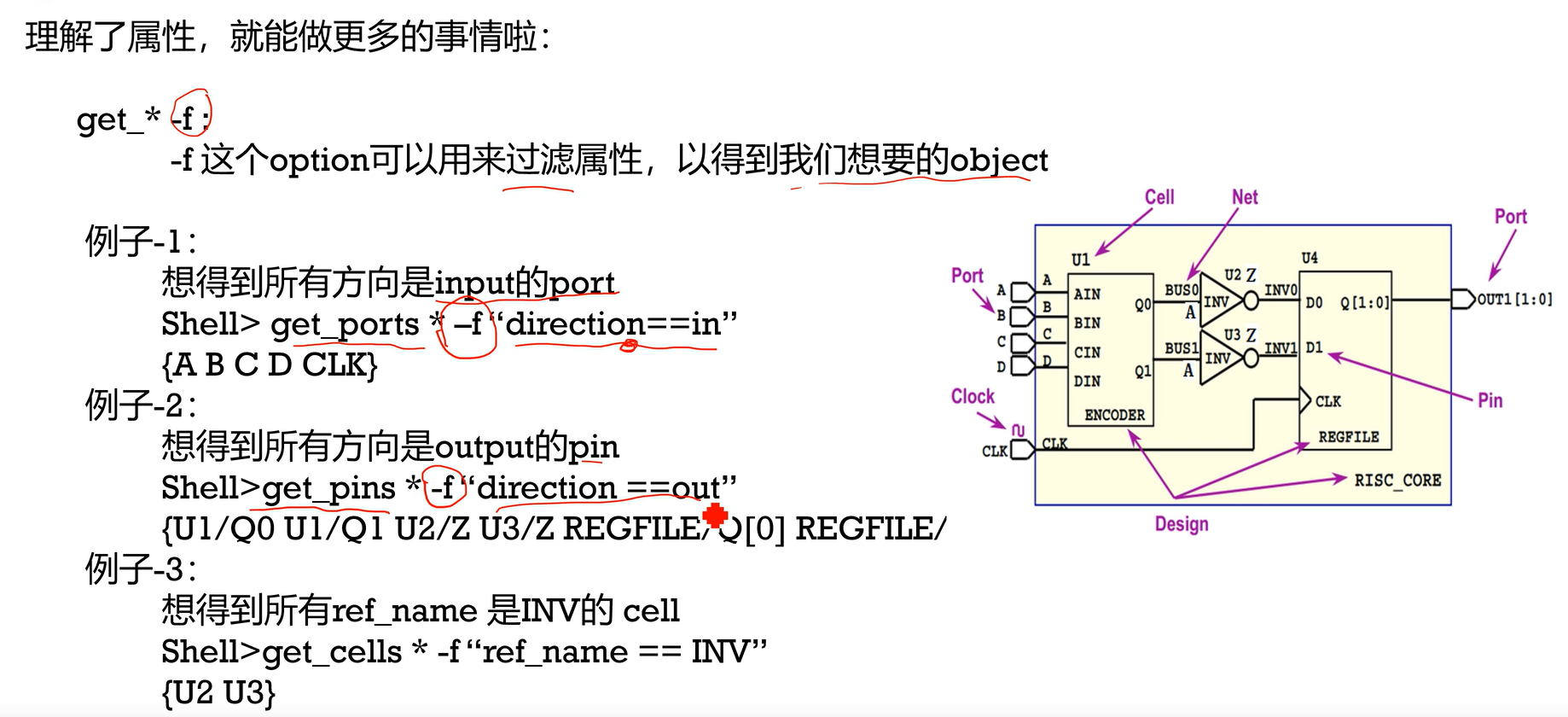

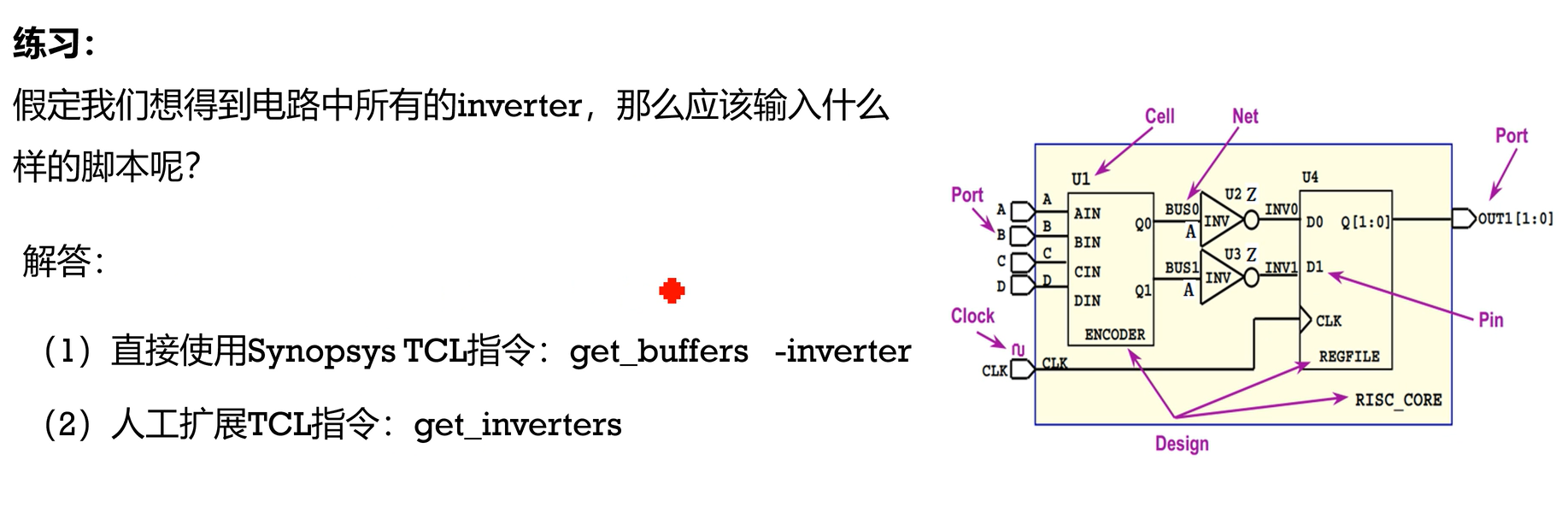

get_*-f

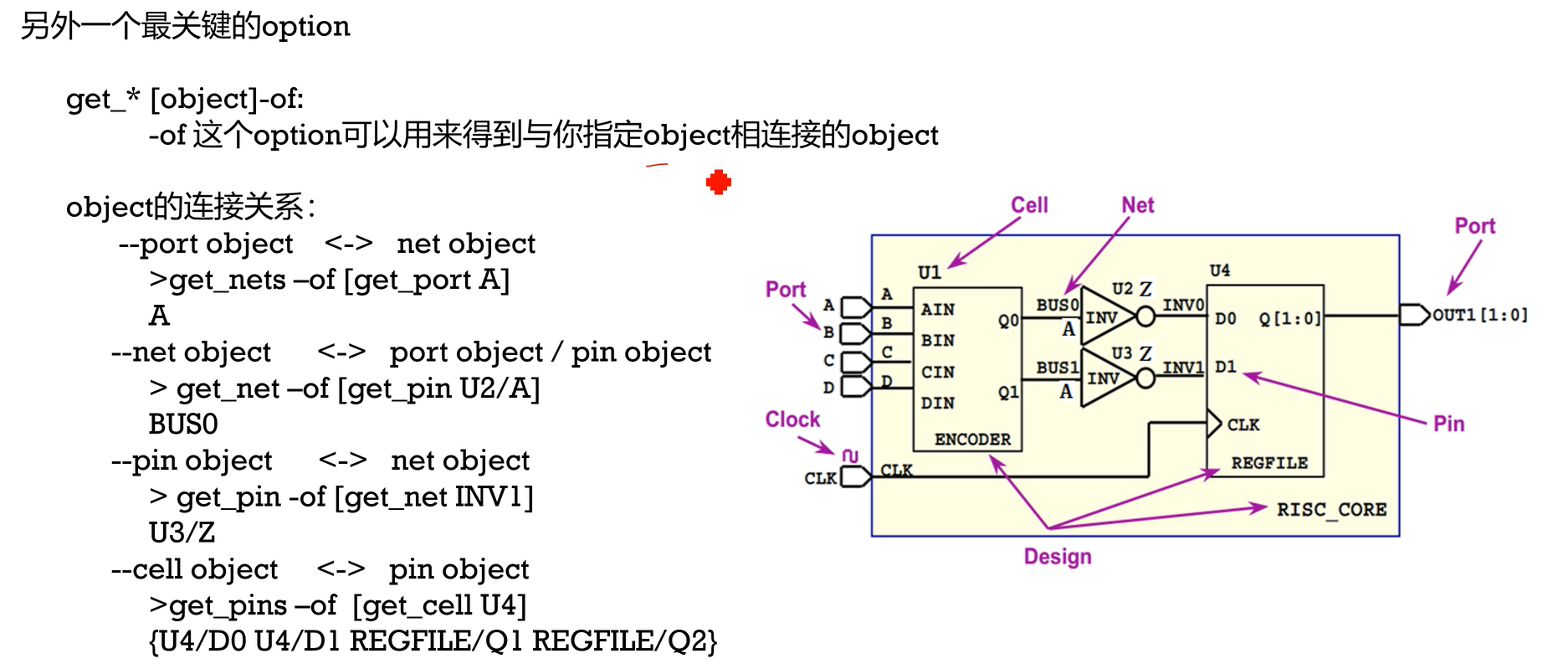

get_*[object]-of

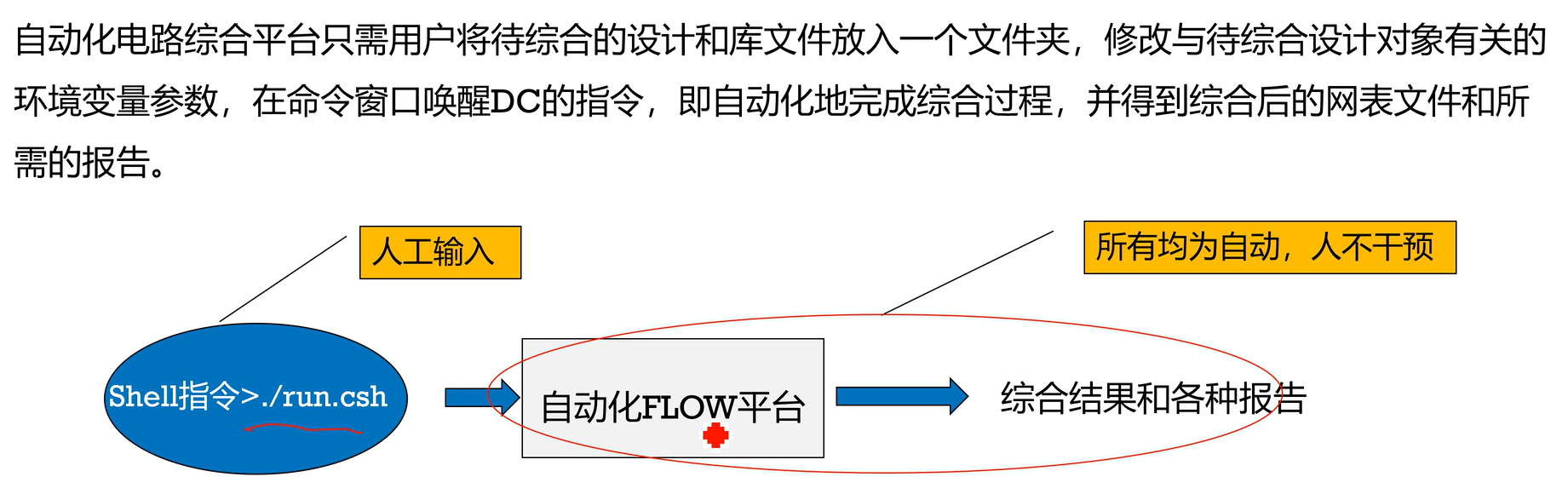

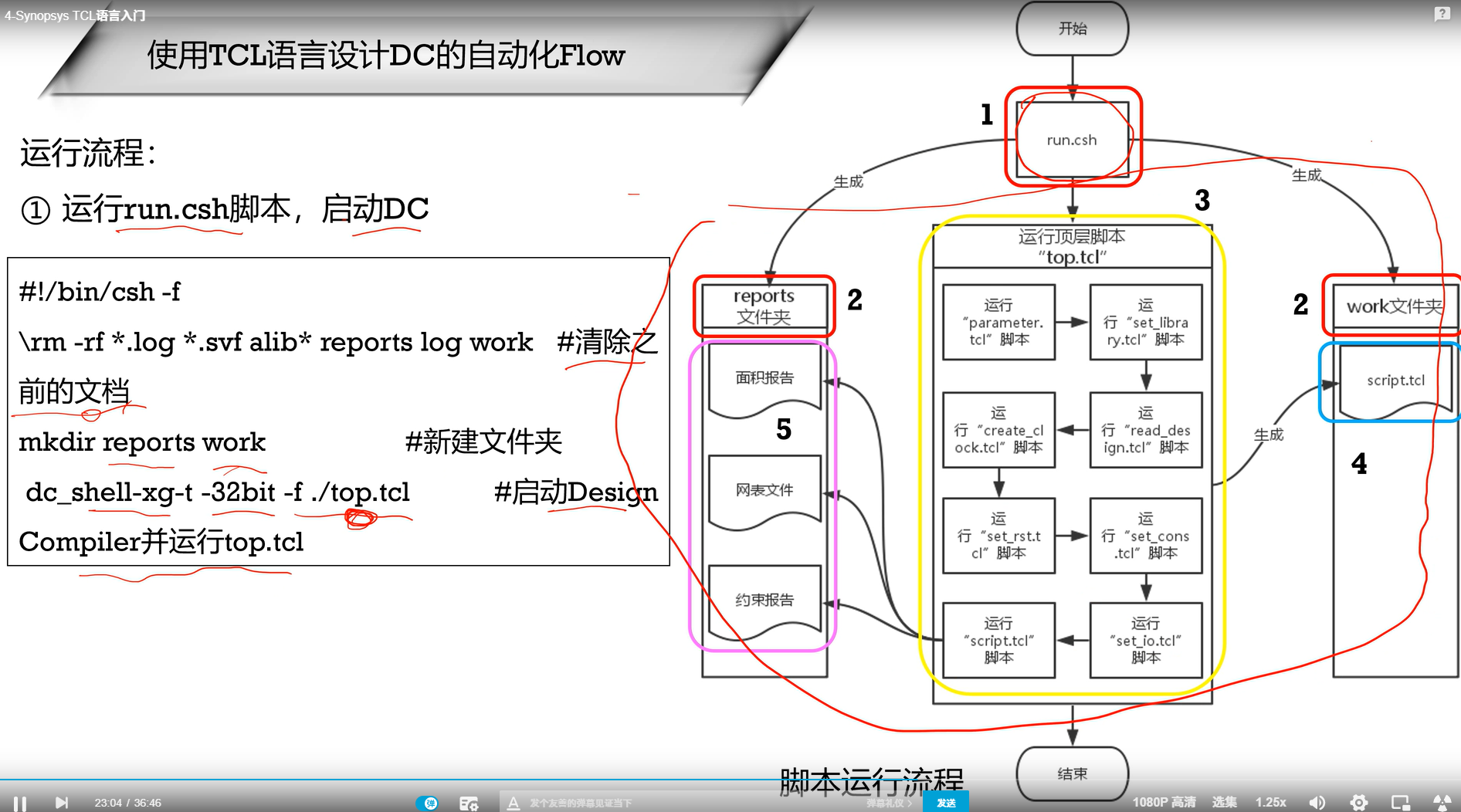

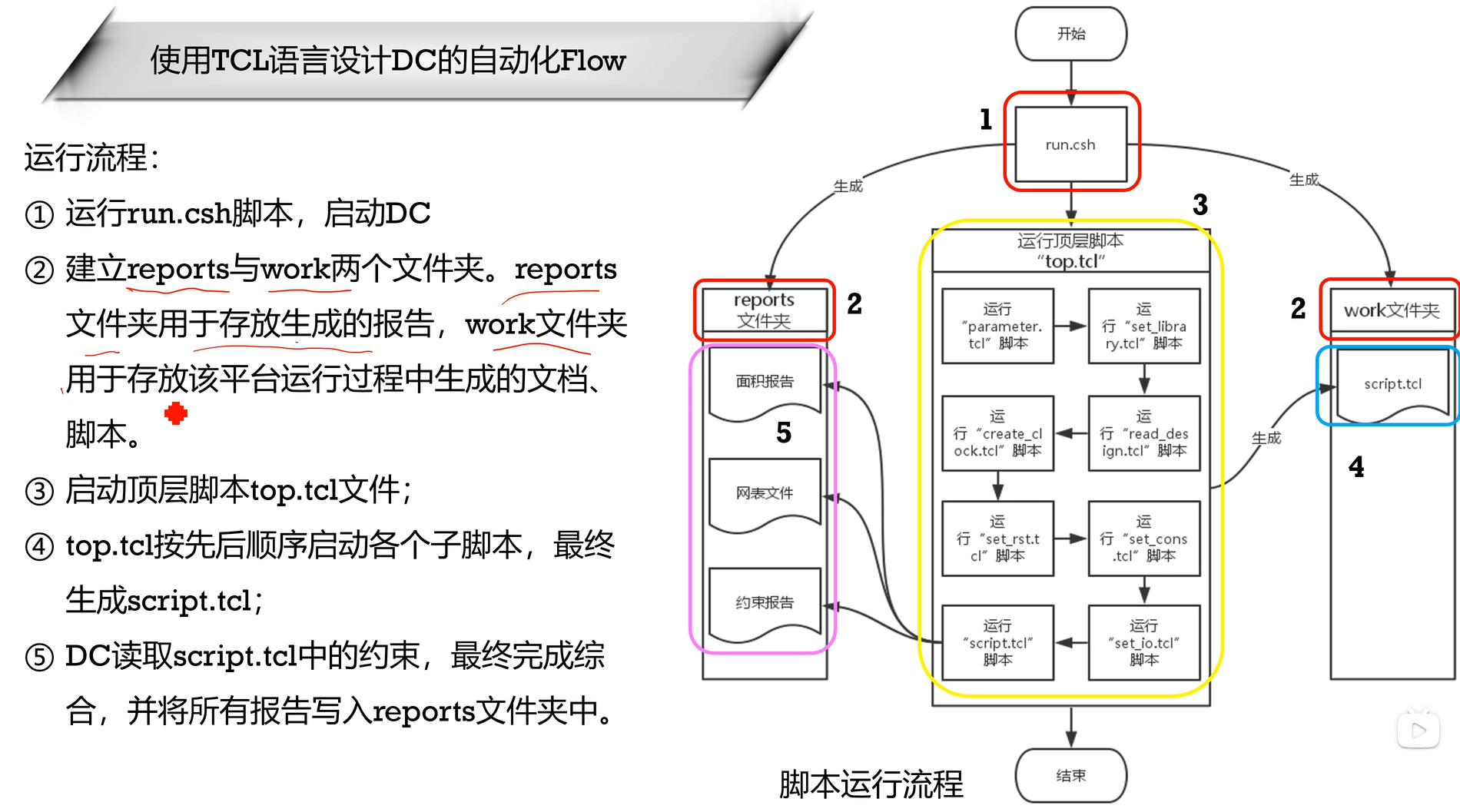

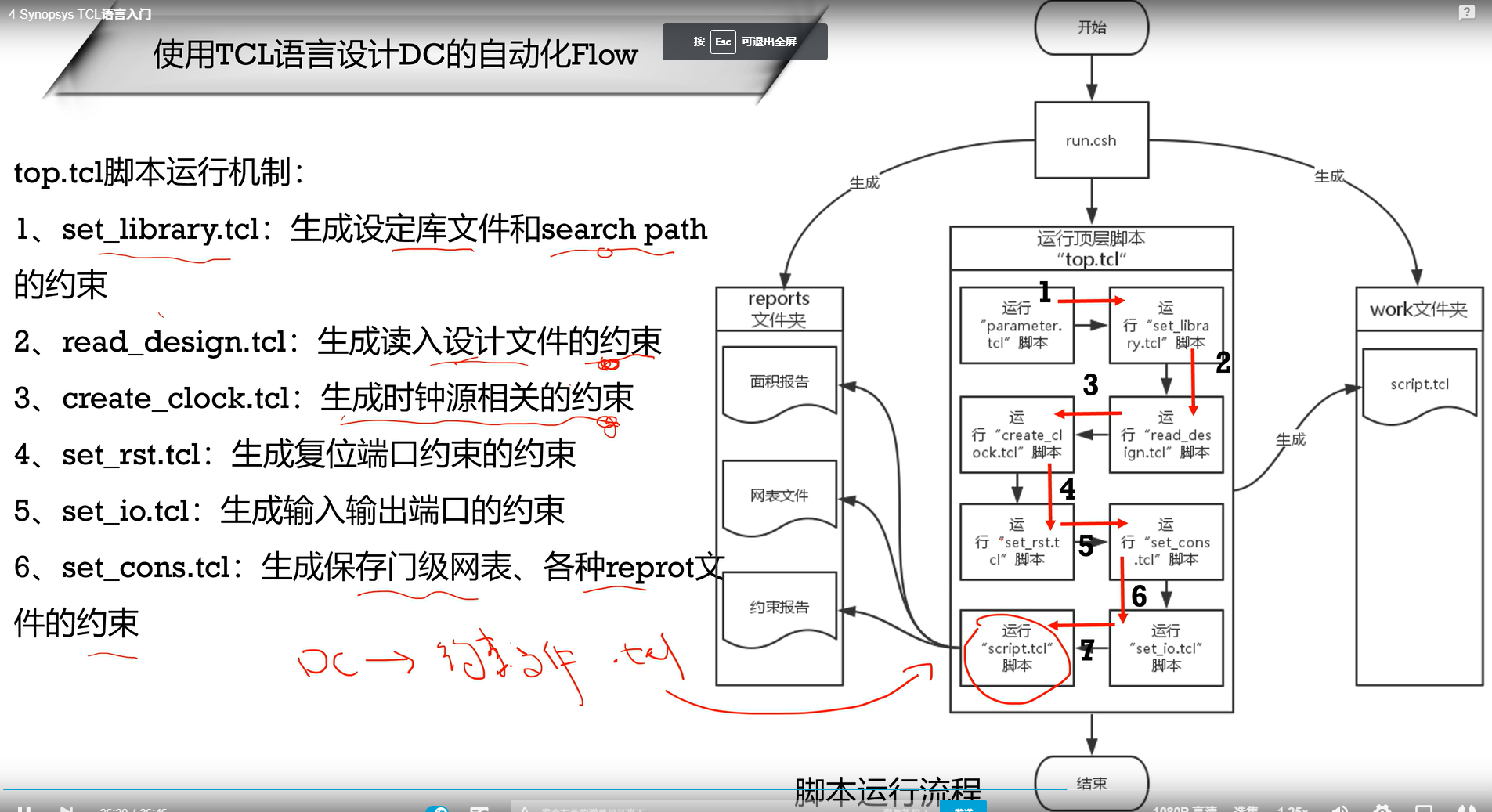

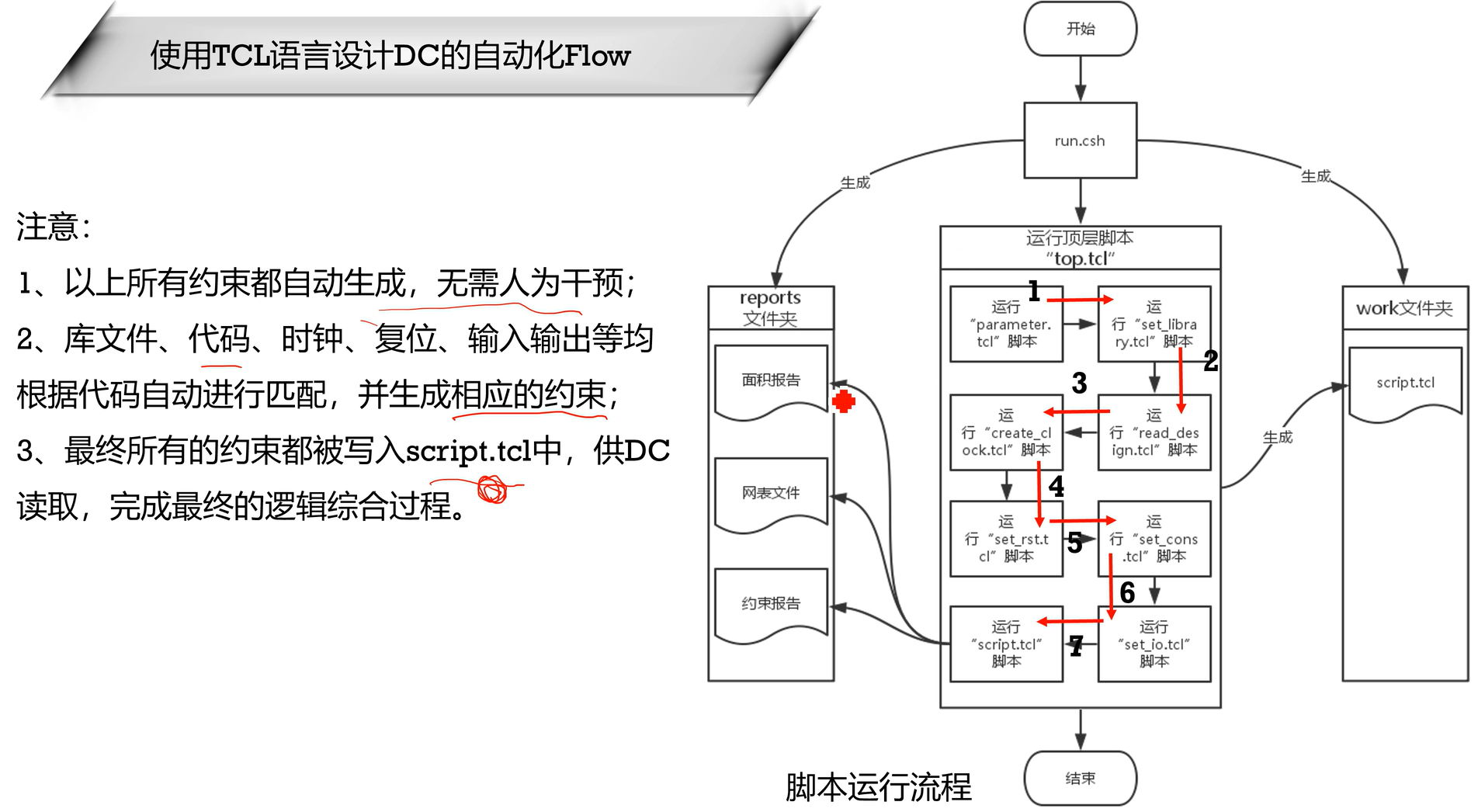

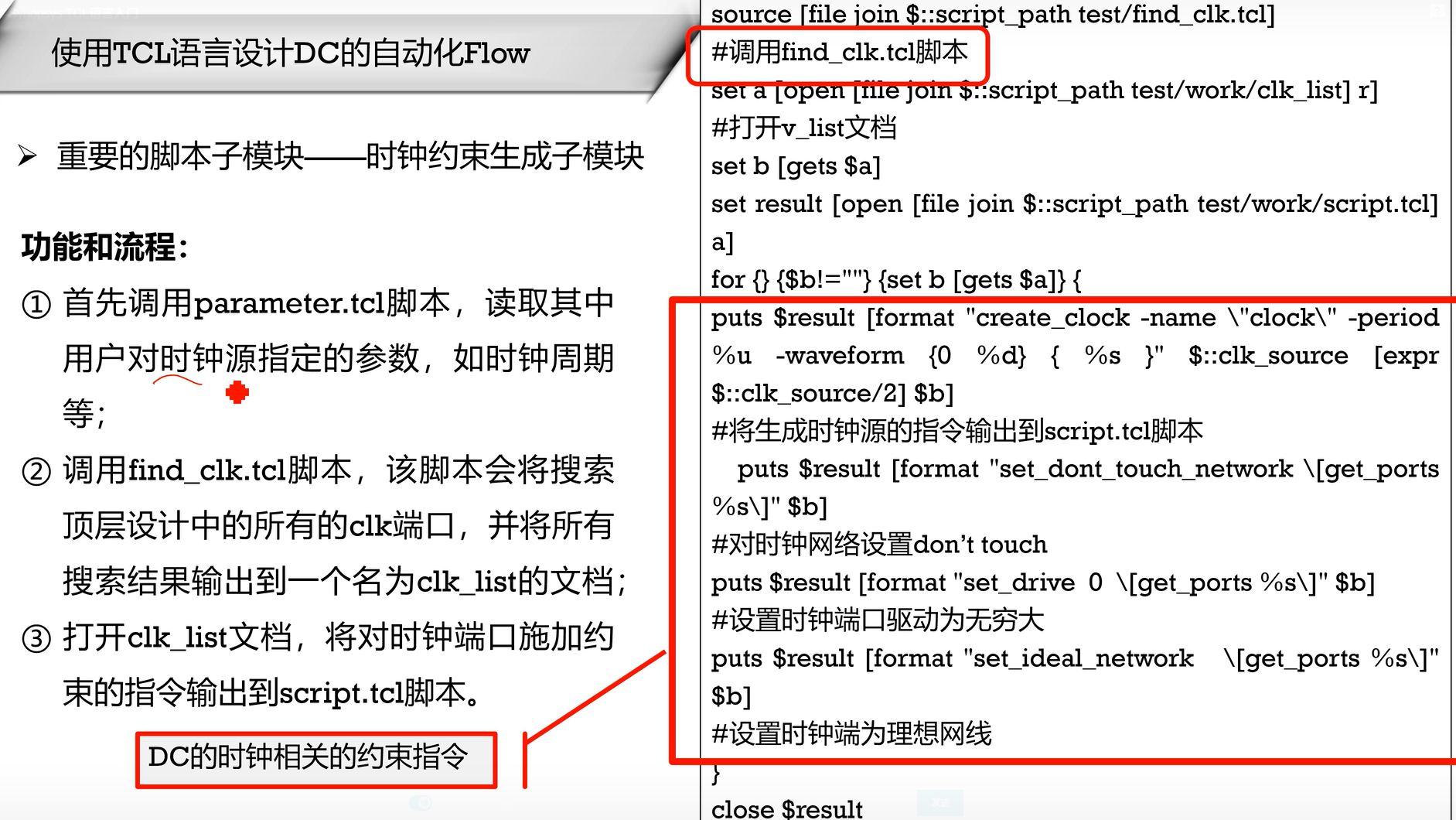

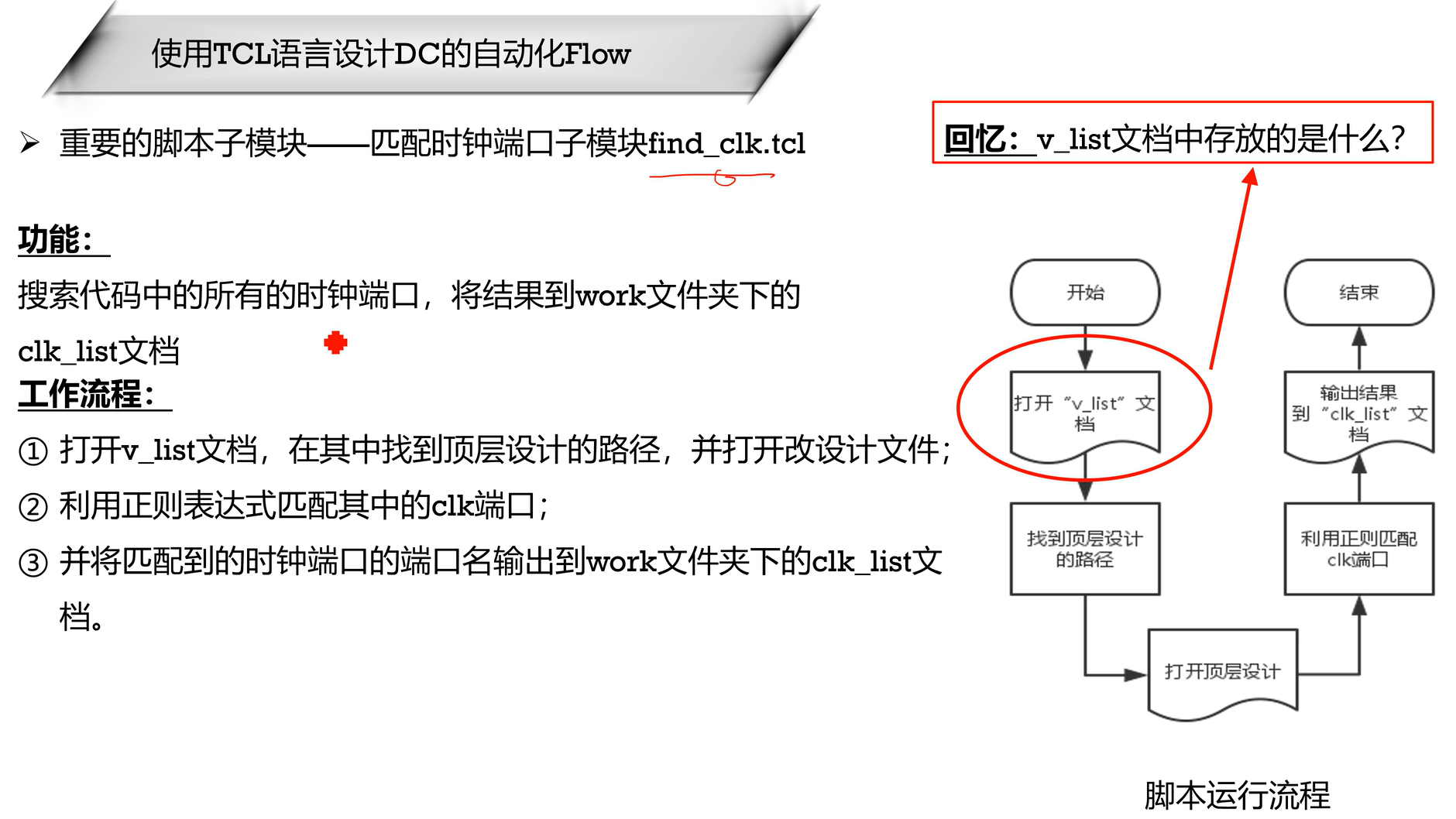

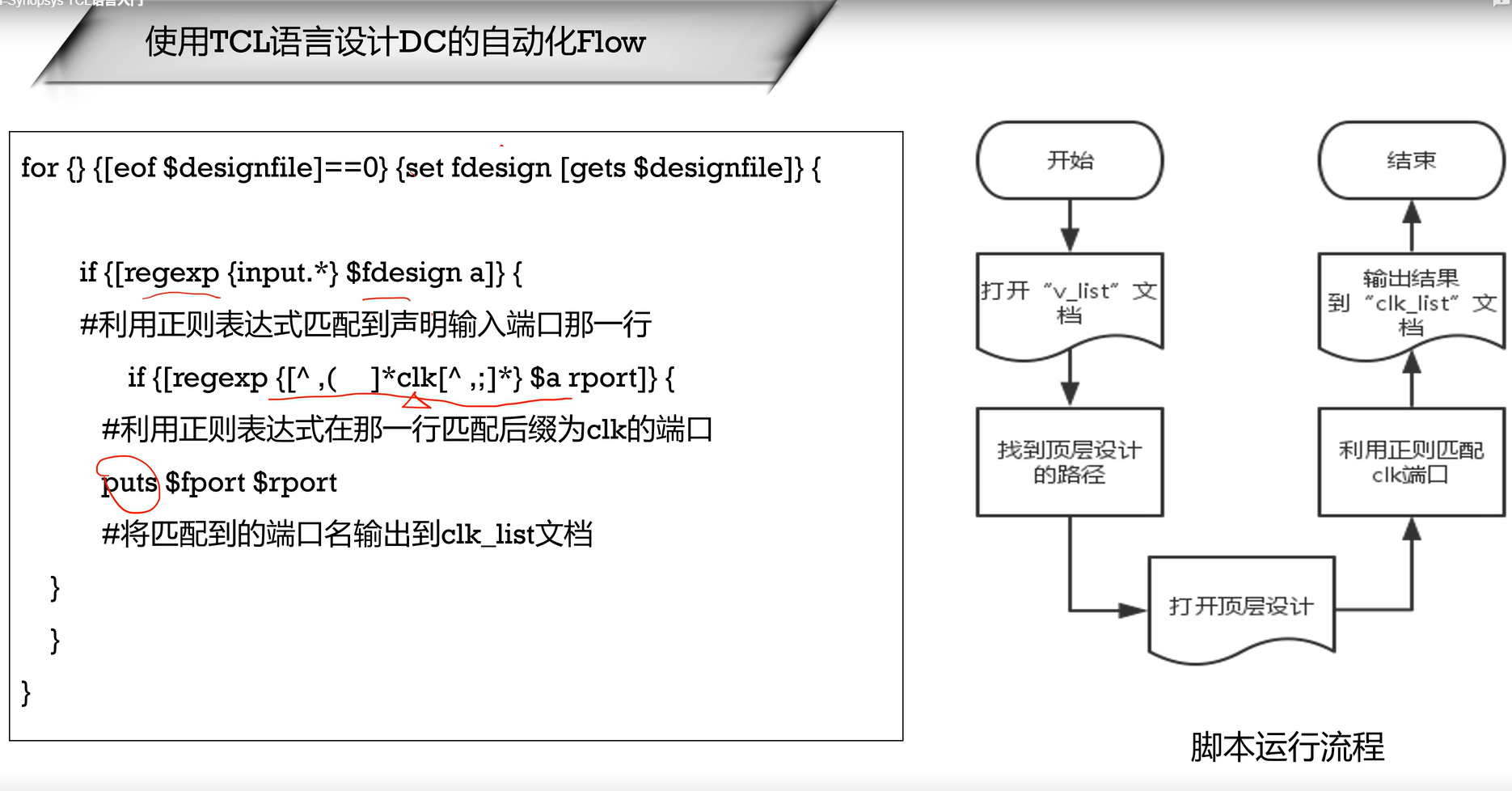

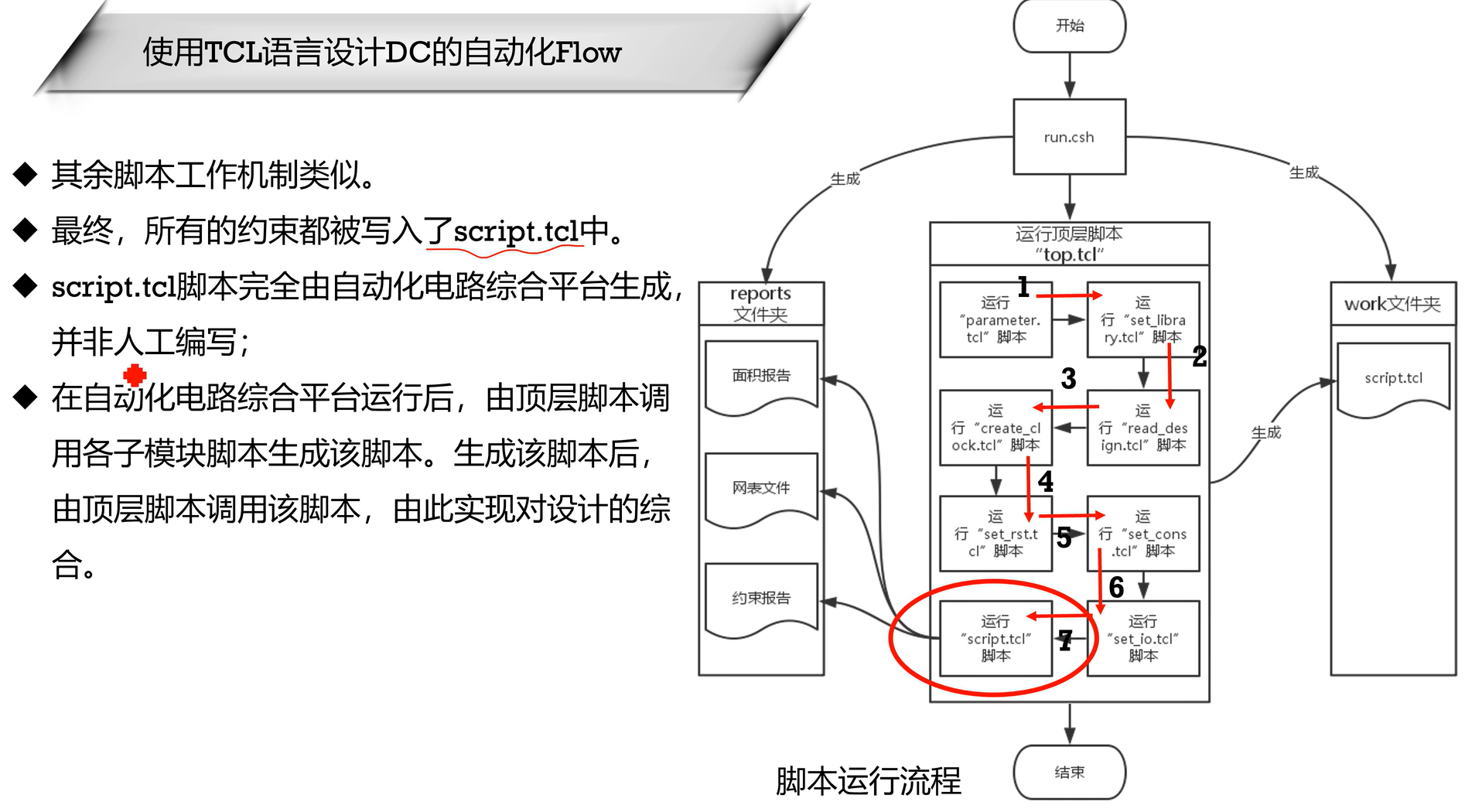

6.3 使用TCL语言设计DC的自动化Flow

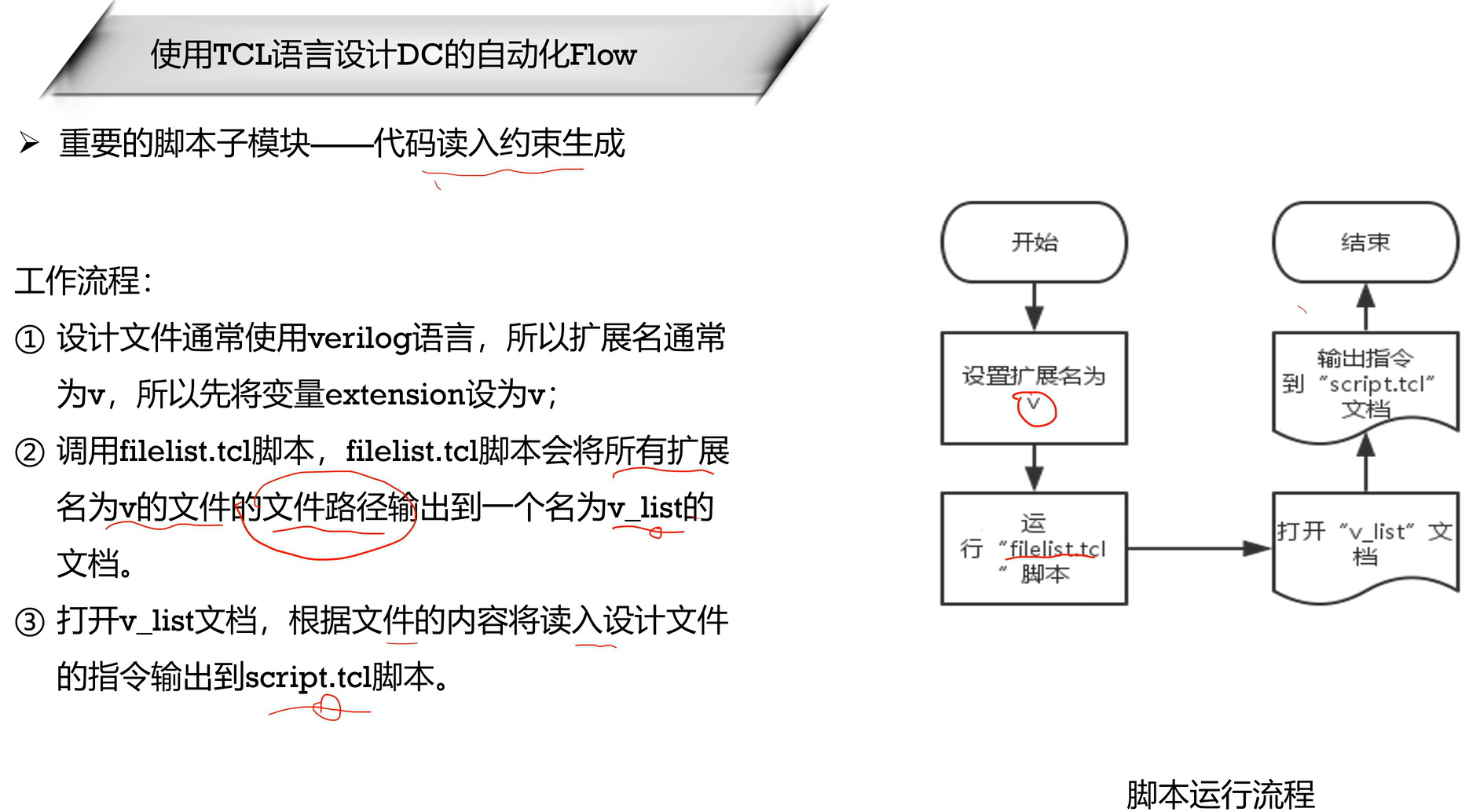

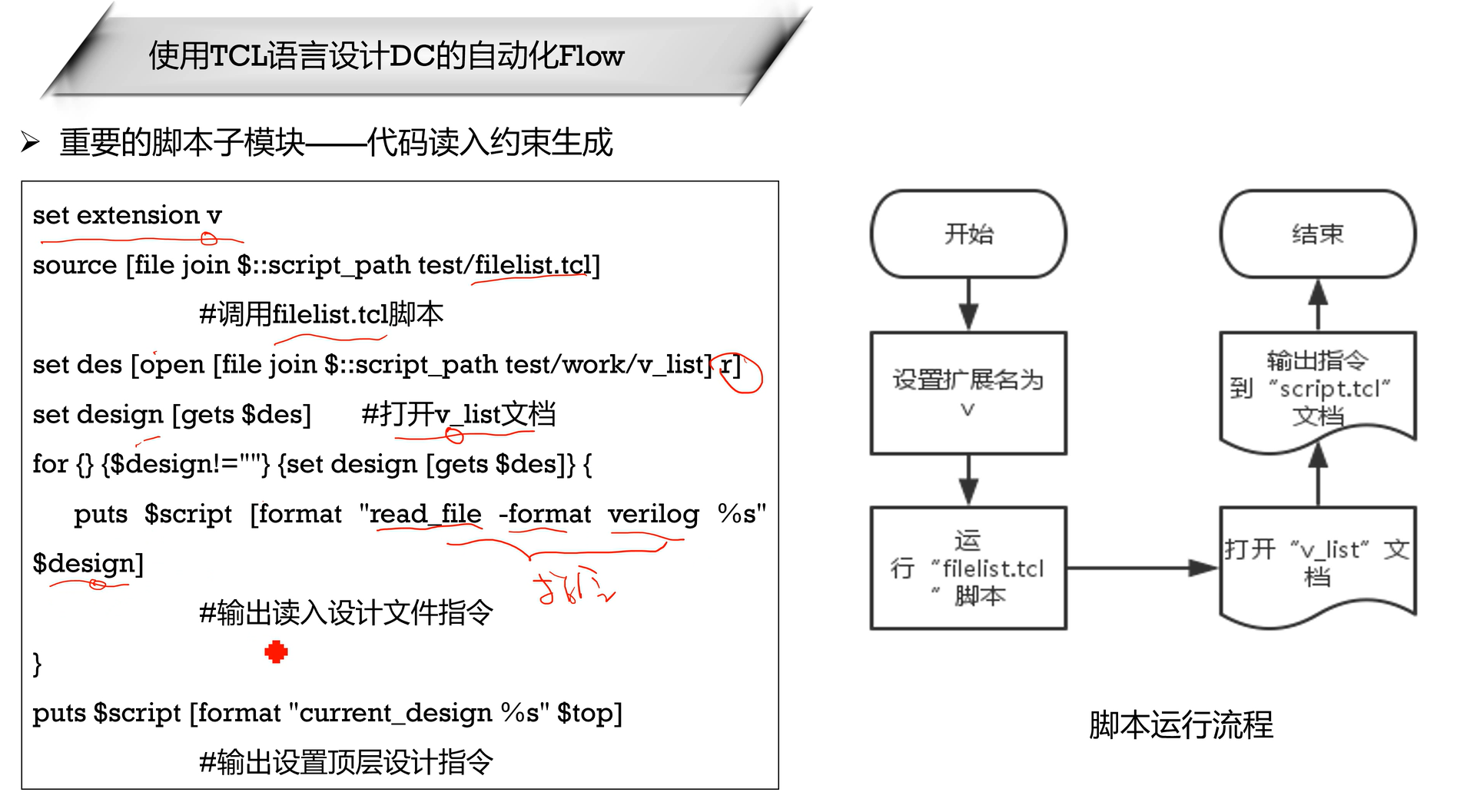

代码读入与约束生成

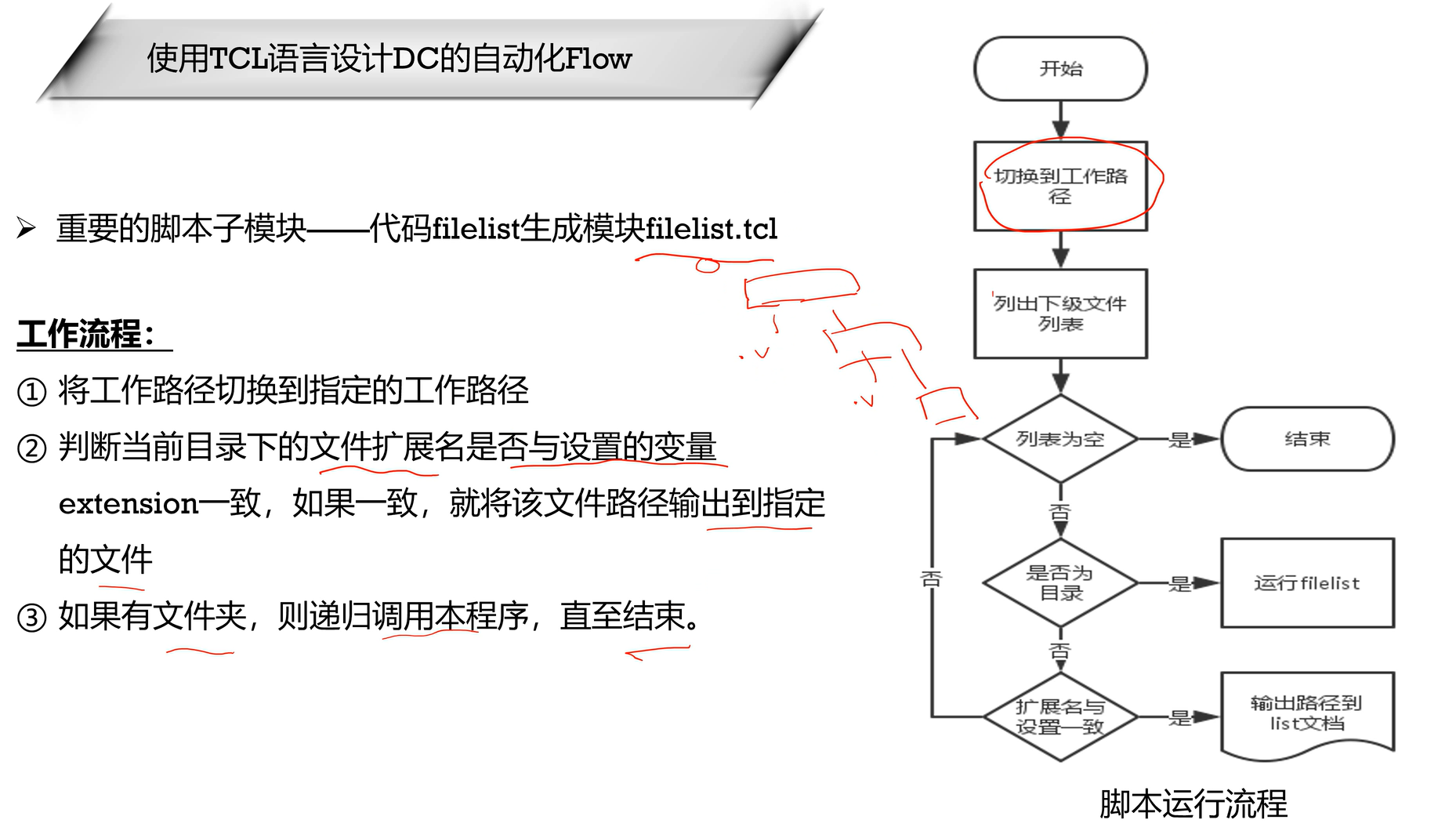

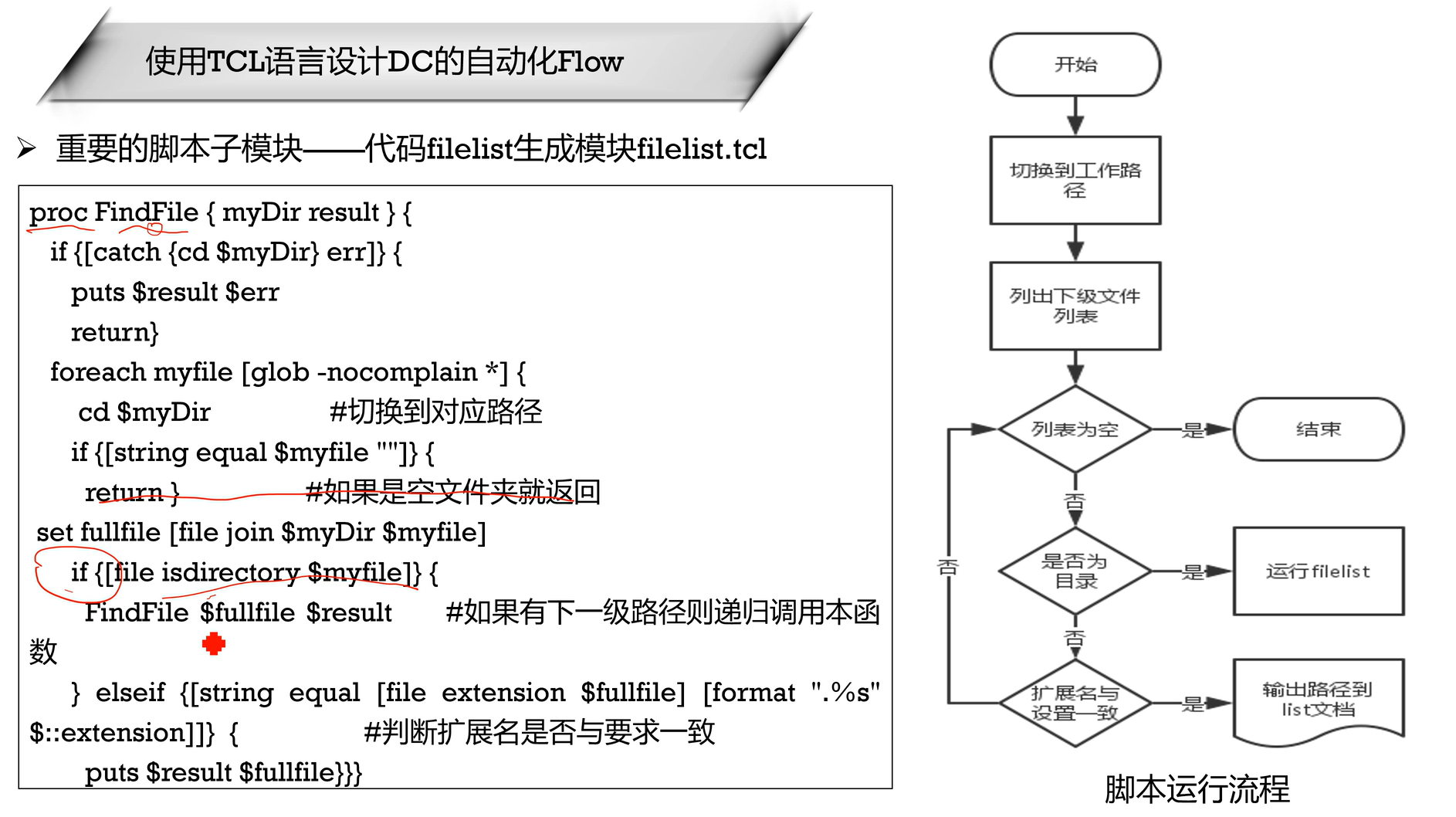

filelist.tcl–代码filelist读入生成模块

find_clk.tcl–时钟约束生成子模块

二、STA静态时序分析

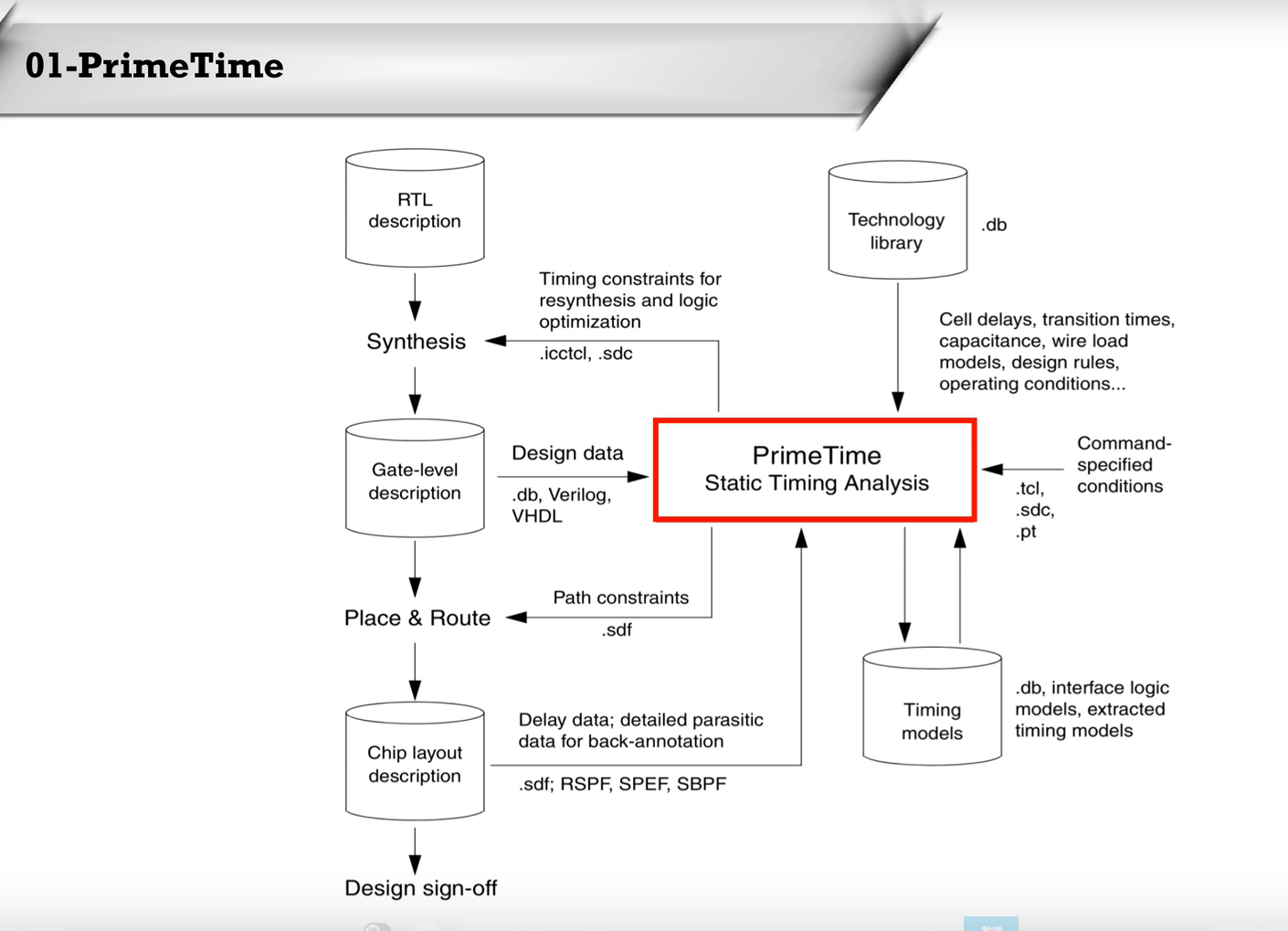

1. PrimeTime

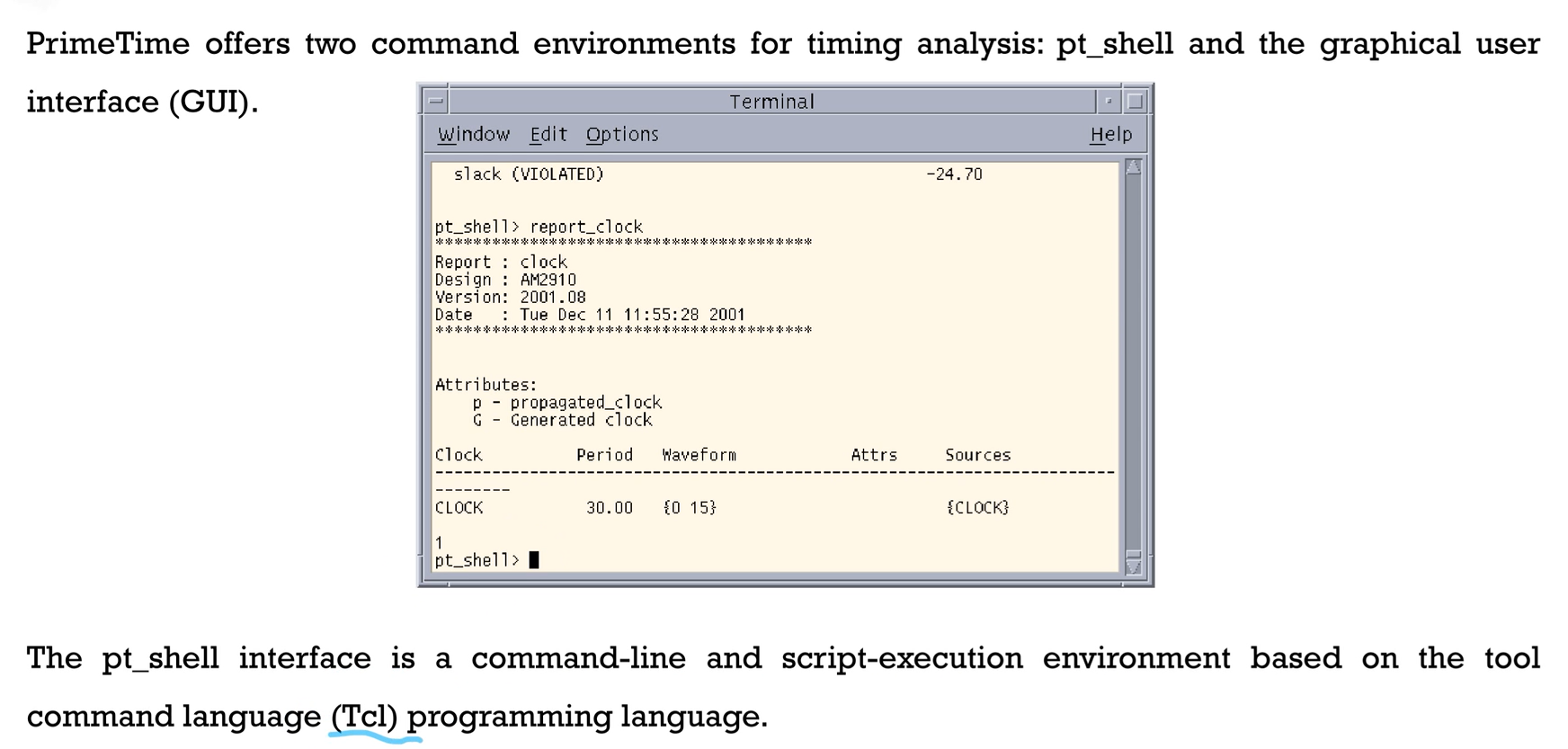

1.1 PT命令行模式

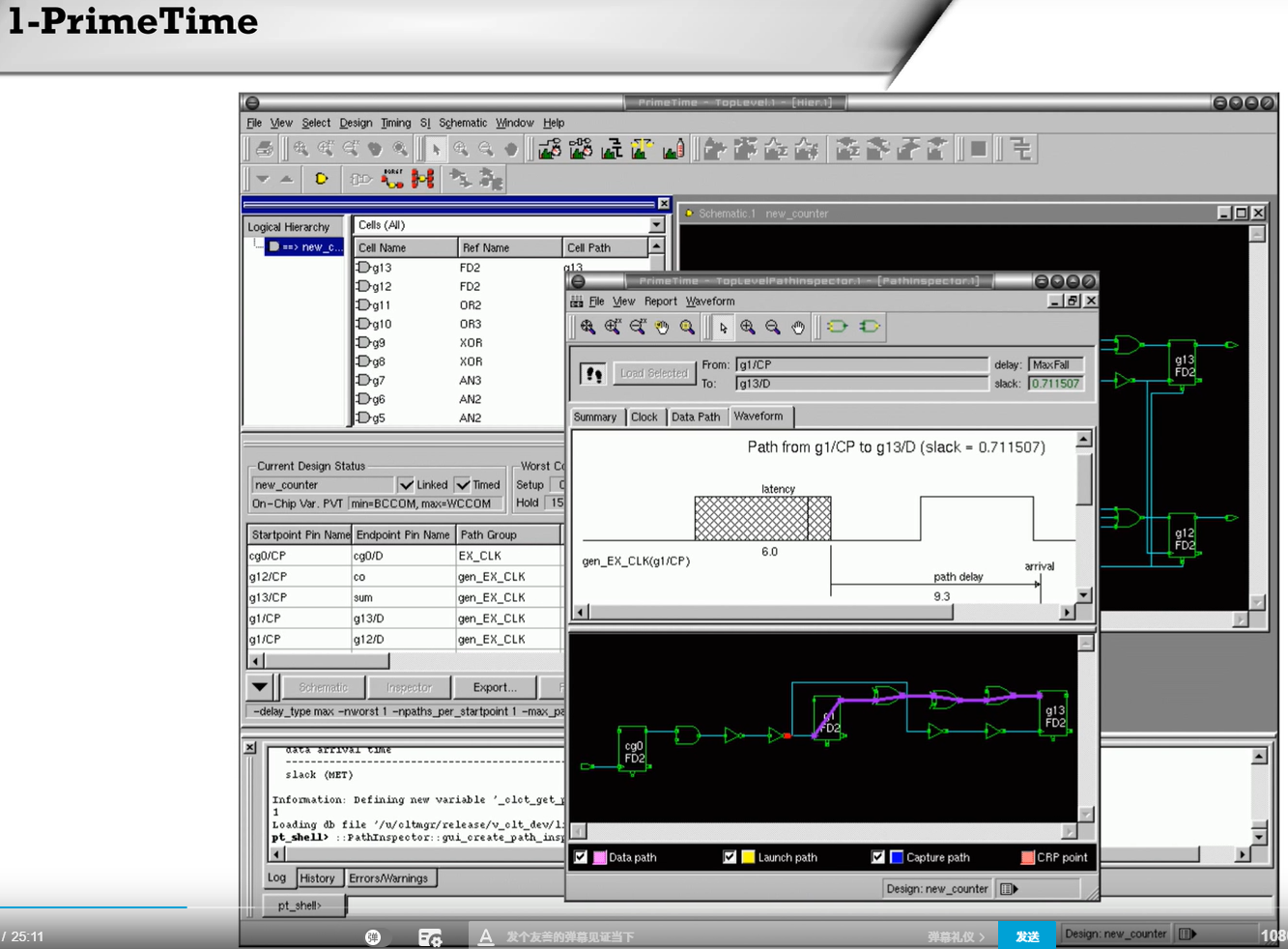

1.2 图形模式

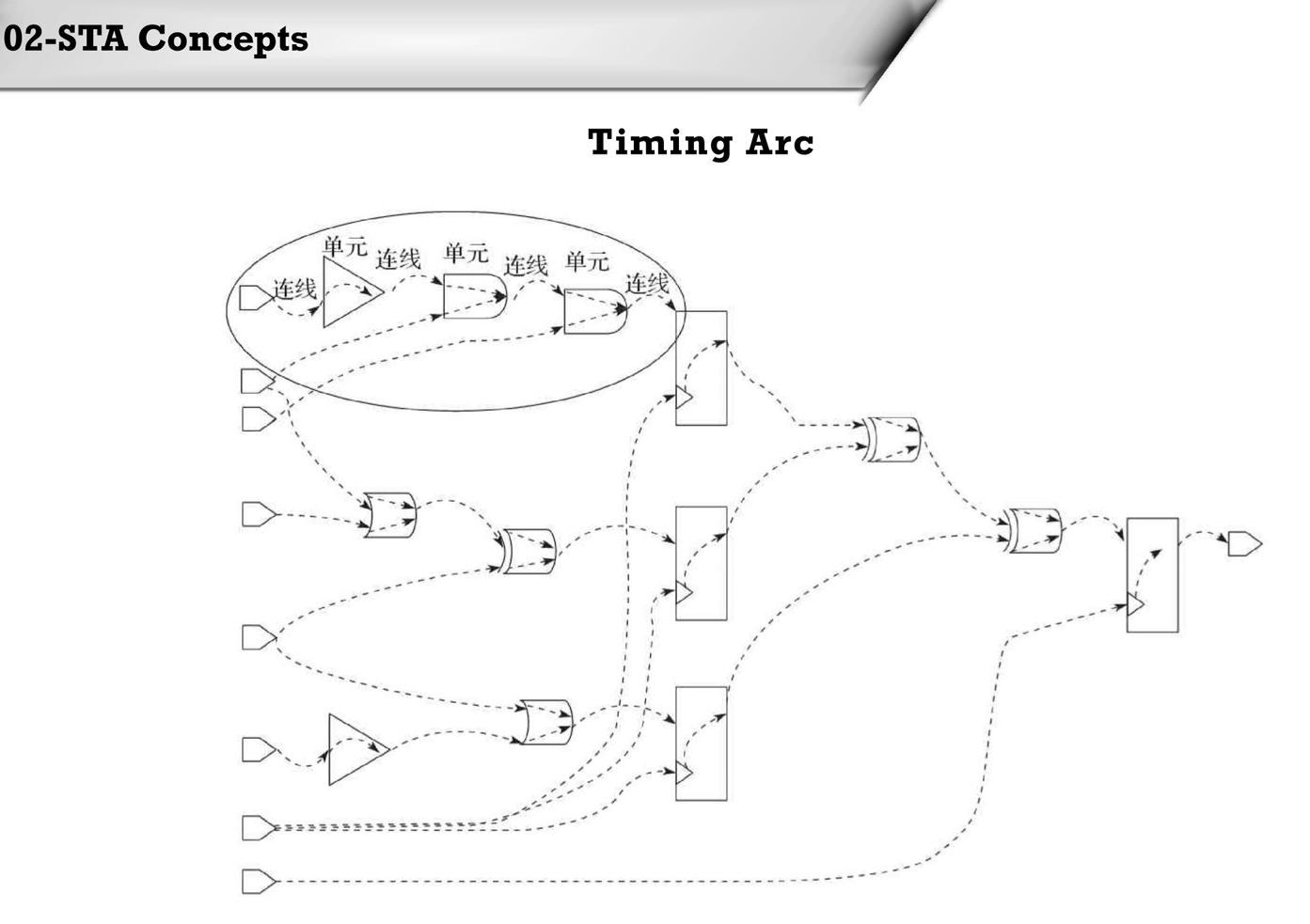

2. 静态时序分析时序弧

又分为连线延迟和单元延迟

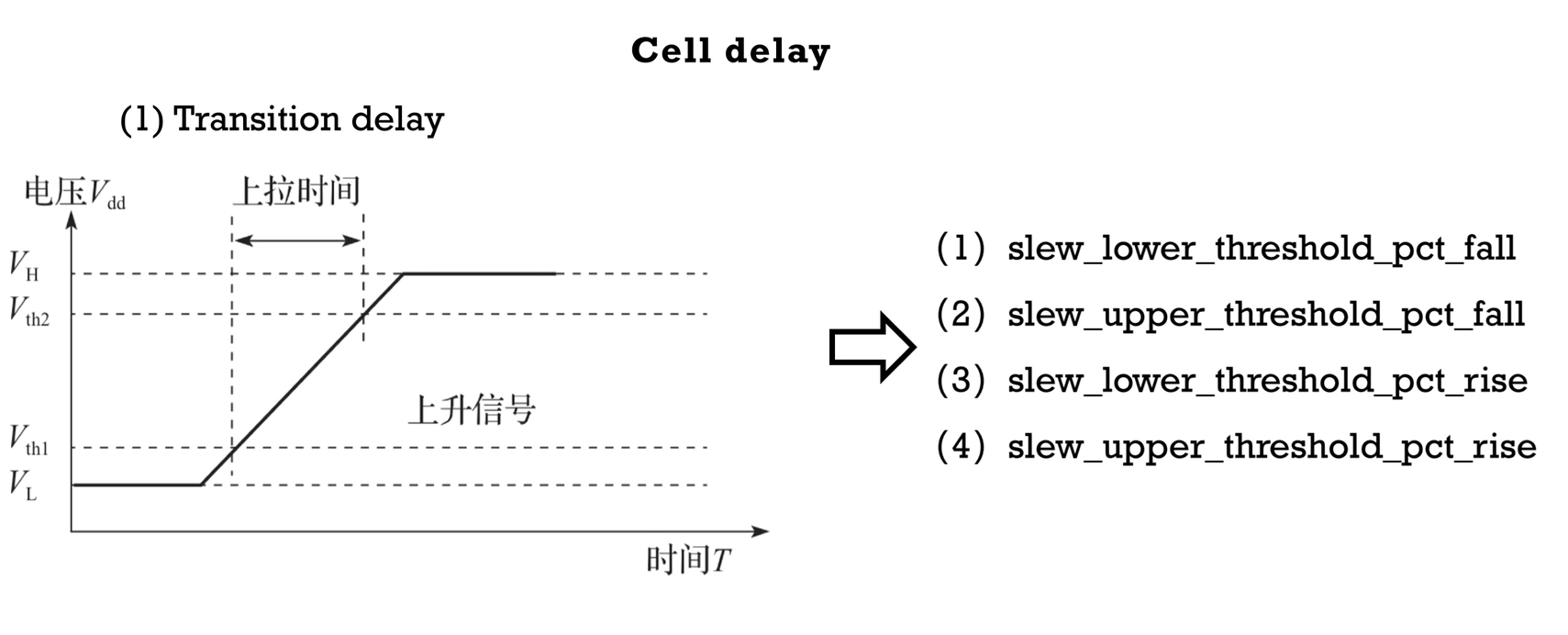

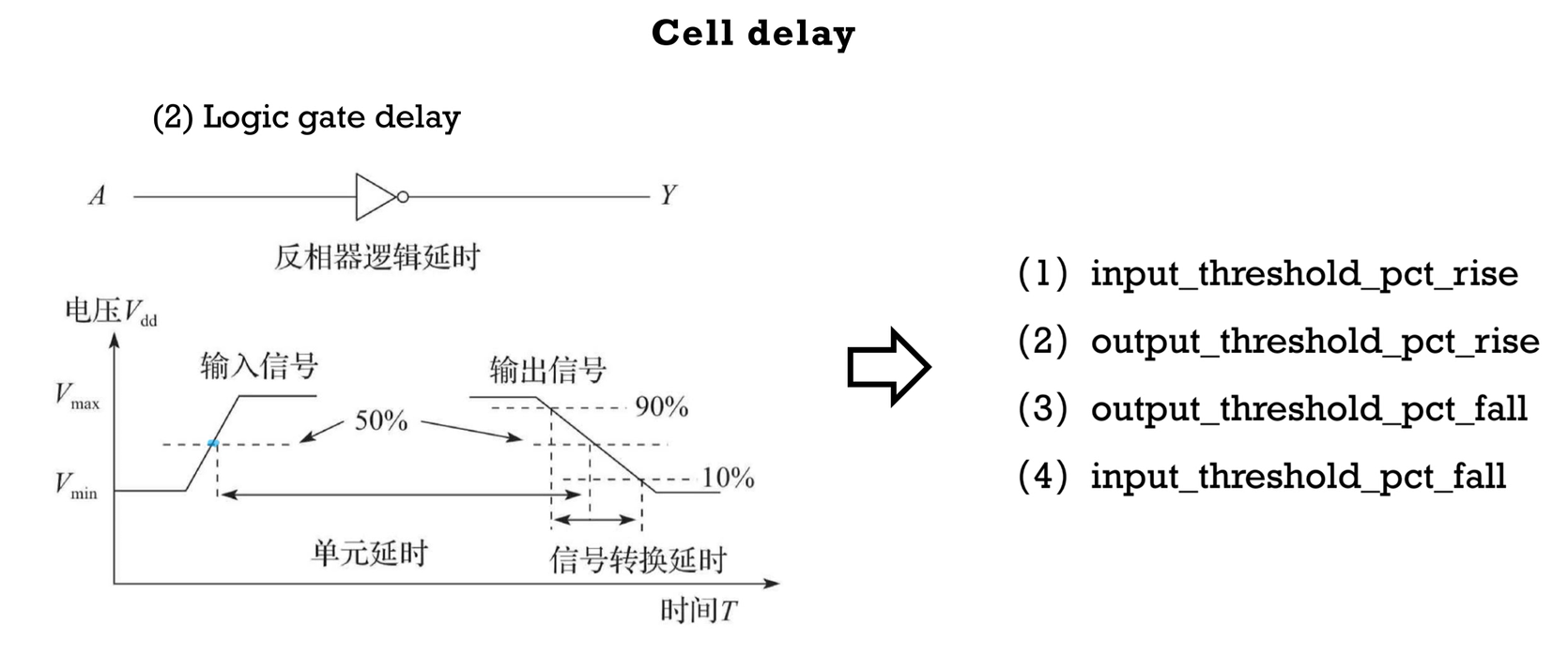

2.1 单元延迟–Cell delay

反转延迟–Transition delay

逻辑延迟–Logic gate delay

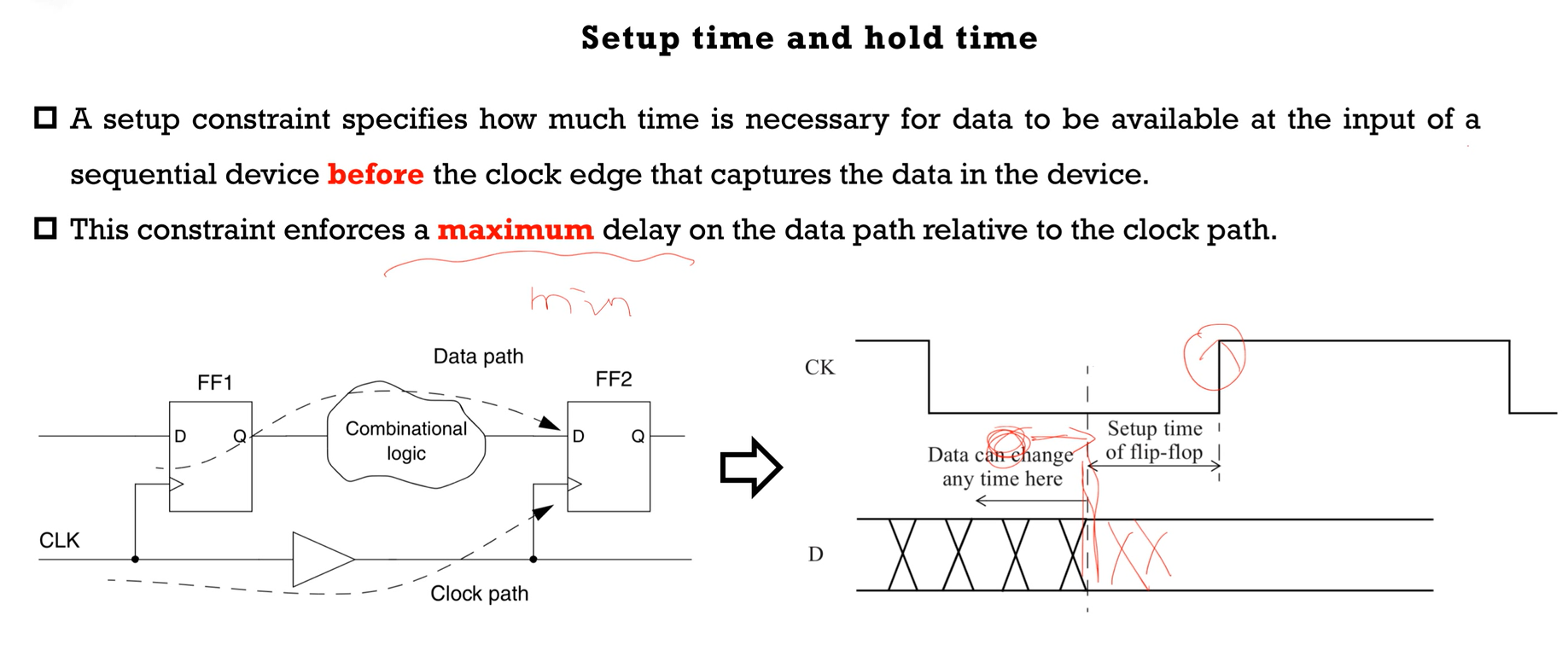

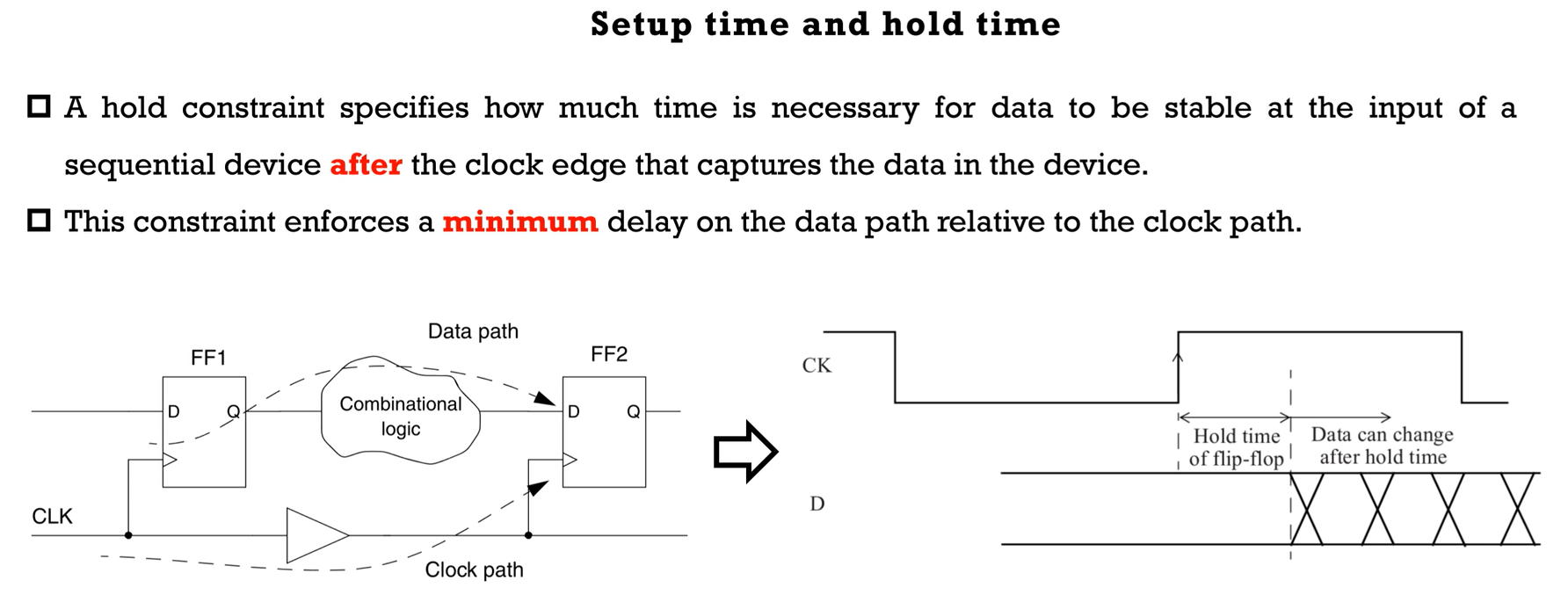

3. 建立时间与保持时间

3.1 setup time

建立时间约束电路最大延迟,所以建立时间决定电路的最大时钟频率

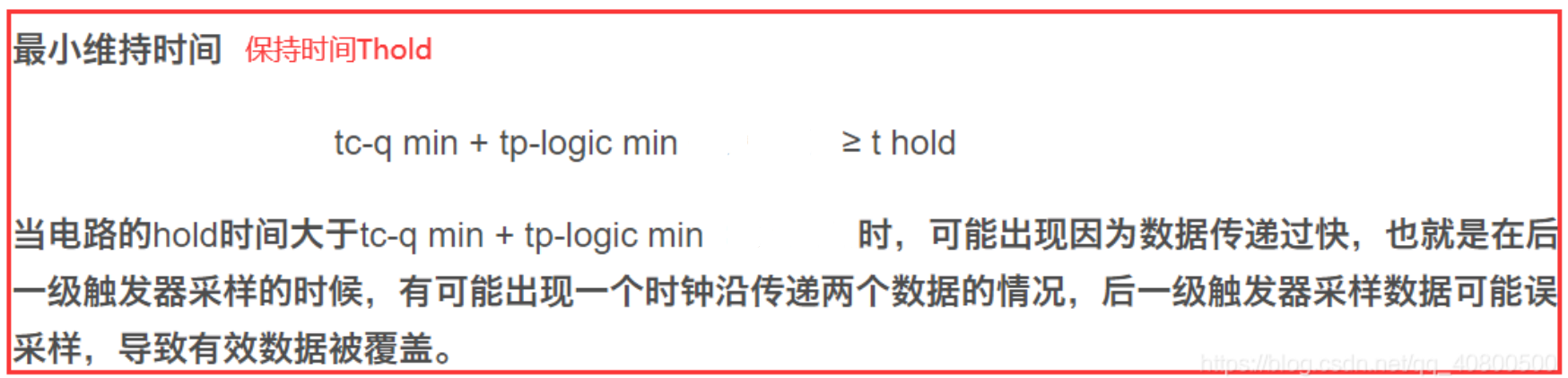

3.2 hold time

保持时间约束电路最小延迟,若不满足保持时间,则发生数据在当前时钟沿发送且在当前时钟沿被采集

3.3 避免两种时序违例(Tsu与Thold计算)

⭐ 3.3.2 消除hold timing违例

理论上可以通过增大数据路径延迟,或者减小时钟路径延迟来改善

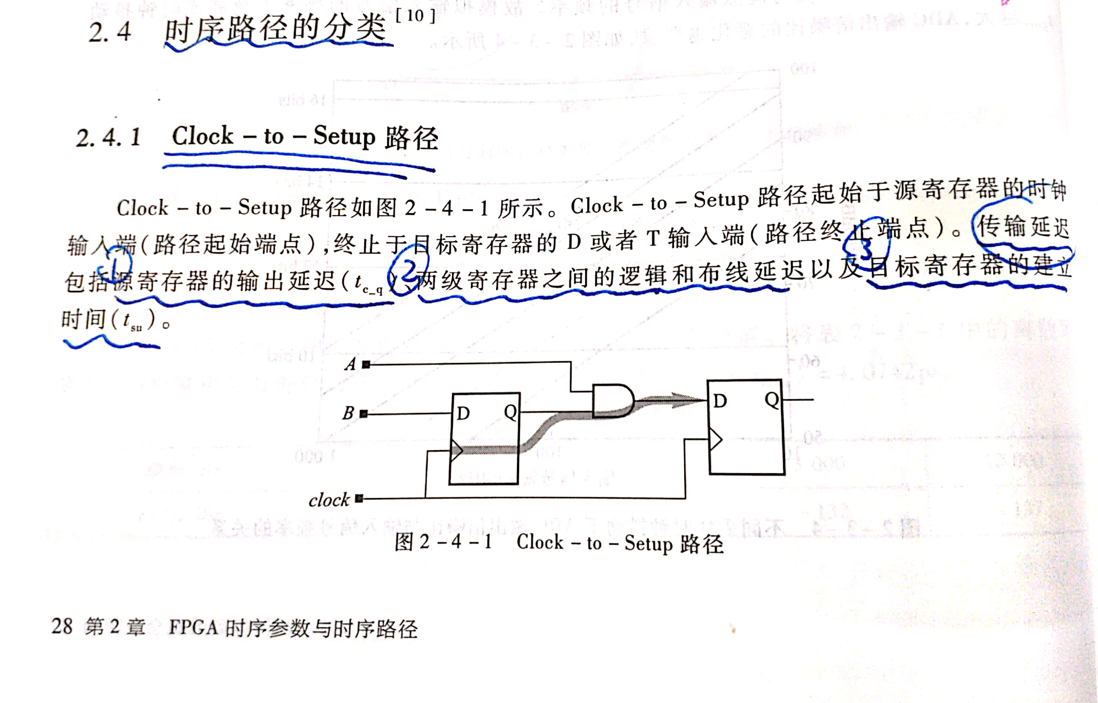

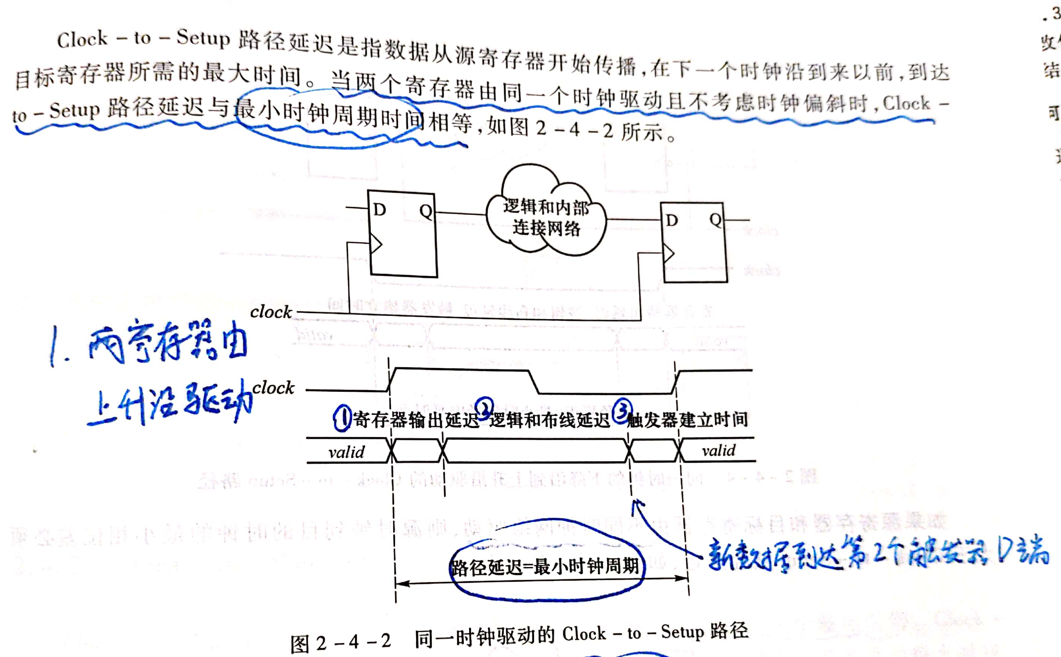

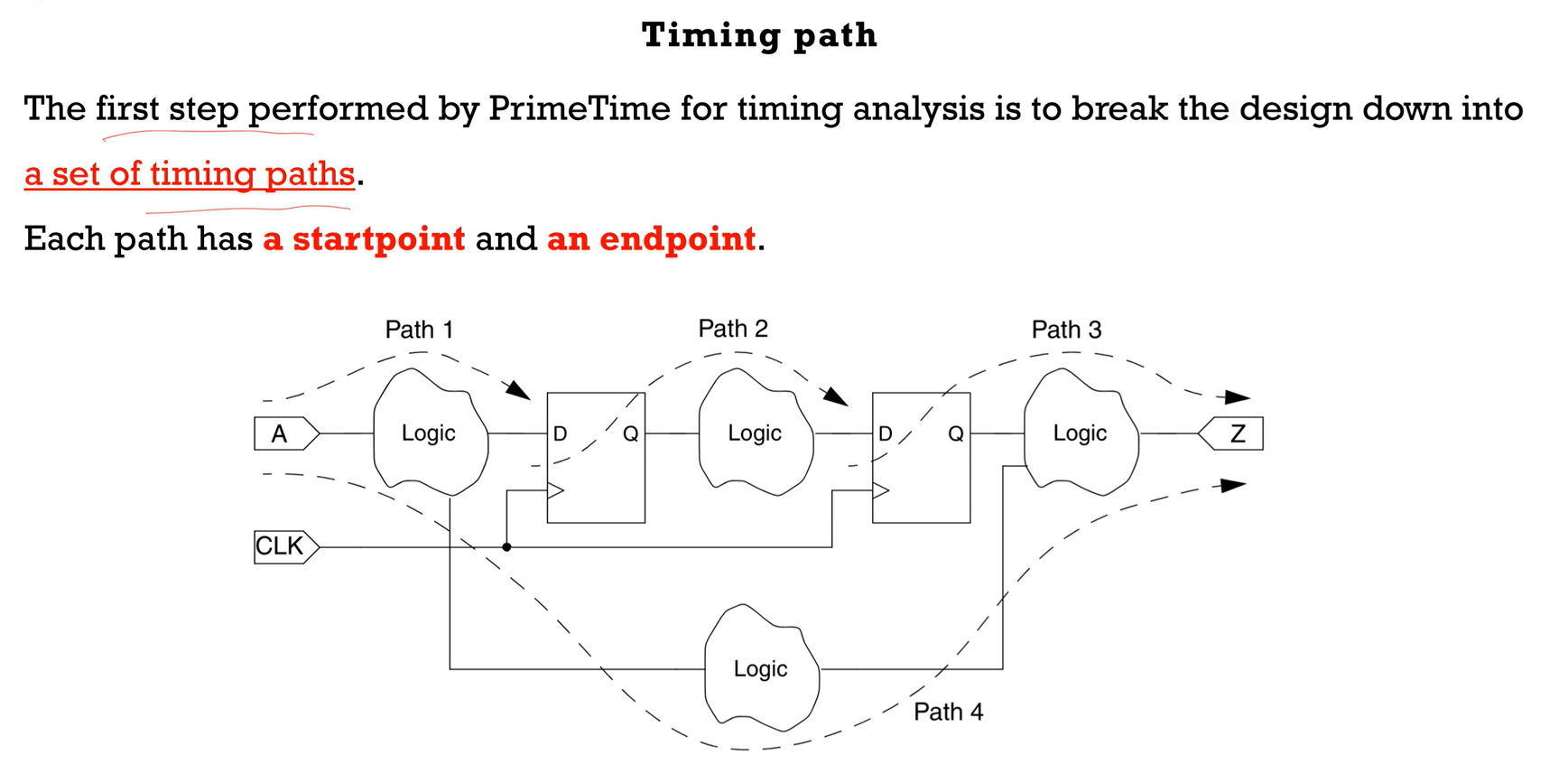

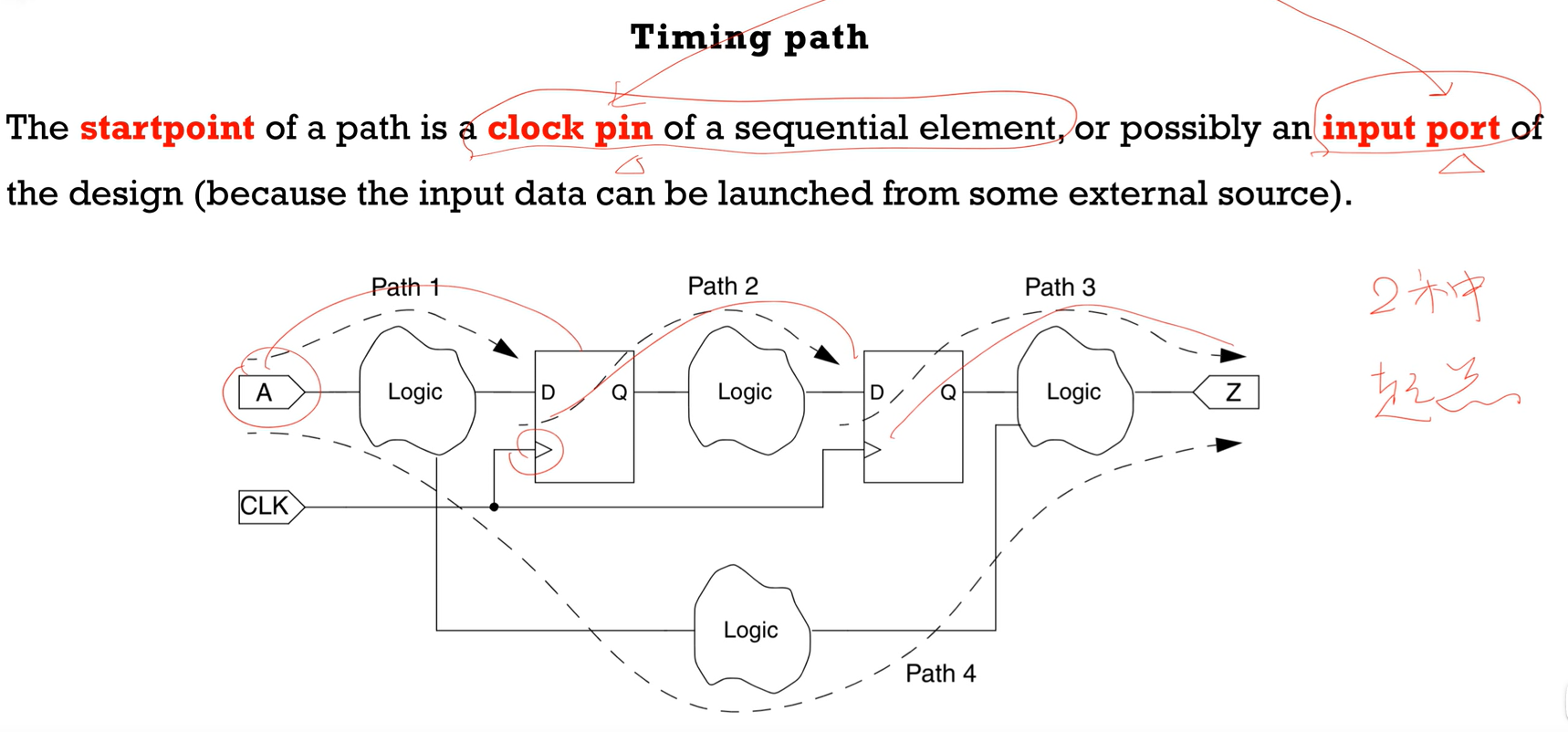

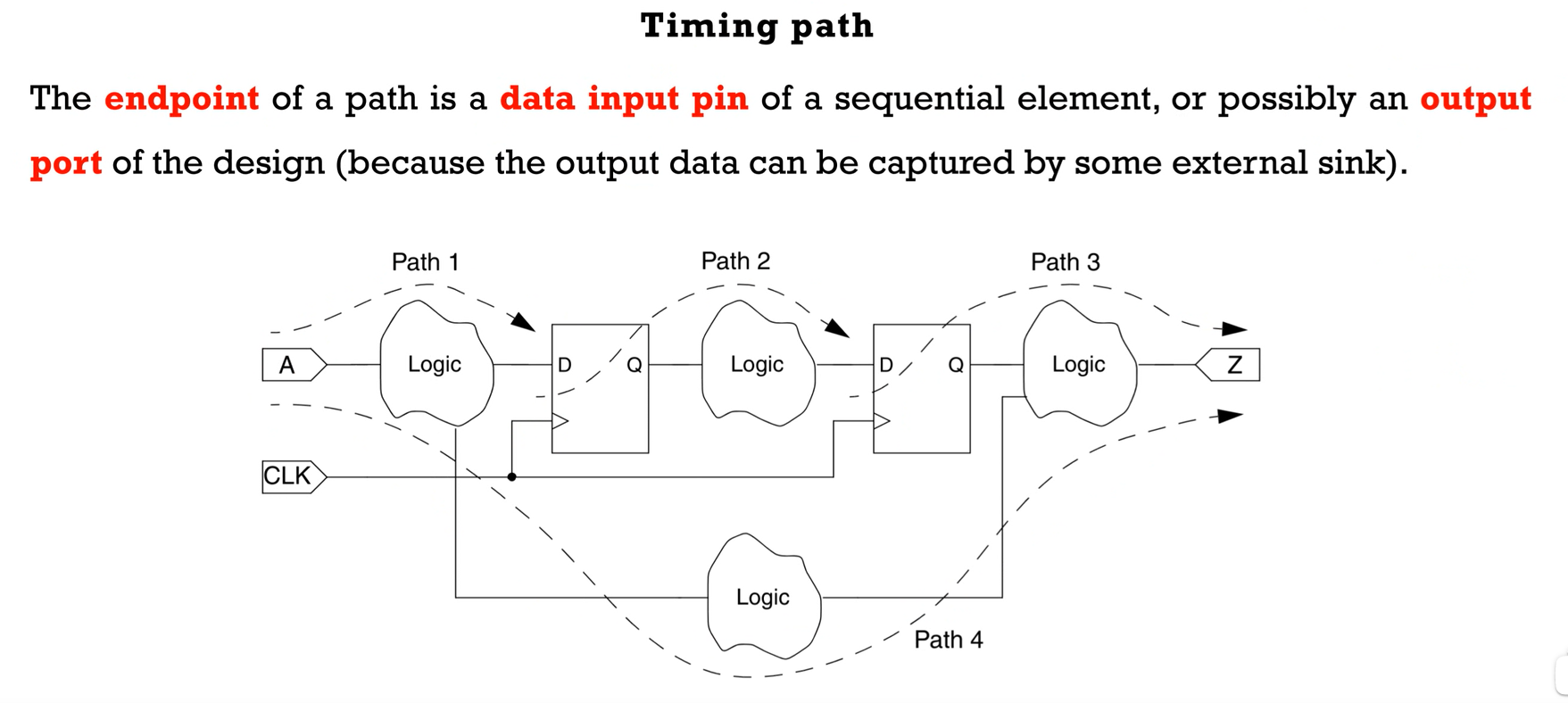

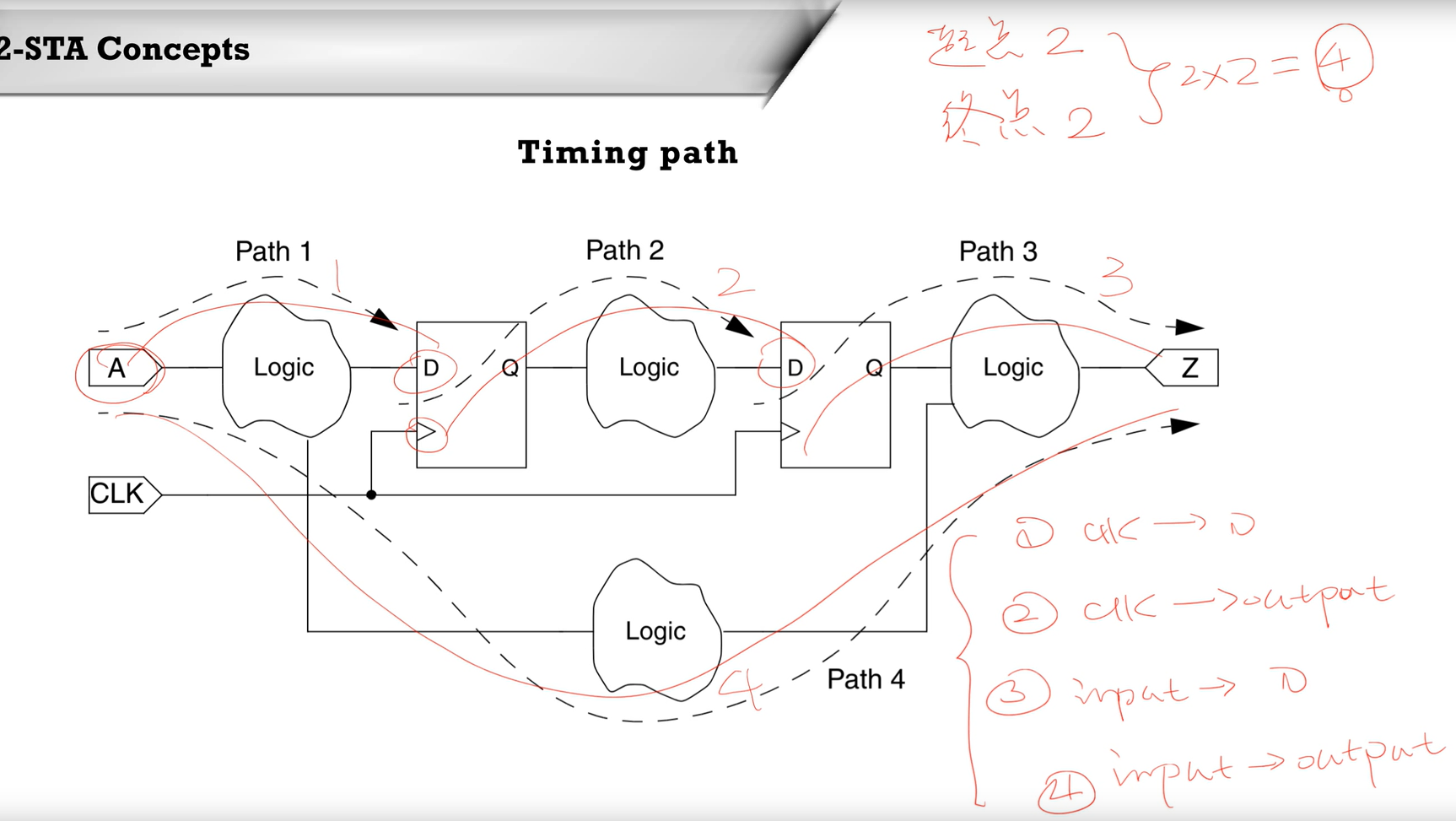

4. 时序路径

4.1 两种起点:clock pin和input port

4.2 两种终点:data input pin和output port

4.3 四种时序路径

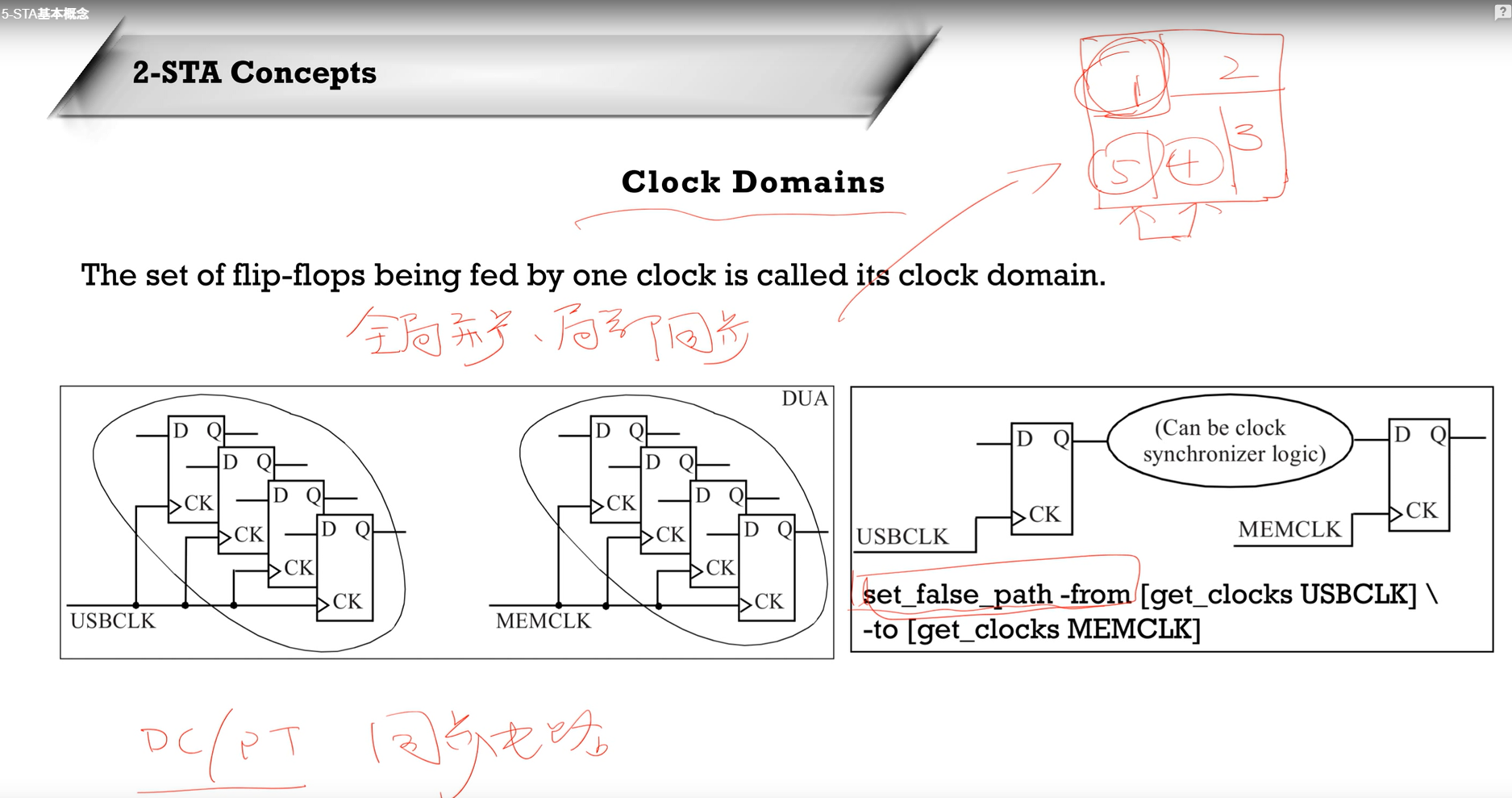

5. 时钟域

SOC全局异步,局部同步。

DC/PT处理的都是同步电路。

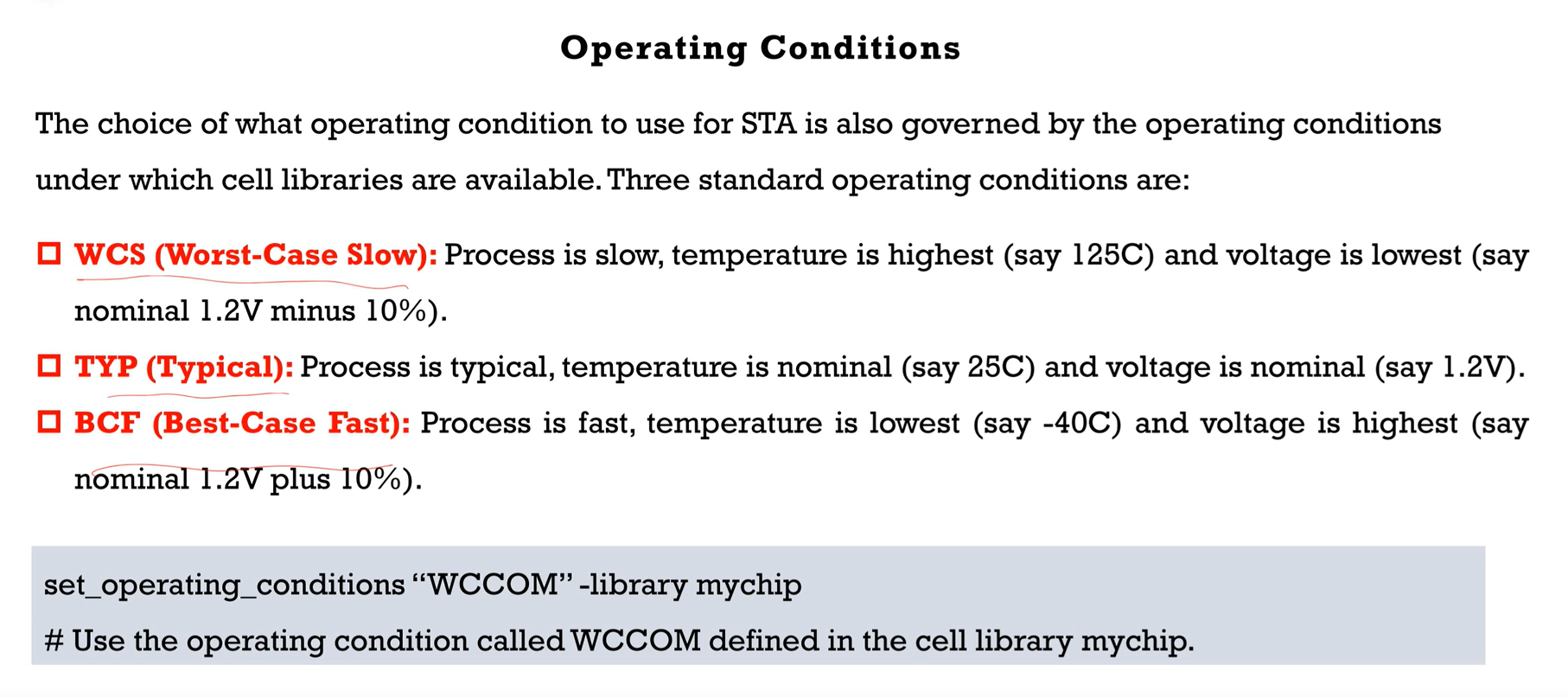

6. 操作条件

PVT: 工艺制成,电压和温度

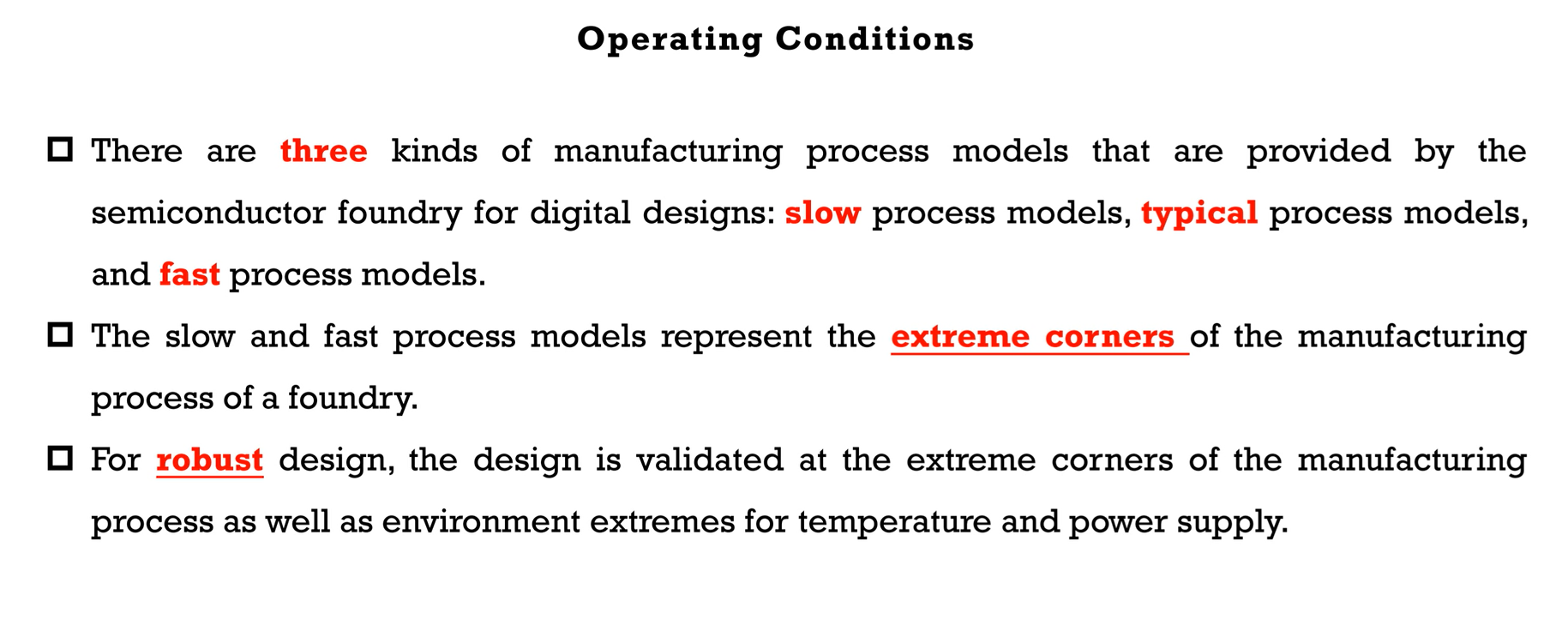

PVT一般分三种:比较慢的,典型的,比较快的。用最慢和最快的极限条件测试,最慢查setup,最快查hold

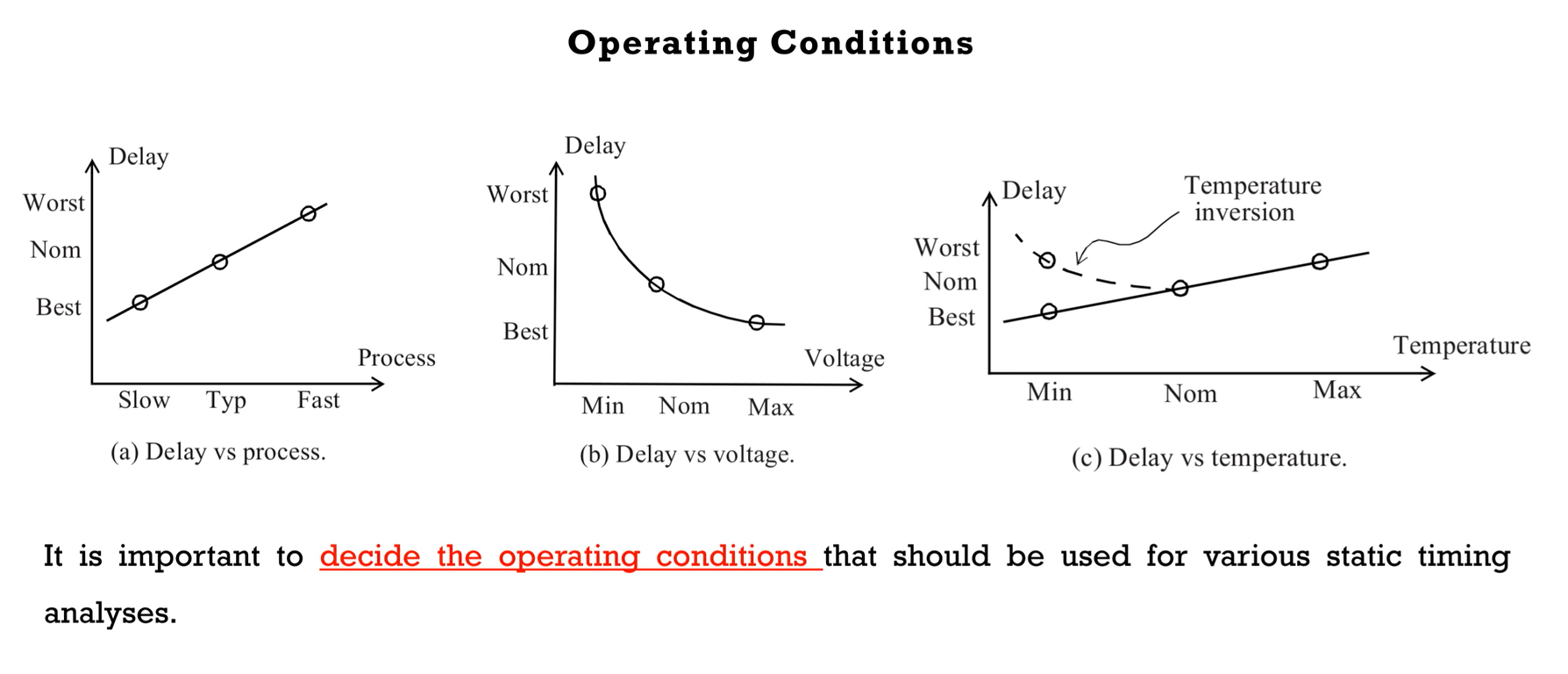

芯片工艺制成越大,延迟越大;

电压越高,延迟越小;

温度越高,延迟越大;

通常讲,高温+低电压看setup time;

低温+高电压看hold time。

三、相关计算

四、时钟偏斜

由于时钟布线网络存在传输延迟,

五、时钟抖动

概述

时钟抖动指在芯片的某一给定点上时钟周期发生暂时的变化,即相邻两个时钟周期之间存在的时间差值。

影响

在高速数字系统中,时钟或振荡器波形的抖动会限制一个数字I/O接口的最大速率,不仅如此,还会增大通信链路的误码率,甚至限制模数转换器的动态范围。

产生原因

相邻两个时钟周期的误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,时钟信号传播过程中的噪声对其也有影响。

时钟抖动分确定性抖动和随机性抖动。

最后

以上就是健康奇异果最近收集整理的关于TCL与STA静态时序分析----邸志雄课程一、TCL语言二、STA静态时序分析三、相关计算四、时钟偏斜五、时钟抖动的全部内容,更多相关TCL与STA静态时序分析----邸志雄课程一、TCL语言二、STA静态时序分析三、相关计算四、时钟偏斜五、时钟抖动内容请搜索靠谱客的其他文章。

发表评论 取消回复