1. WNS & TNS

worst negative slack:最差slack值

total negative slack:所有负slack之和

2. DC & DCG

dc使用线性负载模型预估延迟,网表不含物理布局信息;

dcg在PR布局后,将子模块物理布局信息读入,使用milkway库进行综合。

3. overconstrained

MOSFET制造工艺随机性偏差,不同批次晶圆,同一晶圆不同芯片,同一芯片不同区域都可能存在偏差,生产出的芯片速度为正态分布。所以综合时对时钟加额外约束,DC一般过约30%,DCG对走线延时估计更加精确,一般过约10%即可。

4. max_transition & max_fanout

厂家工艺库cell输入引脚规定最大transition,连接线大于该值会有DRC违例,如果DRC违例,需要添加足够的buffer或更换驱动能力更高的单元。所以前期综合时往往需要约定更严格的max_transition来获得更好的时序。

最大扇出max_fanout属于DRC的另一条违例,同理需要前期的严格约定。

5. set_dont_touch & set_size_only

set_dont_touch表示子模块,cell,net等不希望工具修改或替换。当设计较大时,时钟复位信号会有较大扇出,工具自动在时钟复位网络上增加buffer以保证延迟在设定范围内,set_dont_touch_network表示时钟网络不希望工具修改,后端会通过专门时钟树实现。

set_size_only表示只允许工具改变cell尺寸大小。

6. multi_vth & multi_bit

常用MOS管分为低/标准/高阈值电压(lvt/svt/hvt),vth越低,速度越快,功耗越高,工具优化时用不同管切换收敛时序,可以约束比例和插入方式,设置如下:

set_multi_vth_constraint

–lvth_percentage$lvt_ratio

–lvth_groups {lvt}

多个电路共用时,例如多bit触发器合并可以共享内部时钟buffer,可以减小电路面积,降低电路功耗,设置如下:

set_compile_multibit_lib_analysis true

set_hdlin_infer_multibit default_all

7. set_case_analysis

给设计中的端口或pin指定高/低电平恒值或指定上升沿/下降沿做时序检查。

8. create_clock & create_generated_clock

对电路中实际存在的时钟定义有2种,1种是连接端口的时钟,设置如下:

create_clock –name CLK –period 10

–wave{t0 t1} [get_ports xx]

1种是内部生成时钟,例如根据源时钟分频或倍频得到的时钟,设置如下:

create_generated_clock

–name gen_CLK

–div/-multi n –master CLK [get pins xx]

9. set_false_path

避免工具分析和约束没有必要做时钟检查的路径,例如异步路径,测试路径,某些条件下不发生的路径等等。

10. set_multicycle_path

同步电路设计中,一条路径时延太长,无法满足时钟周期setup时间,又不方便触发器分割流水线,且数据总是保持几个周期不更新,则可以降低时钟周期。设置如下:

set_multi_path 2 –setup from xx to xx

–start/-end (默认-end)

set_multi_path 1 –hold from xx to xx

–start/-end(默认-start)

11. input_delay & output_delay

假设输入输出端口外部都有一段触发器,并将内部触发器时钟向外延伸模拟与真实时钟同源同频的虚拟时钟VCLK,input_delay设置如下:

Input_delay –max 70%

//用作setup检查,越大越严格

Input_delay –min 0

//用作hold检查,越小越严格

output_delay设置同理有-max/-min,相当于把后级触发器的setup/hold time算进数据路径时间,将后级视为理想触发器。

12. uniquify

设计中多次例化子模块生成唯一实体定义。RTL网表中模块按照层次引用,同一个被引用模块名相同,综合中网表被打平,多次例化子模块避免冲突使用ref_name,他们应指向唯一实体。

13. svf文件

综合时,编译优化或一些命令会导致RTL代码到网表例化名称的转变,如ungroup/uniquify;这些改变会被记录在svf文件中。形式验证时会读入该文件,做比较点的匹配和验证。

DC自动生成default.svf文件,如果想自己设置,可在读入文件之前用命令set_svf,综合后需要手动关闭否则形式验证读入时会报错,关闭使用命令set_svf –off。

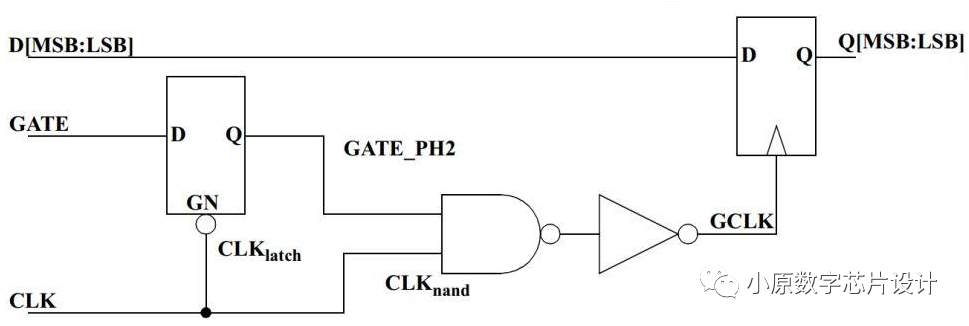

14. ICG(set_clock_gating_style)

条件赋值语句,case语句,for循环等RTL代码都可以产生时钟门控,电路图如下:

综合时可以设置-sequential_cell选择latch_based或latch_free,可以设置-positive/negetive_edge_logic,positive且latch_based模式时用nand,latch_free模式时用nor,negetive反之。

15.读入设计有两种方法

analyze <所有设计文件>

elaborate

//读入文件,检查语法错误,转化中间文件(仅支持verilog/ VHTL)。

read_file <所有设计文件>

current_design

link

//读入文件,不产生中间格式文件,不自动执行link需要手动添加。

16. compile_ultra & compile

compile_ultra相比于compile,需要额外license,DW库,综合时序更好。

撰文 | Tinsika

编辑 | Tinsika

最后

以上就是文静黑米最近收集整理的关于delay 芯片时序output_【芯片设计】DC综合扫盲专题的全部内容,更多相关delay内容请搜索靠谱客的其他文章。

发表评论 取消回复