dc综合约束:时钟约束

1、时钟如何约束

sdc约束采用的tcl脚本语言编写,时钟产生的sdc命令是create_clock. 指令格式为

create_clock -period period_value # 时钟周期

-[source_objects] # 时钟源

-[name clock_name] #给时钟命名

-[waveform edge_list] #时钟占空比分布

-[add] #

-[-comment comment_string]

举例如下:

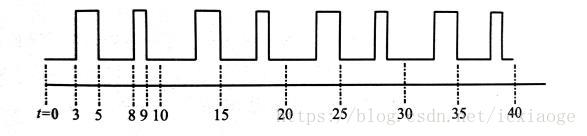

create_clock -period 10 -name host_clk -waveform [3 5 8 9] [get_ports host_clk]

时钟来源于模块输入接口host_clk,命令为host_clk, 周期为10ns,0ns处于低电平,3ns上升沿,5ns下降沿,8上升沿,9ns下降沿,以10ns为周期循环。

时钟周期: -period period_value

-period 定义时钟周期,单位为ns。

时钟源: -[source_objects]

时钟源对象可以是模块端口、引脚、网络。源对象为端口时采用get_ports,网络连线采用get_nets,器件引脚采用get_pins。如下所示:

#采用模块端口clk作为时钟源

creat_clock -period 10 -name host_clk [get_ports clk]

#采用连线n作为时钟源

creat_clock -period 10 -name soc_clk [get_nets n]

#采用触发器引脚作为时钟源

creat_clock -period 10 -name div_clk [get_pins ff/p]

时钟名称: -[name clock_name]

-name 后定义时钟名称,名称定义后在其他地方调用的时候只需要采用时钟名称即可,方便服用,便于理解

时钟占空比 -[waveform edge_list]

改选项用于指定时钟占空比,忽略时表示占空比为50%。

create_clock -period 10 -name host_clk -waveform [5 10 ] [get_ports clk]

create_clock -period 10 -name host_clk [get_ports clk]

以上两个时钟约束表示的含义完全相同,时钟在5ns处于上升沿,10ns处于下降沿,以10ns为周期循环。

复杂的脉冲信号可以通过多个参数进行描述,如下所示

create_clock -period 10 -name host_clk -waveform [3 5 8 9] [get_ports clk]

3ns和8ns时钟处于上升沿,5ns和9ns处于下降沿。

同源多时钟 -add

如图所示,一个多了选择器从电路外部驱动端口,多路选择器的两个时钟具有不同的特性,因此,为了描述时钟特性,需要使用-add。

如下所示:

create_clock -name c1 -period 10 [get_ports clk]

create_clock -name c2 -period 20 [get_ports clk] -add

如果不使用-add,后面一条时序约束将会覆盖前一条约束,导致dc环境中,时钟clk由c2驱动而没有选择器。

2、虚拟时钟如何约束

在一些情况下,模块a输入数据data_in由clk0驱动,而clk0并不是模块a的输入信号。

此时需要定义定义虚拟时钟来约束输入信号data_in,定义虚拟时钟不需要时钟源,只有period、waveform、name选项。

create_clock -period 10 -name v_clk -waveform [0 5]

3、生成时钟如何约束:create_generated_clock

在ic设计中,有时会使用时钟分频器、门控时钟等,会出现多个时钟来源于同一个主时钟的情况,所以为了更加真实的描述时钟关系,此时需要表明生成时钟是由哪个主时钟生成的。

最后

以上就是直率白昼最近收集整理的关于DC综合约束:时钟约束的全部内容,更多相关DC综合约束内容请搜索靠谱客的其他文章。

发表评论 取消回复