实验任务:

设计一个四人参加的智力竞赛抢答计时器。当有某一参赛者首先按下抢答开关时,相应的显示灯亮并伴有声响,此时抢答器不在接受其他输入信号。

电路具有回答问题时间控制功能。要求回答问题时间小于等于60s(显示为0~59),时间采用倒计时方式。当到达限定时间时,发出声响以表示警告。

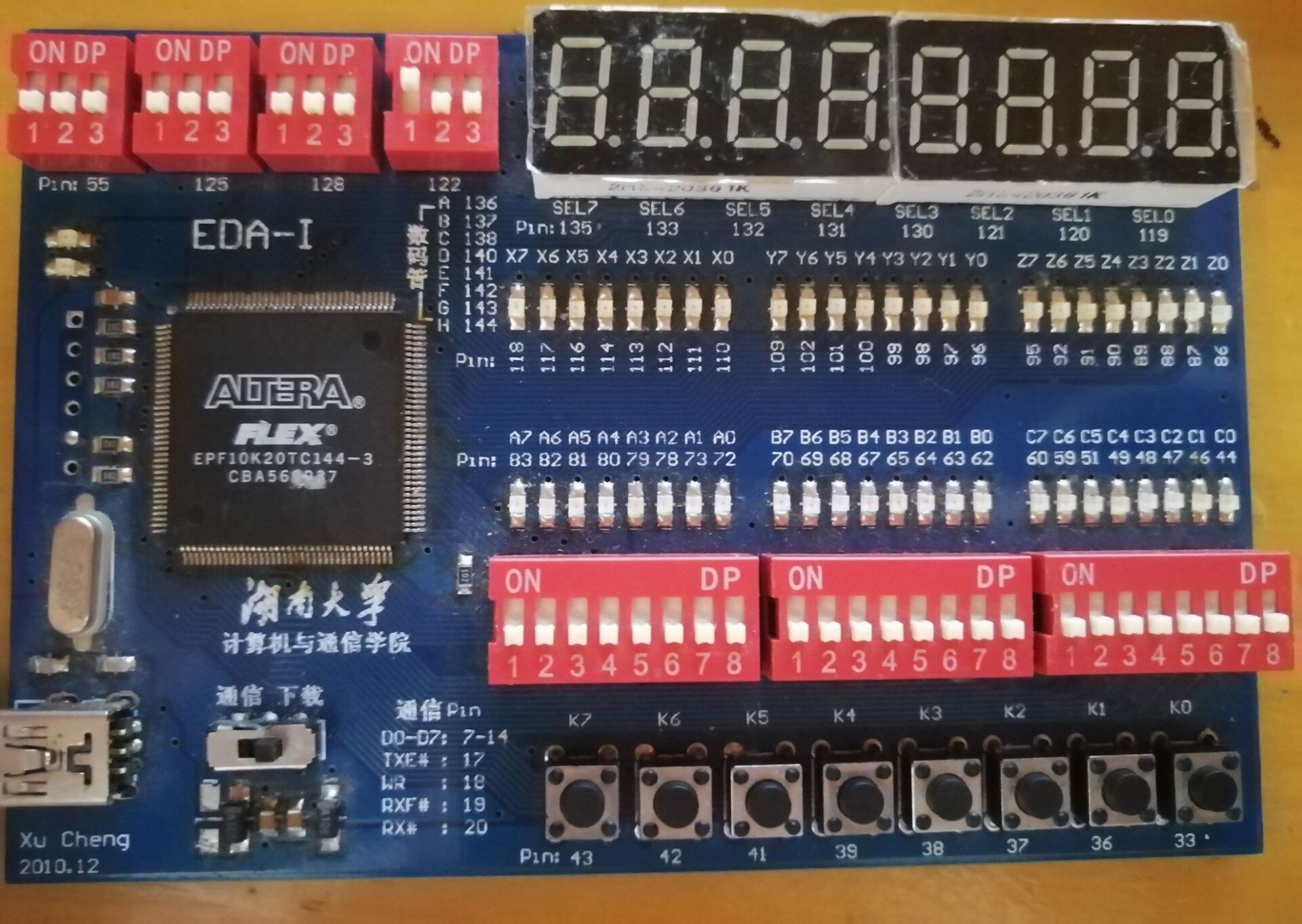

由于学校发的FPGA实验板型号为FLEX10K系列,没有报警器,所以以下报警器报警输出用灯光代替。

以下是VHDL代码

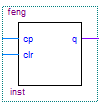

模块feng,在任一选手按下按键后,输出高电平给锁存器,锁存当时的按键状态。由于没有时钟同步,所以锁存的时间延时时间只是硬件延时时间,从而出现锁存错误的概率接近零。

library ieee;

use ieee.std_logic_1164.all;

entity feng is

port(cp,clr:in std_logic;

q:out std_logic);

end feng;

architecture feng_arc of feng is

begin

process(cp,clr)

begin

if clr='0' then

q<='0';

elsif cp'event and cp='0' then

q<='1';

end if;

end process;

end feng_arc;

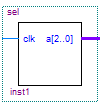

模块sel,产生数码管片选信号

library ieee;

use ieee.std_logic_1164.all;

entity sel is

port(clk:in std_logic;

a:out integer range 0 to 7);

end sel;

architecture sel_arc of sel is

begin

process(clk)

variable aa:integer range 0 to 7;

begin

if clk'event and clk='1' then

aa:=aa+1;

end if;

a<=aa;

end process;

end sel_arc;

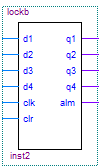

模块lockb,锁存器模块,在任一选手按下按键锁存后锁存,锁存的同时送出alm信号,实现声音提示(灯光提示)

library ieee;

use ieee.std_logic_1164.all;

entity lockb is

port(d1,d2,d3,d4:in std_logic;

clk,clr:in std_logic;

q1,q2,q3,q4,alm:out std_logic);

end lockb;

architecture lock_arc of lockb is

begin

process(clk)

begin

if clr='0' then

q1<='0';

q2<='0';

q3<='0';

q4<='0';

alm<='0';

elsif clk'event and clk='1' then

q1<=d1;

q2<=d2;

q3<=d3;

q4<=d4;

alm<='1';

end if;

end process;

end lock_arc;

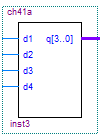

模块ch41a,将抢答的结果转换为二进制数

library ieee;

use ieee.std_logic_1164.all;

entity ch41a is

port(d1,d2,d3,d4:in std_logic;

q:out std_logic_vector(3 downto 0));

end ch41a;

architecture ch41_arc of ch41a is

begin

process(d1,d2,d3,d4)

variable tmp:std_logic_vector(3 downto 0);

begin

tmp:=d1&d2&d3&d4;

case tmp is

when "0111"=>q<="0001";

when "1011"=>q<="0010";

when "1101"=>q<="0011";

when "1110"=>q<="0100";

when others=>q<="1111";

end case;

end process;

end ch41_arc;

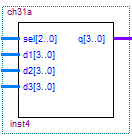

模块ch31a,对应数码管片选信号,送出需要显示的信号

library ieee;

use ieee.std_logic_1164.all;

entity ch31a is

port(sel:in std_logic_vector(2 downto 0);

d1,d2,d3:in std_logic_vector(3 downto 0);

q:out std_logic_vector(3 downto 0));

end ch31a;

architecture ch31_arc of ch31a is

begin

process(sel,d1,d2,d3)

begin

case sel is

when "110"=>q<=d1;

when "101"=>q<=d2;

when "011"=>q<=d3;

when others=>q<="1111";

end case;

end process;

end ch31_arc;

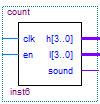

模块count,实现答题时间的倒计时,在计满60秒后送出声音提示(灯光提示)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count is

port(clk,en:in std_logic;

h,l:out std_logic_vector(3 downto 0);

sound:out std_logic);

end count;

architecture count_arc of count is

begin

process(clk,en)

variable hh,ll:std_logic_vector(3 downto 0);

begin

if clk'event and clk='1' then

if en='1' then

if ll=0 and hh=0 then

sound<='1';

elsif ll=0 then

ll:="1001";

hh:=hh-1;

else

ll:=ll-1;

end if;

else

sound<='0';

hh:="0101";

ll:="1001";

end if;

end if;

h<=hh;

l<=ll;

end process;

end count_arc;

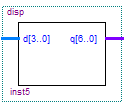

模块disp,它是七段译码器

library ieee;

use ieee.std_logic_1164.all;

entity disp is

port(d:in std_logic_vector(3 downto 0);

q:out std_logic_vector(6 downto 0));

end disp;

architecture disp_arc of disp is

begin

process(d)

begin

case d is

when"0000"=>q<="0111111";

when"0001"=>q<="0000110";

when"0010"=>q<="1011011";

when"0011"=>q<="1001111";

when"0100"=>q<="1100110";

when"0101"=>q<="1101101";

when"0110"=>q<="1111101";

when"0111"=>q<="0100111";

when"1000"=>q<="1111111";

when"1001"=>q<="1101111";

when others=>q<="0000000";

end case;

end process;

end disp_arc;

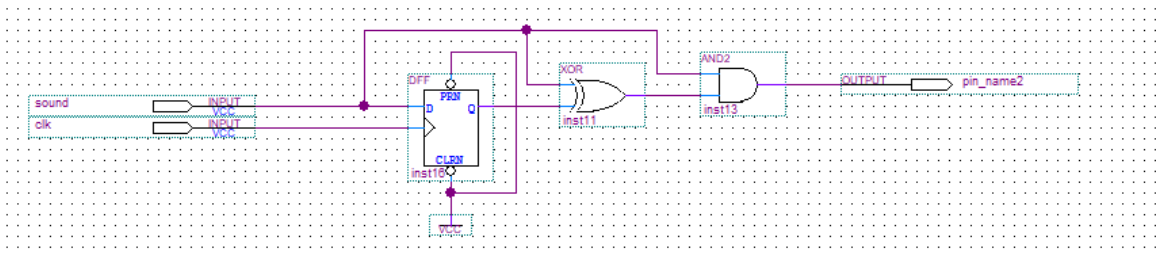

下图部分只是在sound的上升沿时送出一个时钟周期的高电平,接蜂鸣器可做声音提示

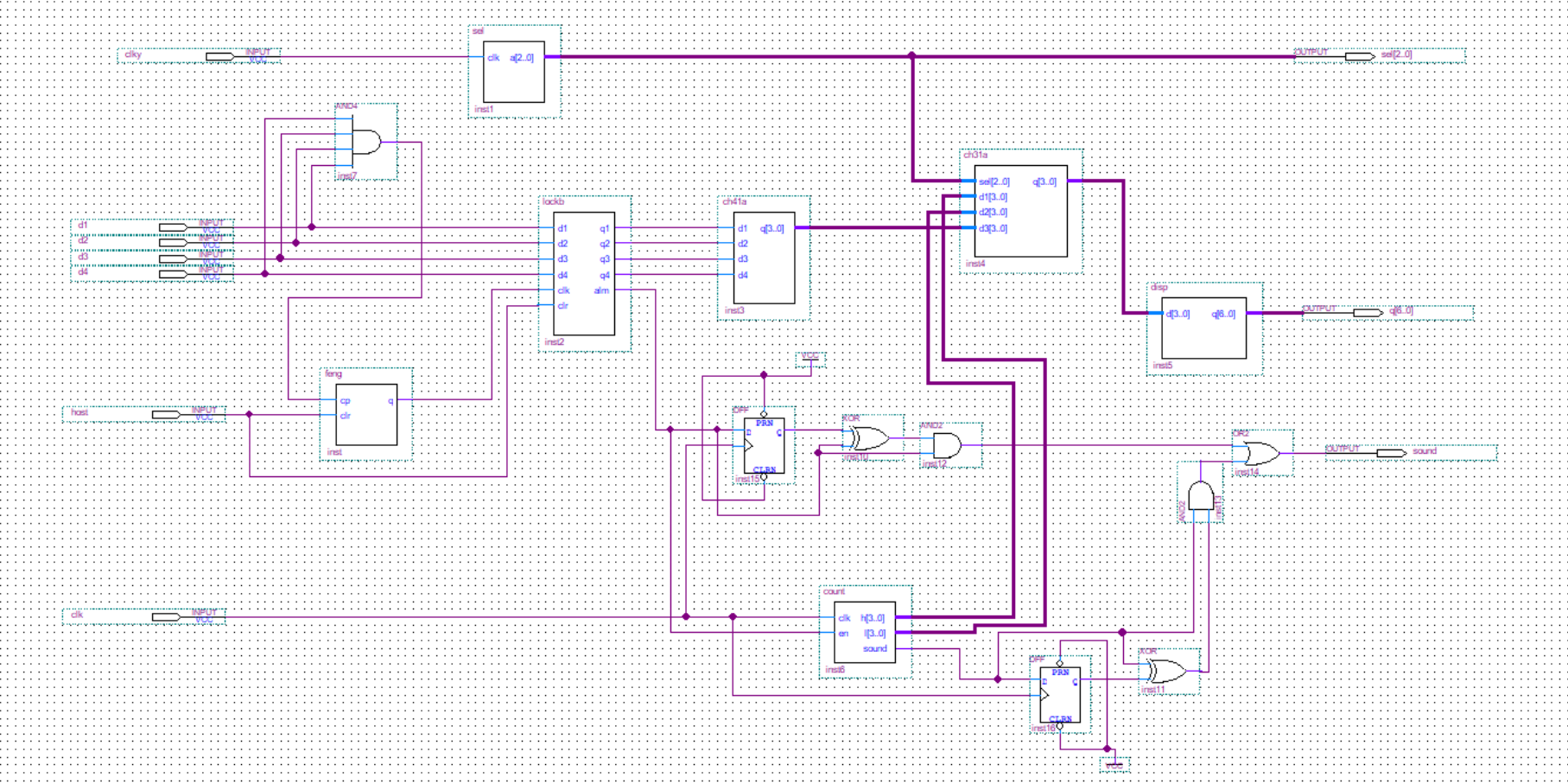

总体框图如下

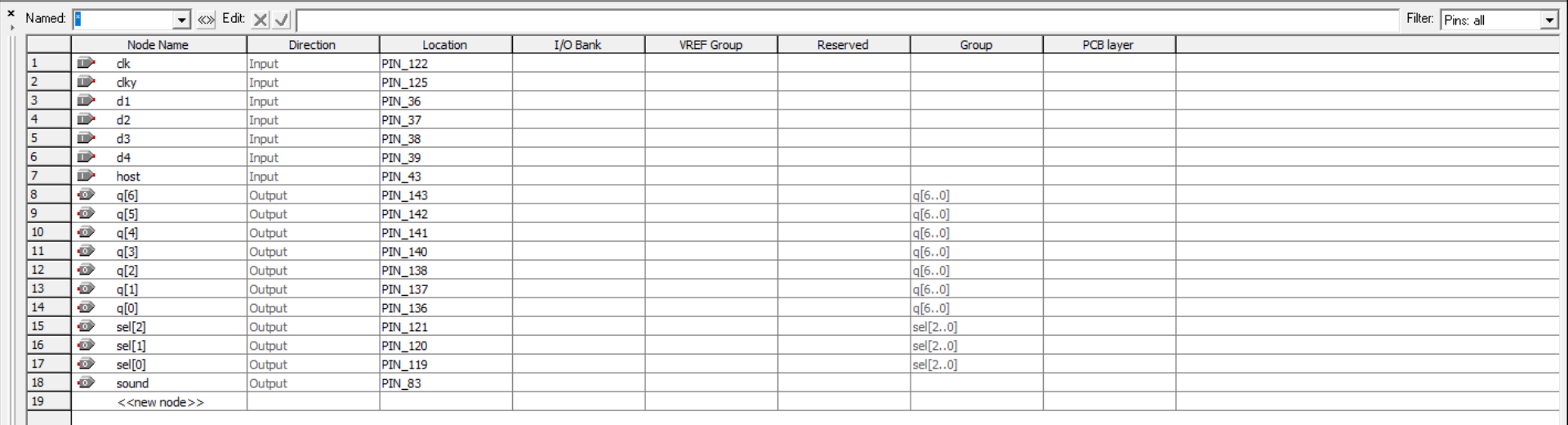

引脚分配如下:

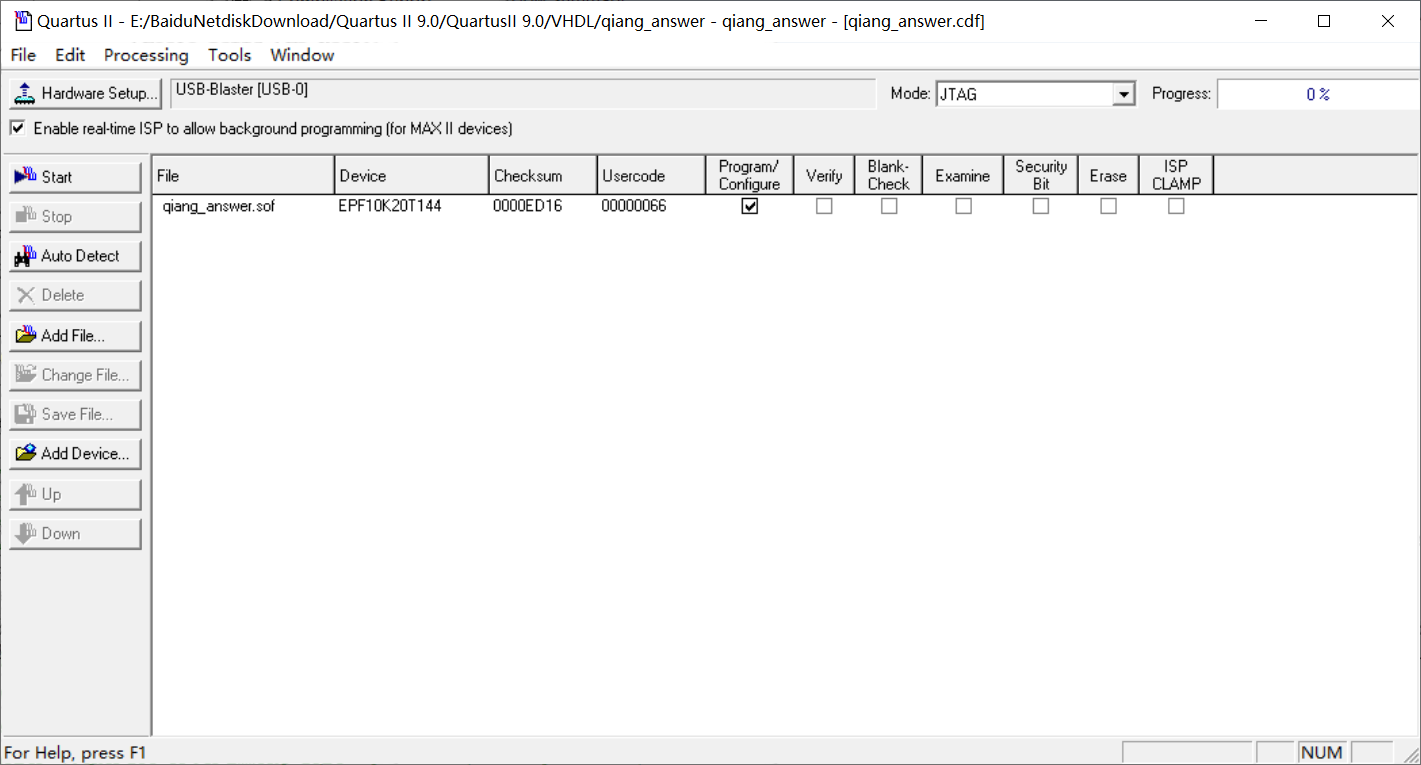

引脚分配好后烧录程序

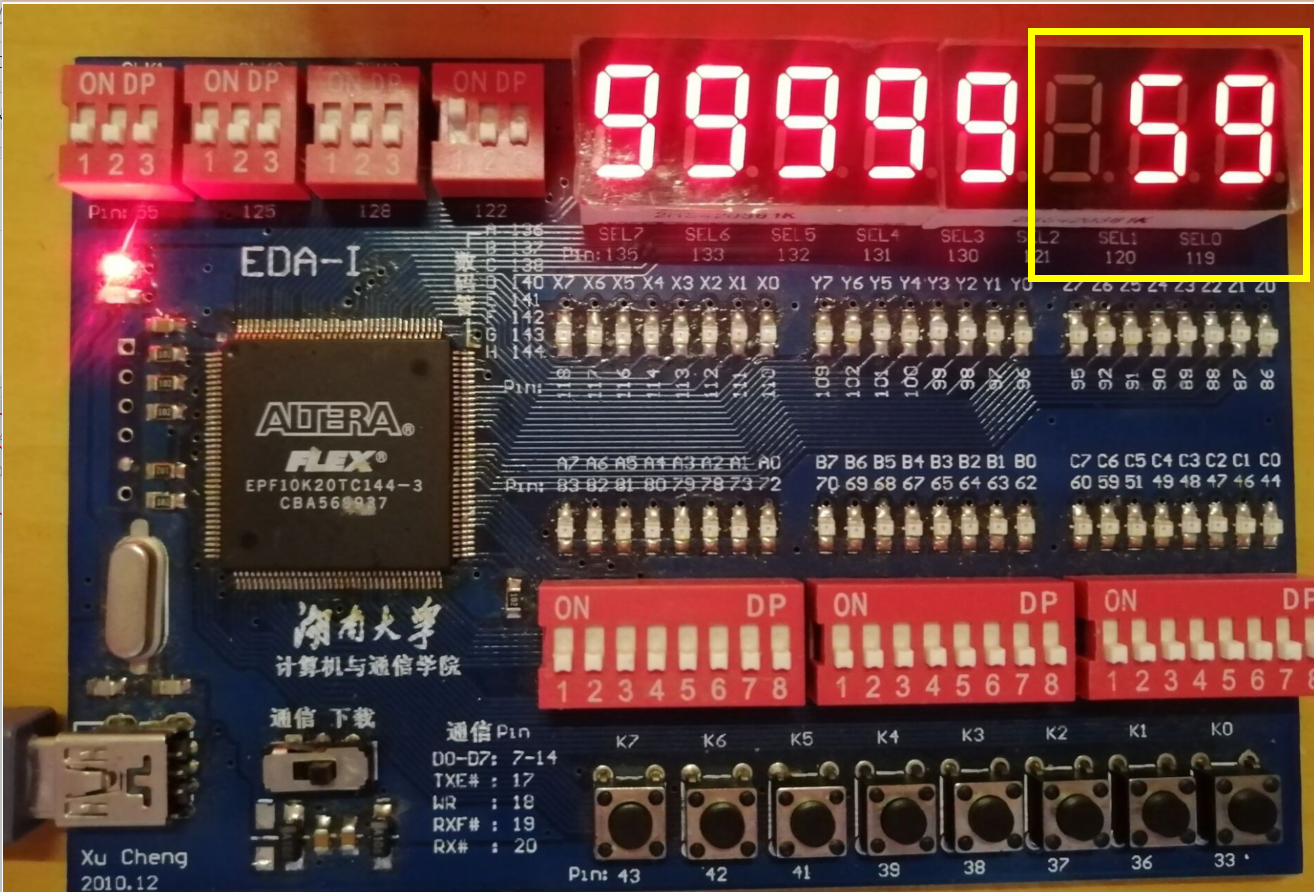

数码管片选信号我分配在最后三个数码管,这是初始时倒计时为59秒,任一选手抢答,第一个(黄框内第一个)数码管会显示抢答者的号码,同时pin83号的灯亮了,待倒计时结束,pin83号灯亮表示时间到。

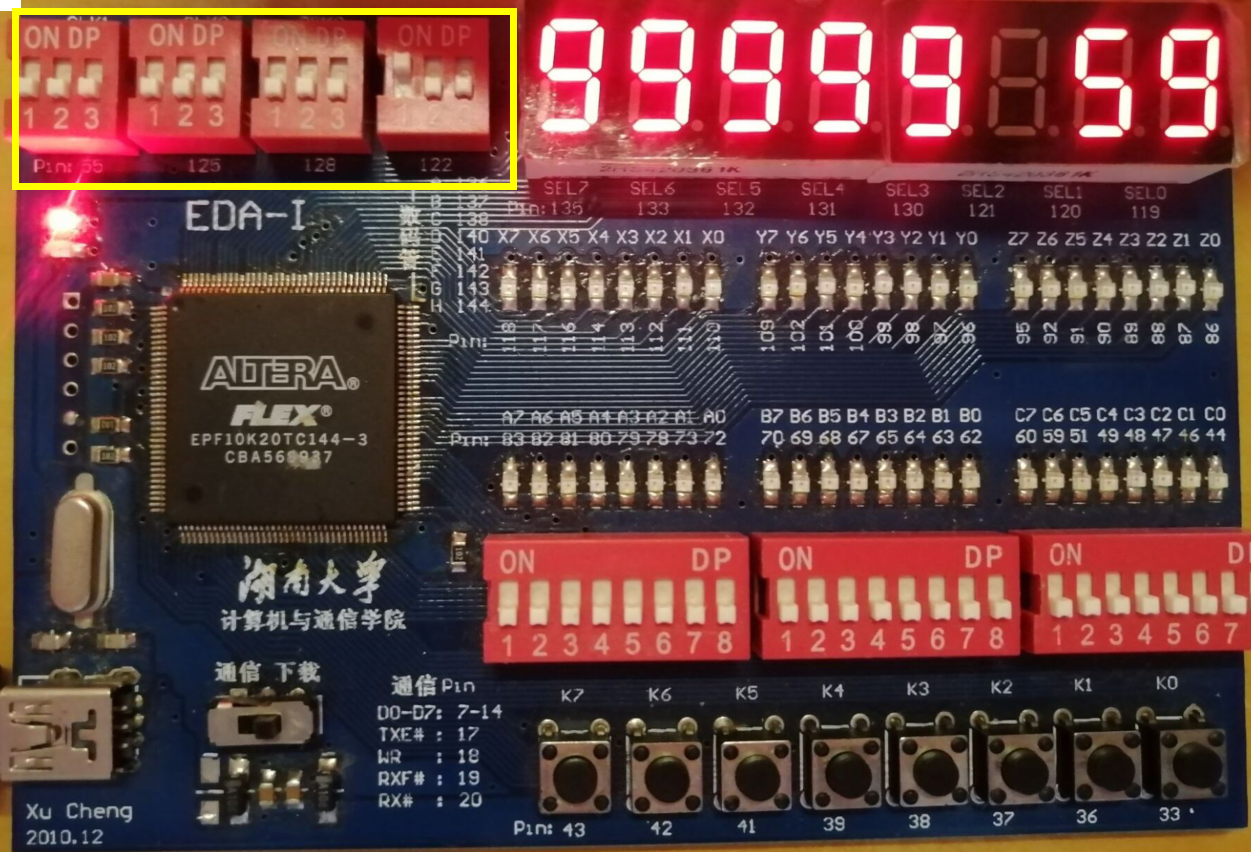

框内是时钟信号接入口,FPGA板背面会介绍不同的频率,调节频率可以改变倒计时的速度。

最后

以上就是瘦瘦小猫咪最近收集整理的关于竞赛抢答器设计的全部内容,更多相关竞赛抢答器设计内容请搜索靠谱客的其他文章。

发表评论 取消回复