2 组合逻辑设计

组合电路和时序电路的区别是在于输出是否与之前的状态有关。本章还介绍了布尔表达式,布尔代数等知识点,推气泡法是比较好的能根据电路原理图快速写出逻辑电路的表达式的方法。

然后是卡诺图化简方法。数据选择器、译码电路等。

时序概念与毛刺

3 时序逻辑设计

3.1 锁存器与触发器

交叉耦合反相器,就是数电学过的最基本的双稳态电路,是不存在实际应用意义的,因为初始状态没控制输入。

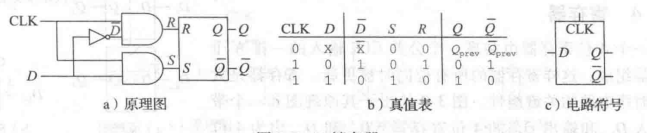

对于SR锁存器,R表示reset,置零,S表示set,置1,当R=S=0时,是锁存状态,Q和^Q将保持以前的状态。当R=S=1时,此时由于或非门输出一定为0,Q和^Q都是0,因此不能确定Q的值,所以这种情况是无意义的。

D锁存器,有两个输入,数据输入D和时钟输入CLK。当CLK(图中WE)=0时,S=R=0,输出端保持不变。当CLK=1时,Q=D。

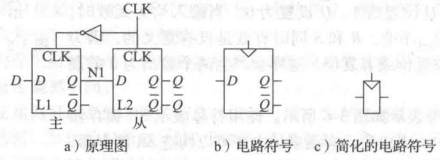

D触发器可以由两个锁存器构成。

当CLK=0时,主锁存器将数据传送到从锁存器的D端,当CLK变成1时,从锁存器将D传到Q端。而主锁存器被切断,不能传输源端数据。D触发器只能在时钟上升沿才能将D传输到输出Q。

N位寄存器由一排N位触发器构成。

带使能端触发器,在D触发器前面加上选择器;带复位,则将复位信号与上数据D后输入到D触发器的D端。此为同步复位。异步复位需要调整触发器内部结构。

3.2 同步逻辑设计 有限状态机

书上介绍的方法与以前在数电课程上学的略有区别,更好理解。这里就简单总结一下流程。

对实际问题进行状态机设计:(1)确定输入、输出;(2)画状态转换图,确定状态、状态转换表,输出表;(3)选择状态编码(4)写出下一个状态的逻辑表达式,写出输出的逻辑表达式;(5)画出电路图。

电路图确定状态图:(1)确定输入、输出,状态的编码位,写出输出表达式,状态编码的表达式;(2)合并简化,得到状态编码转换表;(3)给编码命名状态,画出状态图

3.3 时序逻辑中的时序

建立时间、保持时间的概念:时钟上升沿到来前,输入必须在建立时间内保持稳定,在时钟上升沿到来之后,输入必须至少在保持时间内保持稳定。

动态约束主要是指同步时序电路的输入满足这两个要求。

建立时间约束:t(setup) <= Tc- (tpd+tpcq)

保持时间约束:t(hold) <= tpd+tpcq.

建立时间不满足,可以考虑增加时钟周期或者优化组合逻辑,缩短组合逻辑的延迟时间。

保持时间不满足,可以考虑增加组合逻辑的延迟时间。

在考虑时钟偏移时,均考虑最坏情况,对于建立时间,最坏情况是CLK1更晚,CLK2更早,那么就有t(setup) <= Tc- (tpd+tpcq)-t(skew);对于保持时间,最坏情况是CLK2更晚,CLK1更早,那么就有t(hold) <= tpd+tpcq-t(skew)。当时钟偏移时间存在时,有时候为了防止严重的保持时间错误,将触发器故意设计很慢,增加tpcq。

3.4 亚稳态与同步器、并行

书上详细说明了亚稳态出现的情况,输入变化出现在窗口时间内,会出现亚稳态,但是当时间足够长,是能够回到稳态的。所以两级同步的好处就是在一个时钟周期内,亚稳态基本都能消失回到稳态了。

关于分辨时间的推导暂时没有看。

延迟是任务从开始到结束的时间,吞吐量是系统单位时间内能完成的任务量。

使用流水线能在时间上并行处理任务,通过插入寄存器,缩短时钟周期的要求,从而提高系统频率。

最后

以上就是辛勤电灯胆最近收集整理的关于学习笔记 《数字设计与计算机体系结构》2 组合逻辑设计3 时序逻辑设计的全部内容,更多相关学习笔记内容请搜索靠谱客的其他文章。

发表评论 取消回复