一个电路能跑到多少M的时钟呢?

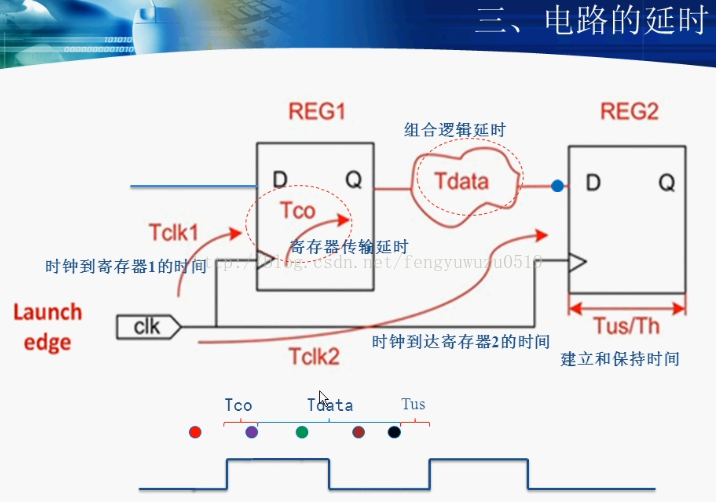

这和电路的设计有密切联系(组合逻辑的延时),我们知道电路器件都是由一定延迟的,所以信号的仿真很重要。如果延迟时间大于时钟,就会导致时序违例,出现逻辑错误。

项目要求300M怎么实现呢?

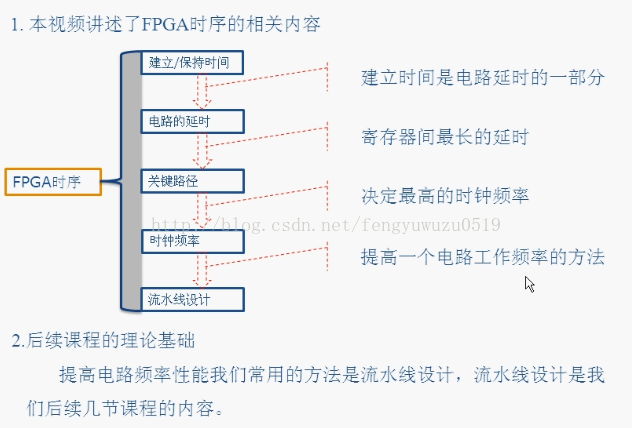

学习涉及如下:

- 建立时间保持时间;

- 电路延时

- 时钟频率

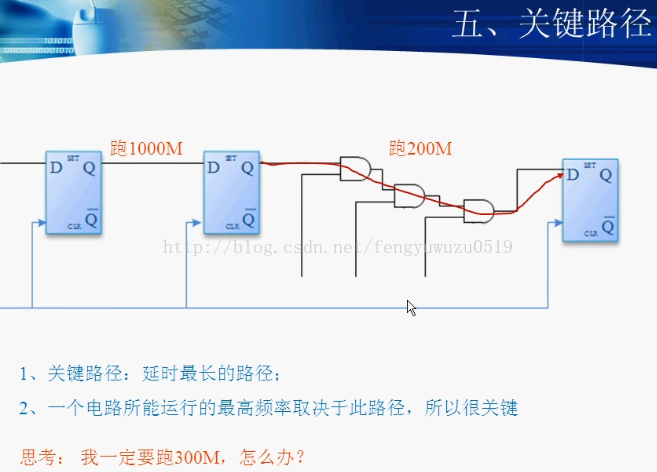

- 关键路径

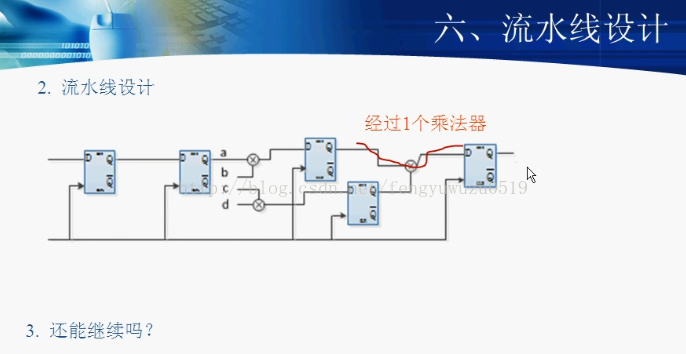

- 流水线设计来提高CLK

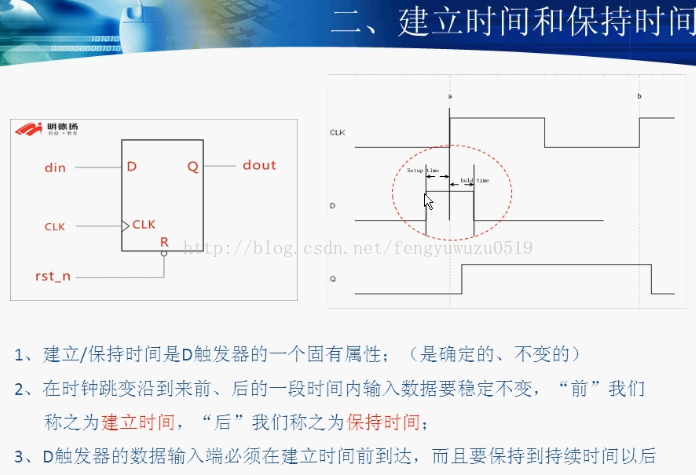

首先来看下D触发器

一、D触发器时序分析

上升沿前后对D有一定要求,称为上升时间和保持时间

电路都是存在延时的:

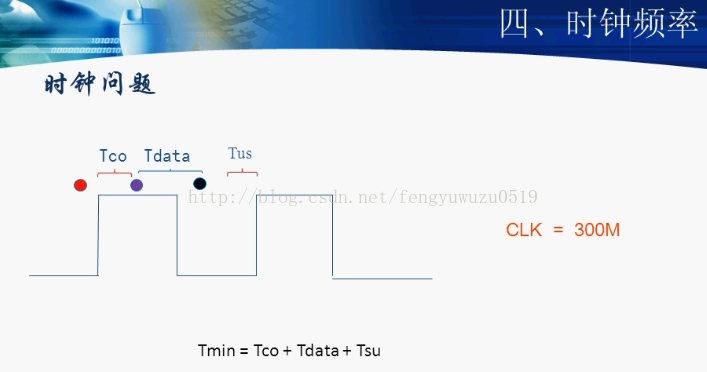

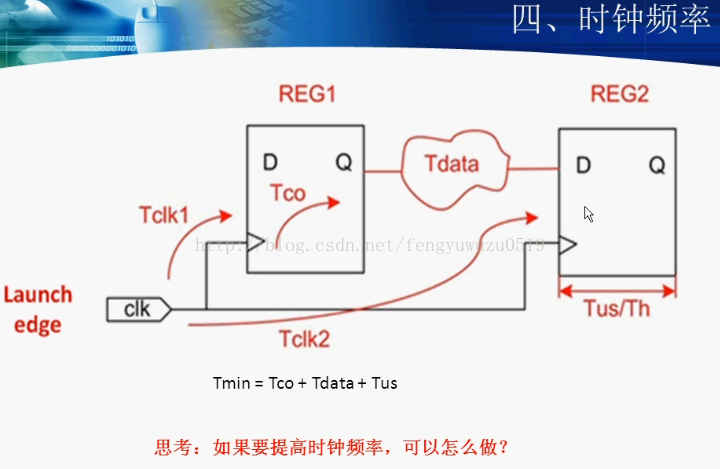

时钟频率最高可达多少:

由系统的延时时间情况决定。

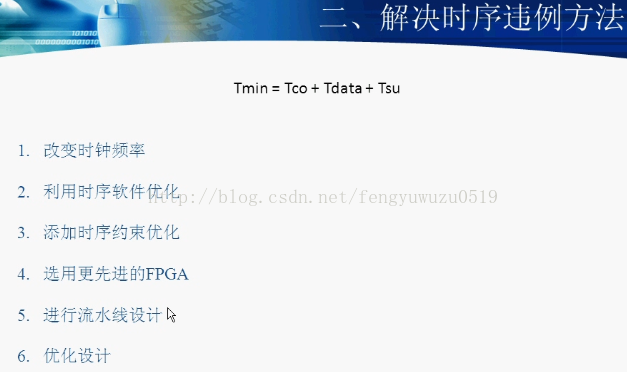

降低关键路径的延时时间,如组合逻辑的时间来提高系统可运行的频率。

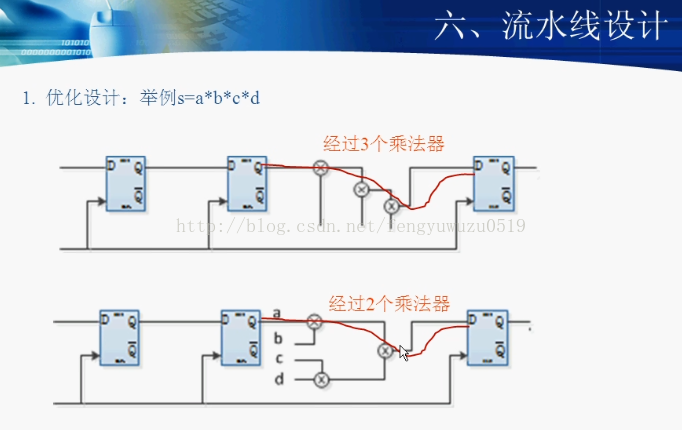

优化设计方案:

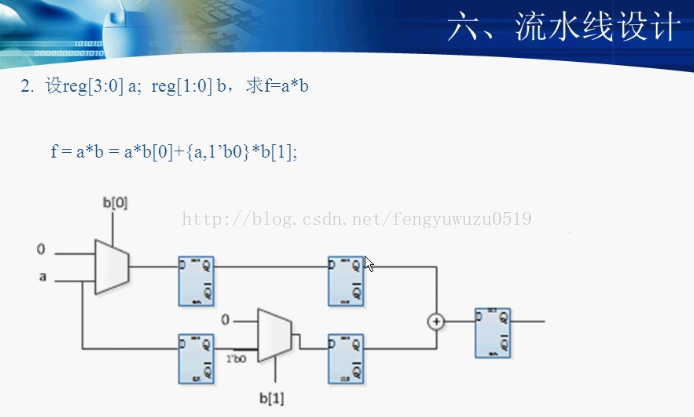

乘法器变成:选择器+加法器

+

+

由此我们可以看出,电路的设计决定了延时时间的大小。一般而言乘法器会占用比加法器更多的延迟时间。所以设计中尽量降低乘法器的个数,来降低组合逻辑造成的延时。

接下来,我们来学习一下,如何通过软件仿真来检查系统是否满足时序要求,及系统的当前频率是否可以正常实现功能。

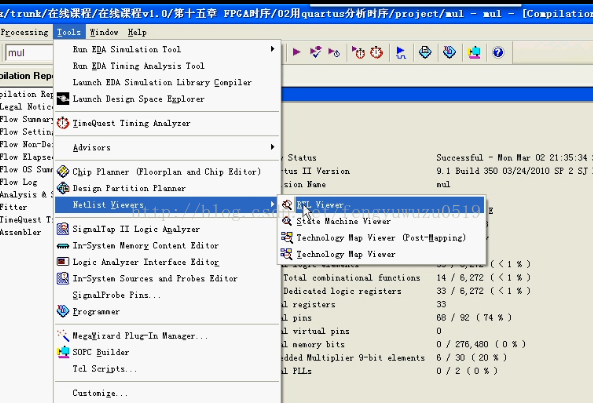

二、仿真操作

(1) 编译

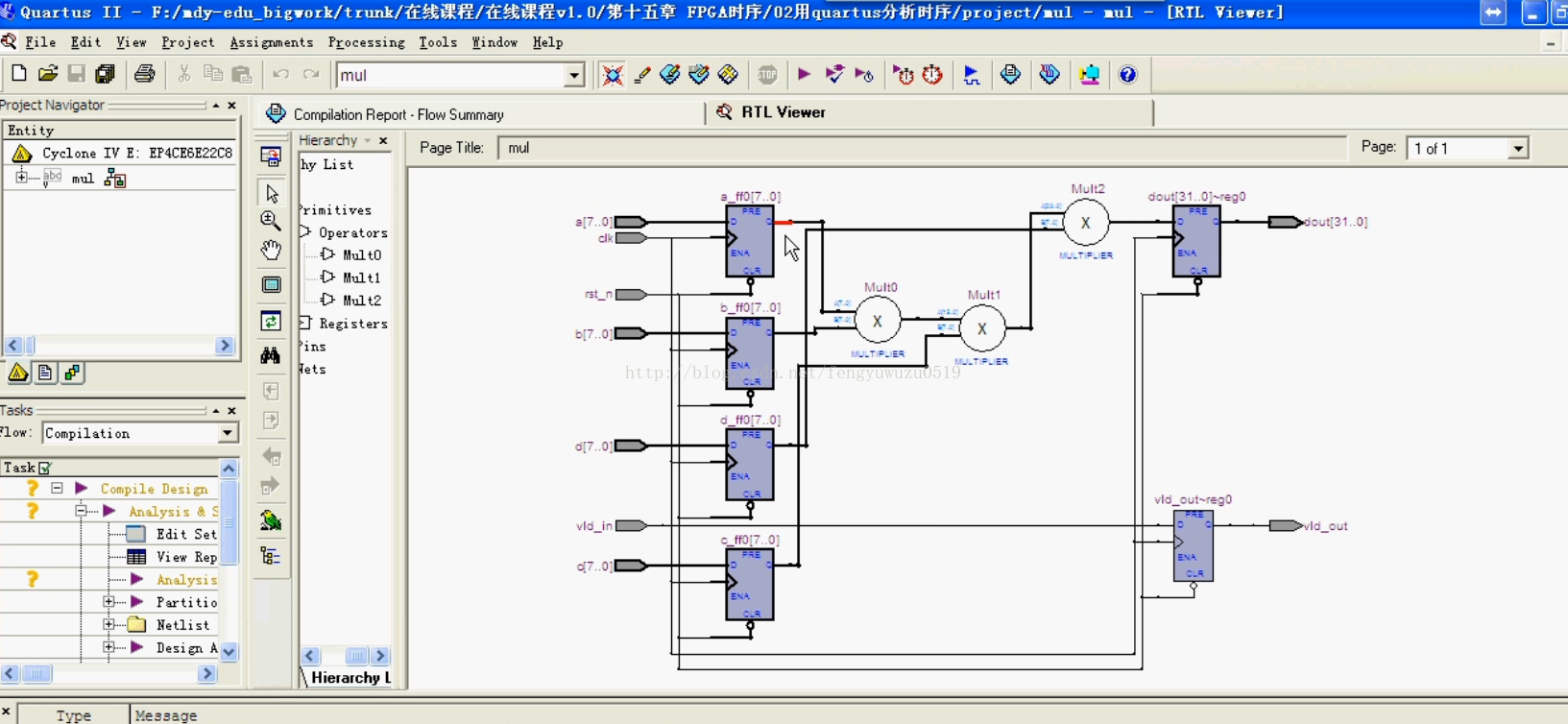

(2) 查看RTL电路

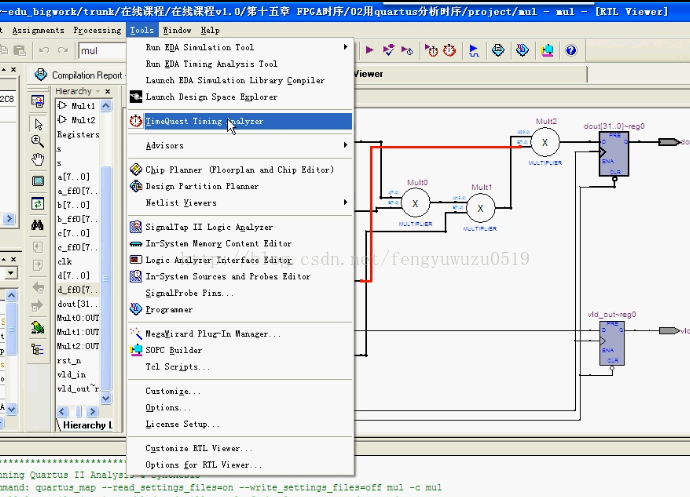

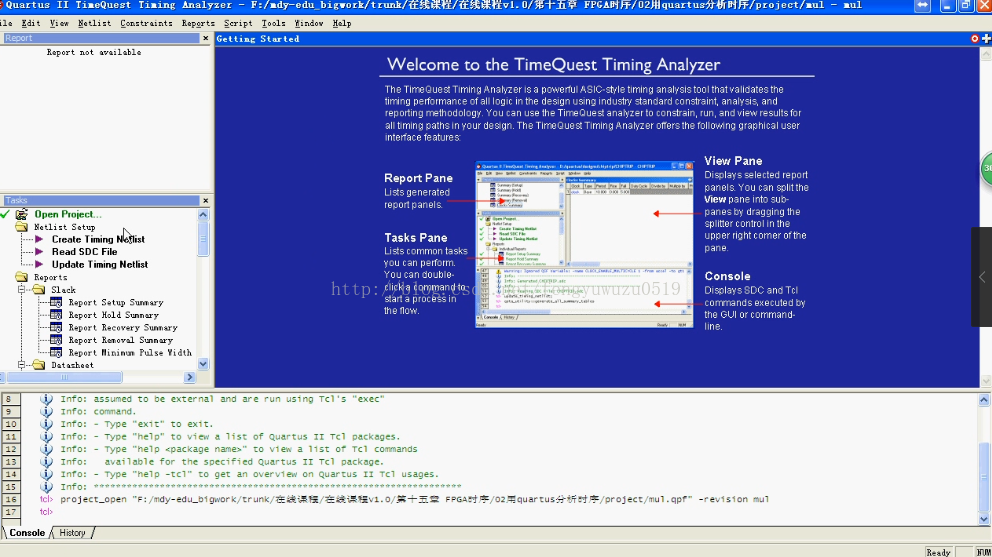

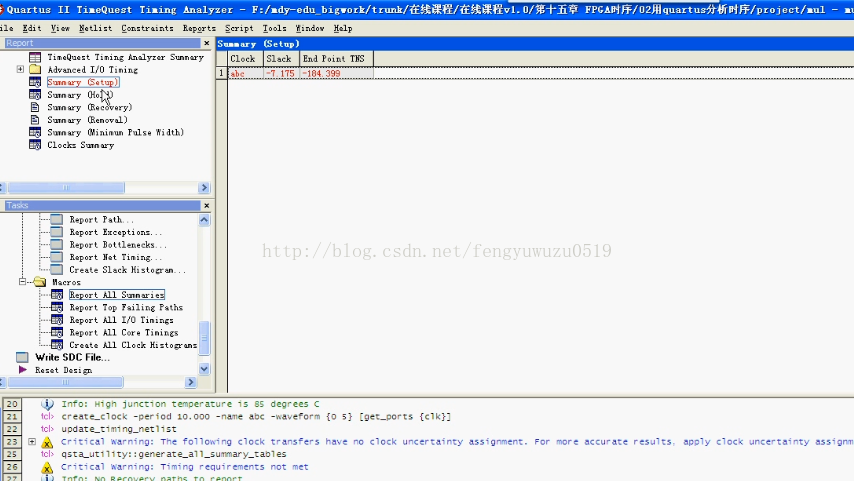

(3)编译--时序分析器

产生时序网表

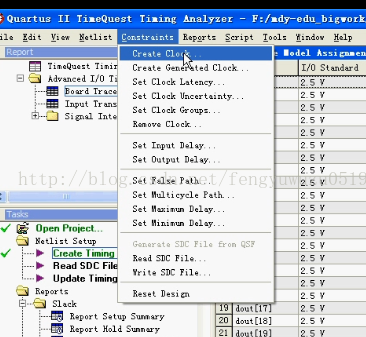

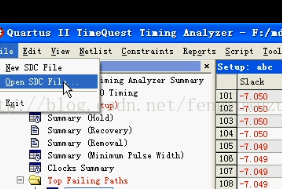

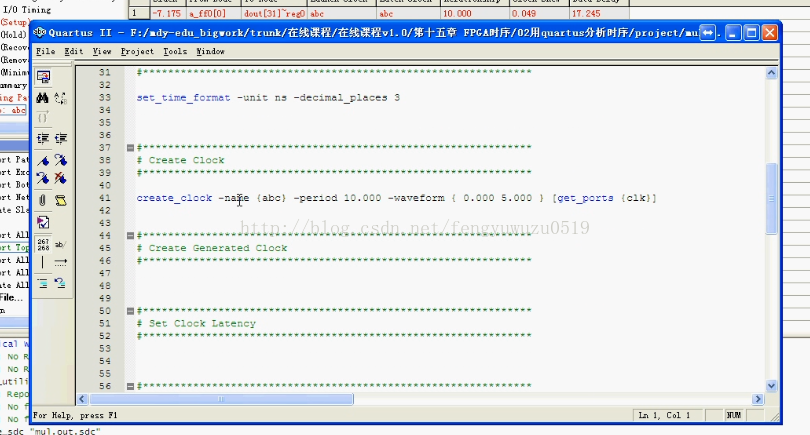

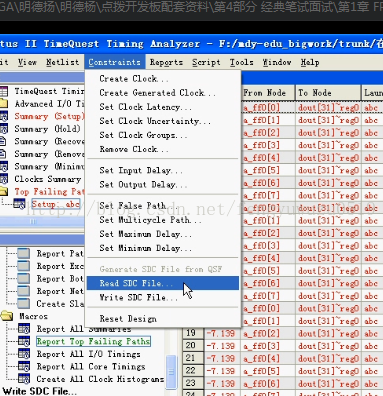

(1) 添加约束,告诉软件时钟是多少等

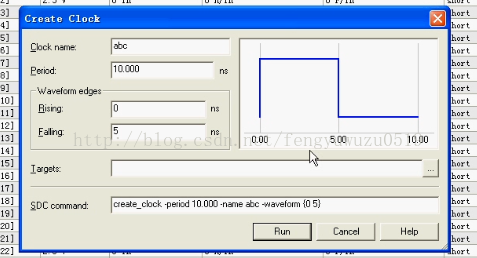

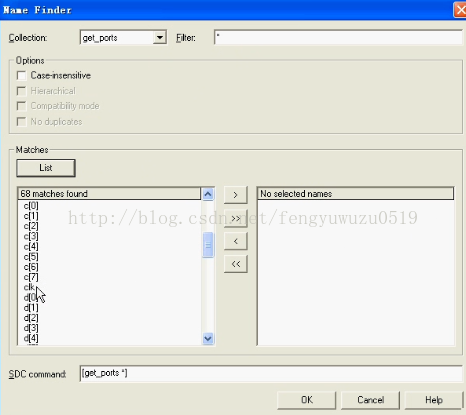

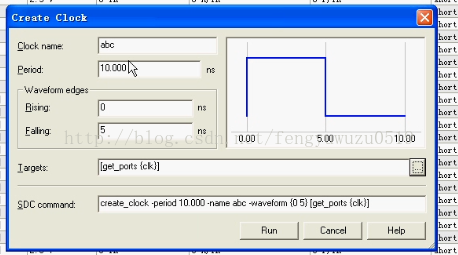

(2) 先产生时钟

点击run

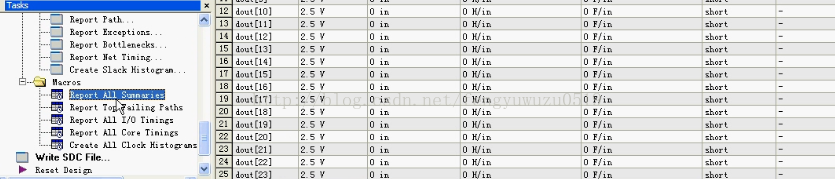

双击报告

建立时间不满足

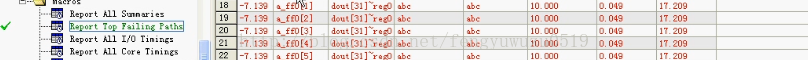

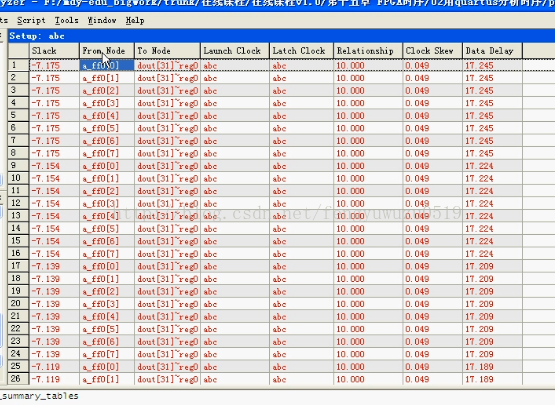

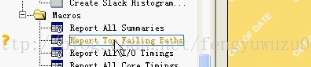

想知道哪里不满足 哪个路径延时比较大,点击下面,

列出了所有不满足的路径

正常大于等于0

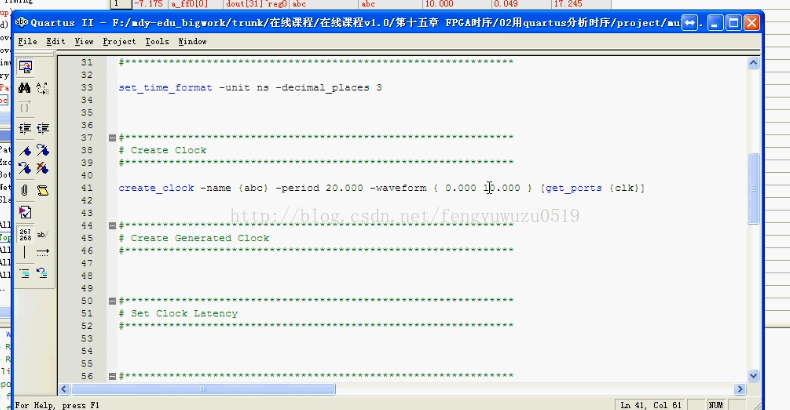

修改时序约束:

通过以上学习,我们认识到了,系统的时钟频率不是可以随意设定的很高的,它有系统设计的结构造成的延时时间来决定(组合逻辑)。

我们可以通过降低乘法器的个数,采用流水线的设计方法来提高系统可达到的最高时钟。

并通过了软件仿真来验证当前频率是否能保证系统正常运行,满足时序要求。

转载自:http://blog.csdn.net/fengyuwuzu0519/article/details/72599432?locationNum=14&fps=1

转载于:https://www.cnblogs.com/chengqi521/p/7444891.html

最后

以上就是怡然口红最近收集整理的关于FPGA学习(第8节)-Verilog设计电路的时序要点及时序仿真一、D触发器时序分析二、仿真操作的全部内容,更多相关FPGA学习(第8节)-Verilog设计电路内容请搜索靠谱客的其他文章。

发表评论 取消回复