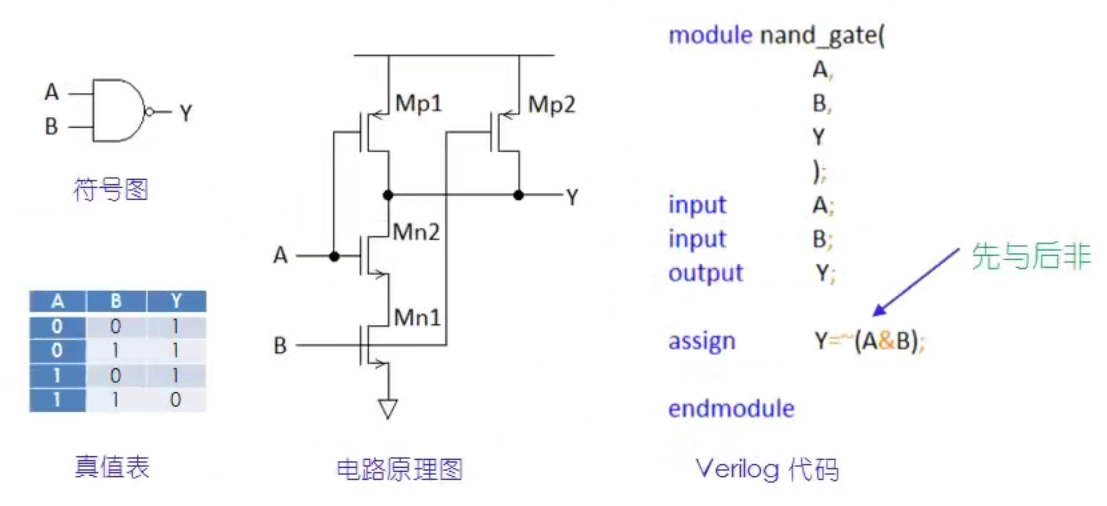

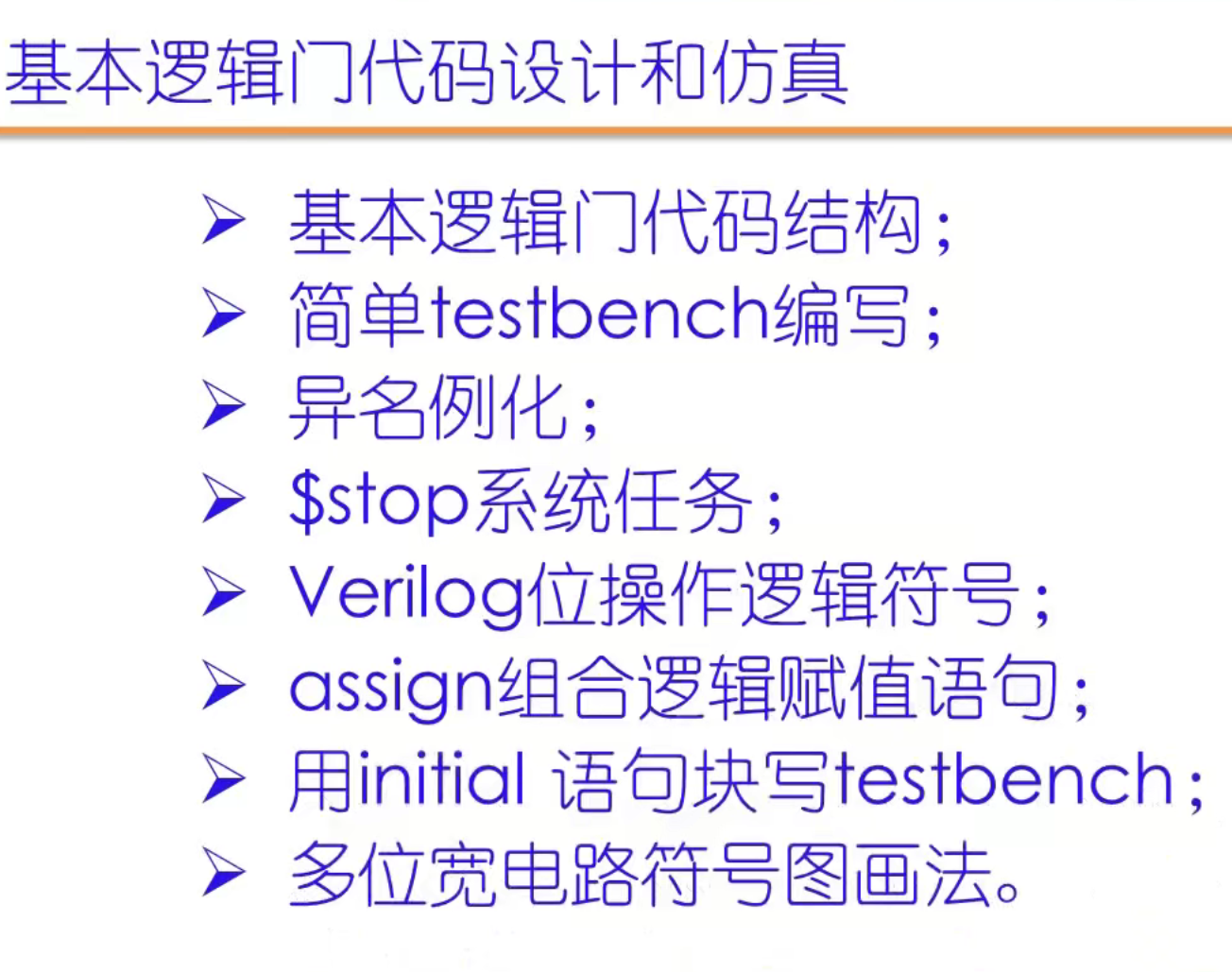

一位与非门 nand_gate.v:

// 2022-1-16 verilog学习

// 与非门 (与and,非n,与非门nand_gate)

`timescale 1ns/10ps

module nand_gate(

// 定义端口

A,

B,

Y

);

// 定义端口属性

input A;

input B;

output Y;

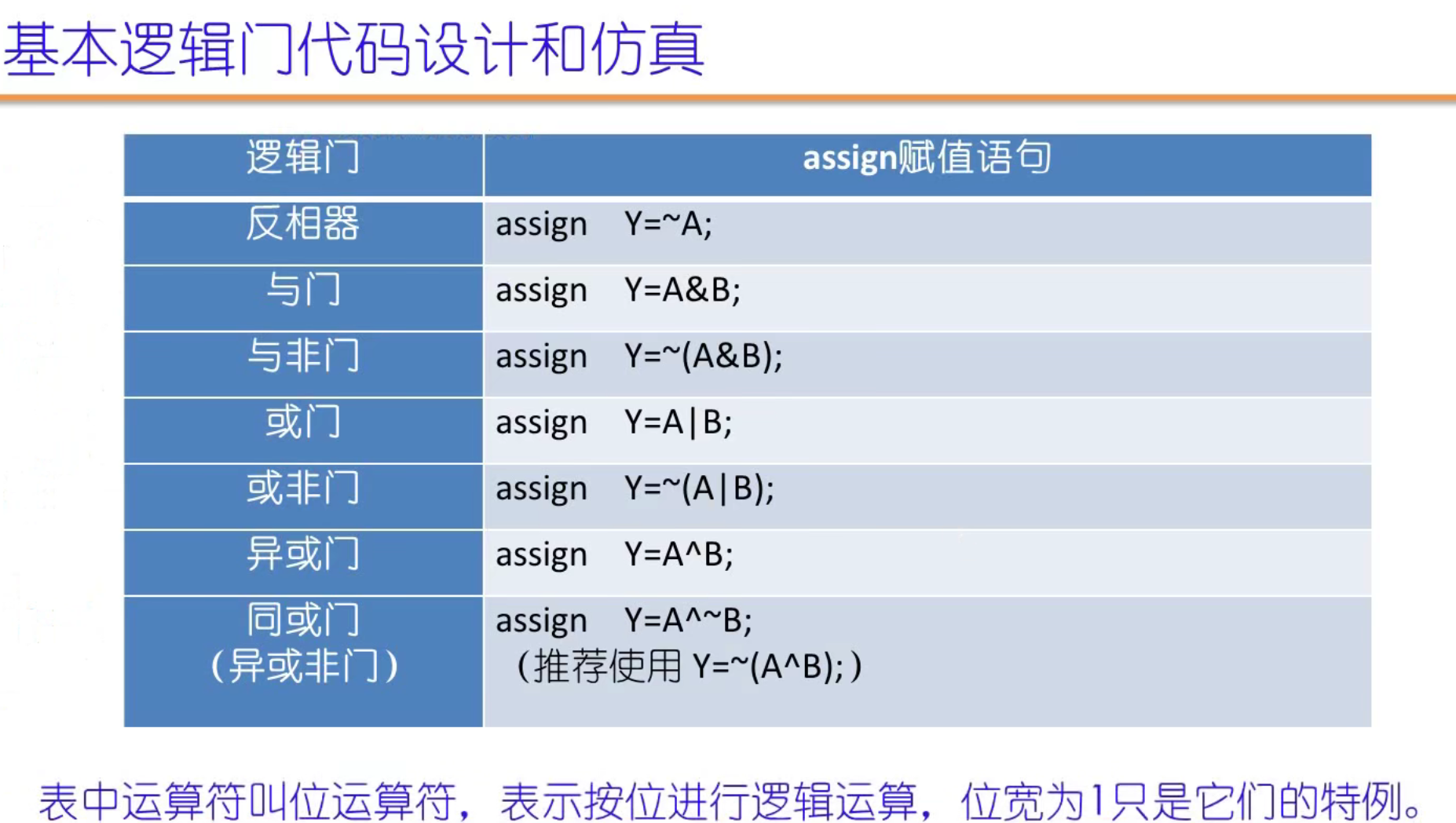

assign Y=~(A&B);

endmodule

// testbench 测试台

module nand_gate_tb;

reg aa,bb; // 输入reg型变量

wire yy; // 输出wire型变量

nand_gate nand_gate(

.A(aa),

.B(bb),

.Y(yy)

); // A()括号表示A端口接啥

initial begin

aa<=0;bb<=0;

#10 aa<=0;bb<=1;

#10 aa<=1;bb<=0;

#10 aa<=1;bb<=1;

#10 $stop; // 停止

end

endmodule

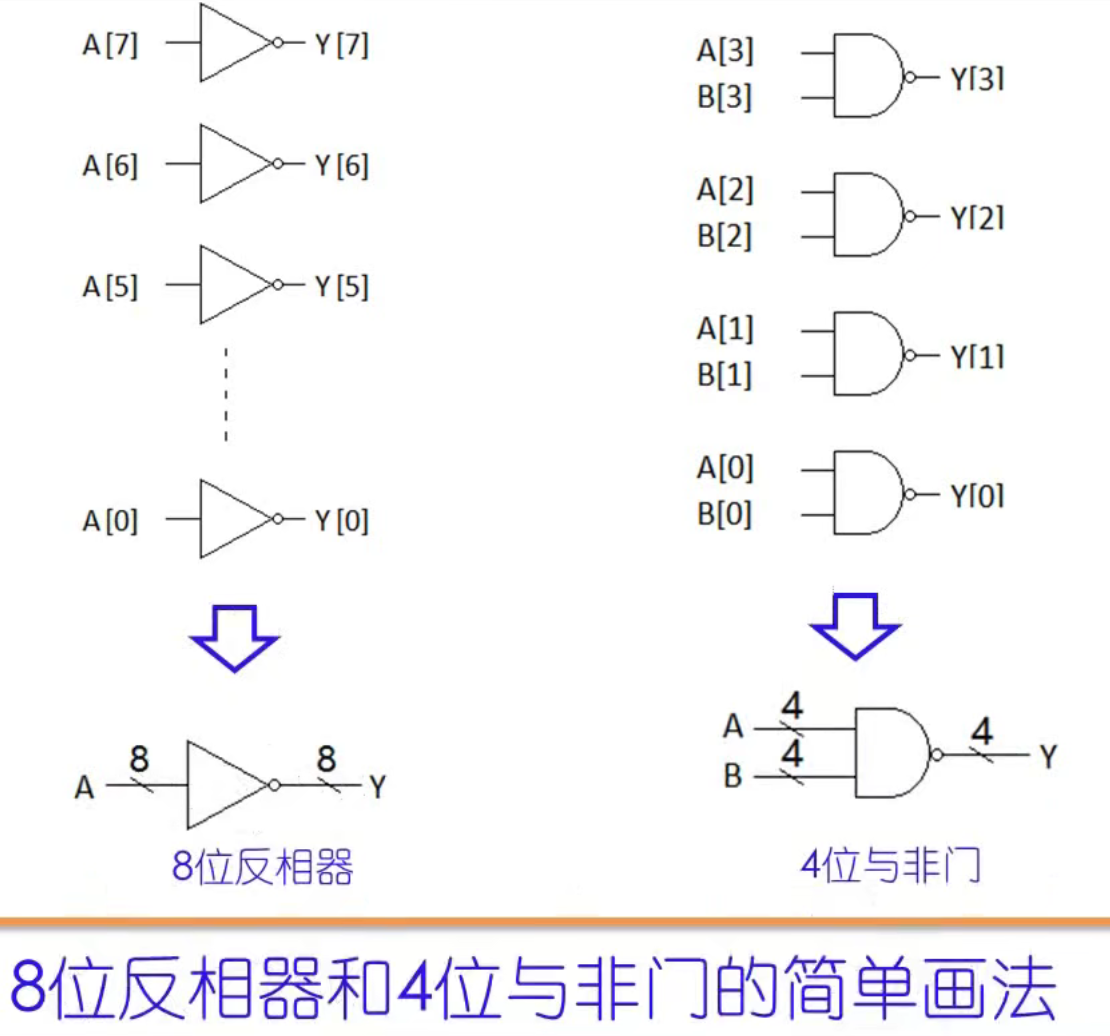

4位与非门 nand_gate_4bits.v:

// 2022-1-16 verilog学习

// 与非门 (与and,非n,与非门nand_gate)

`timescale 1ns/10ps

module nand_gate_4bits(

// 定义端口

A,

B,

Y

);

// 定义端口属性

input[3:0] A;

input[3:0] B;

output[3:0] Y;

assign Y=~(A&B);

endmodule

// testbench 测试台

module nand_gate_4bits_tb;

reg[3:0] aa,bb; // 输入reg型变量

wire[3:0] yy; // 输出wire型变量

nand_gate_4bits nand_gate_4bits(

.A(aa),

.B(bb),

.Y(yy)

); // A()括号表示A端口接啥

initial begin

// 4'b00 表示4位

aa<=4'b0000;bb<=4'b1111;

#10 aa<=4'b0010;bb<=4'b0110;

#10 aa<=4'b0111;bb<=4'b0100;

#10 aa<=4'b0000;bb<=4'b1110;

#10 $stop; // 停止

end

endmodule

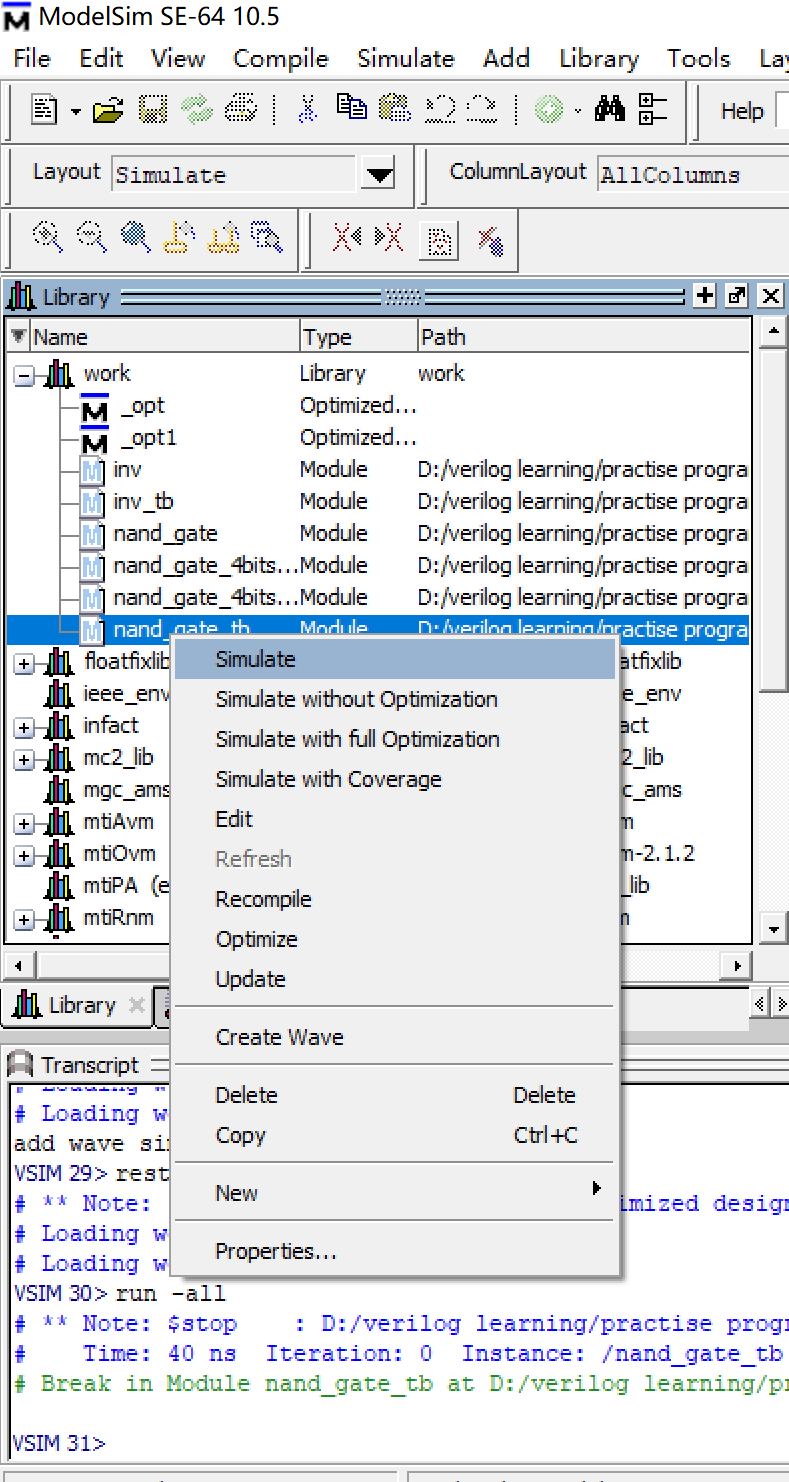

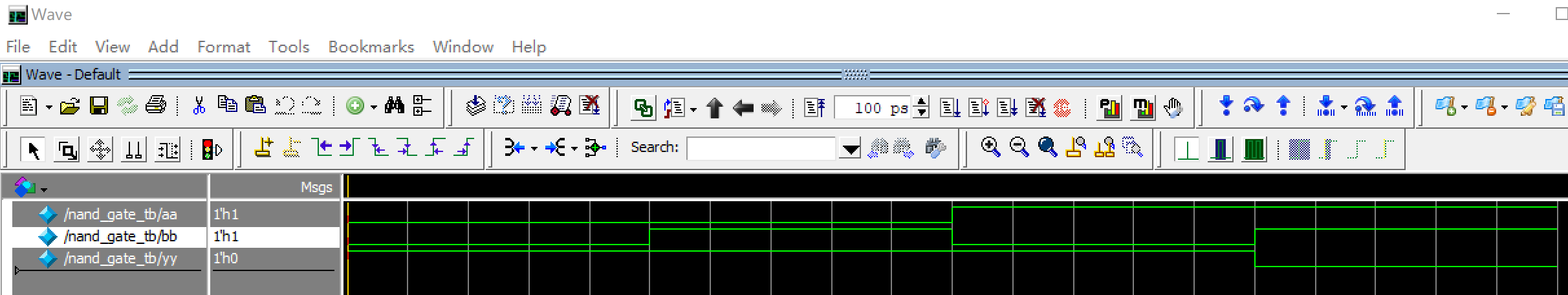

modelsim 仿真:

library 中找到测试台module,一般命名为 xxx_tb,右键simulate

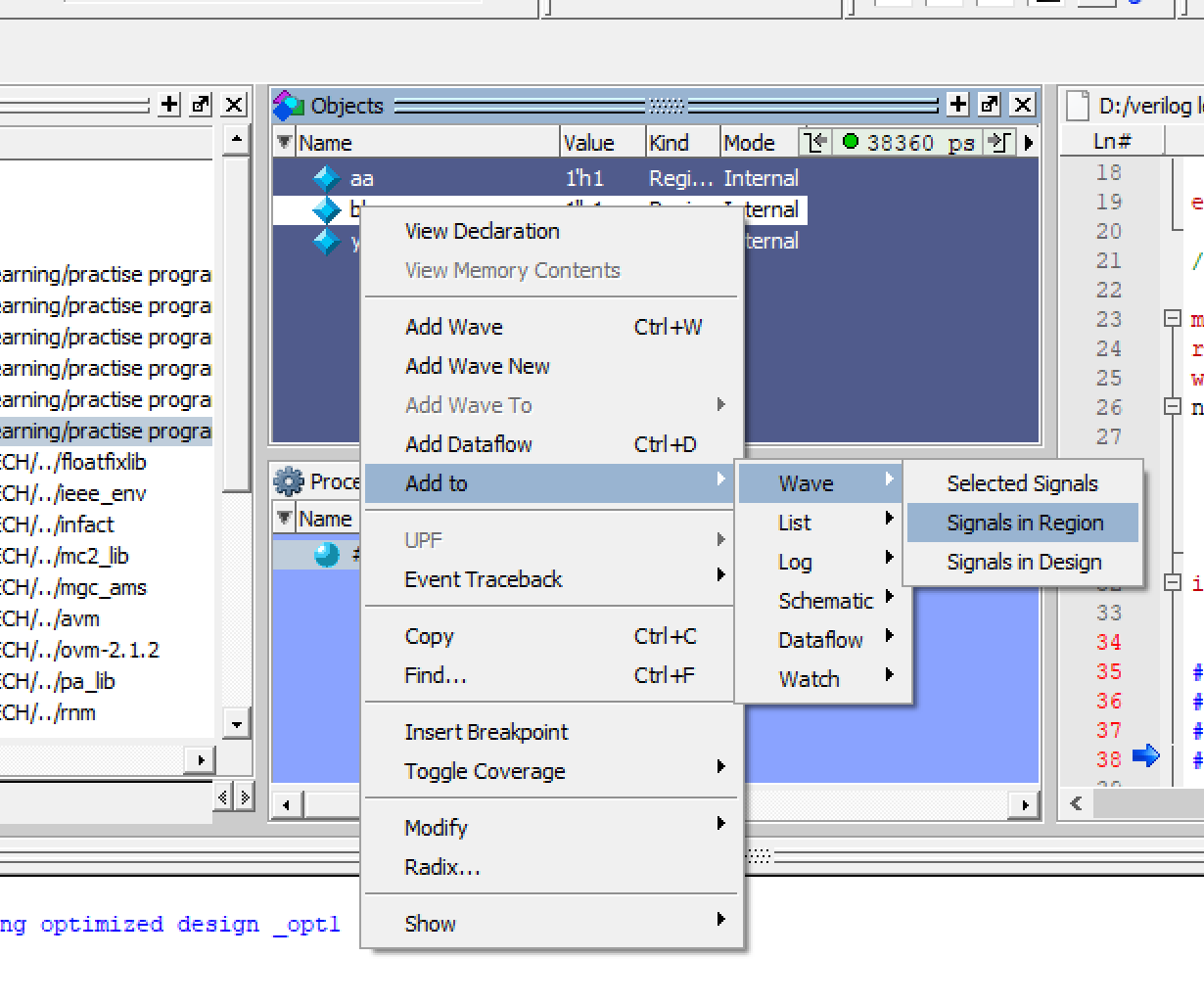

object 中找到输入变量 add to,wave,signal in region

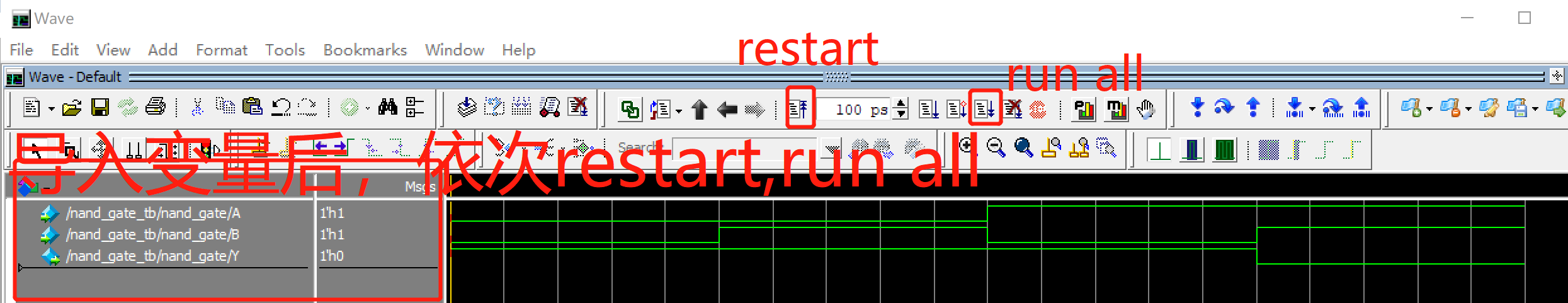

wave窗口中依次 restart,run all

与非门

4位与非门

最后

以上就是完美御姐最近收集整理的关于verilog 一位/多位与非门的设计与仿真modelsim 仿真:的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复