因为想申请 CSDN 博客认证需要一定的粉丝量,而我写了五年博客才 700 多粉丝,本文开启关注才可阅读全文,很抱歉影响您的阅读体验

- 为了准备电赛临时学一下TM4C123G,简单记录学习内容

- 大家可以在这里下载我收集的资源,非常全面,花了很大功夫收集来的,还有书籍、例程代码等

- 还可以在TI官网下载相关文档TI官网

一、实验简介

- PWM产生脉冲,周期为10^-4

- 定时器0的timerA捕获下降沿次数,每记到10个脉冲就溢出,变量timer0A_cnt+=1

- 定时器1产生1s的中断,LED红蓝切换表示,检测这1秒钟内timer0A_cnt记录了多少次,并用串口输出(理论上每秒钟应该记到1000次捕获溢出)

二、TM4C123输入捕获介绍

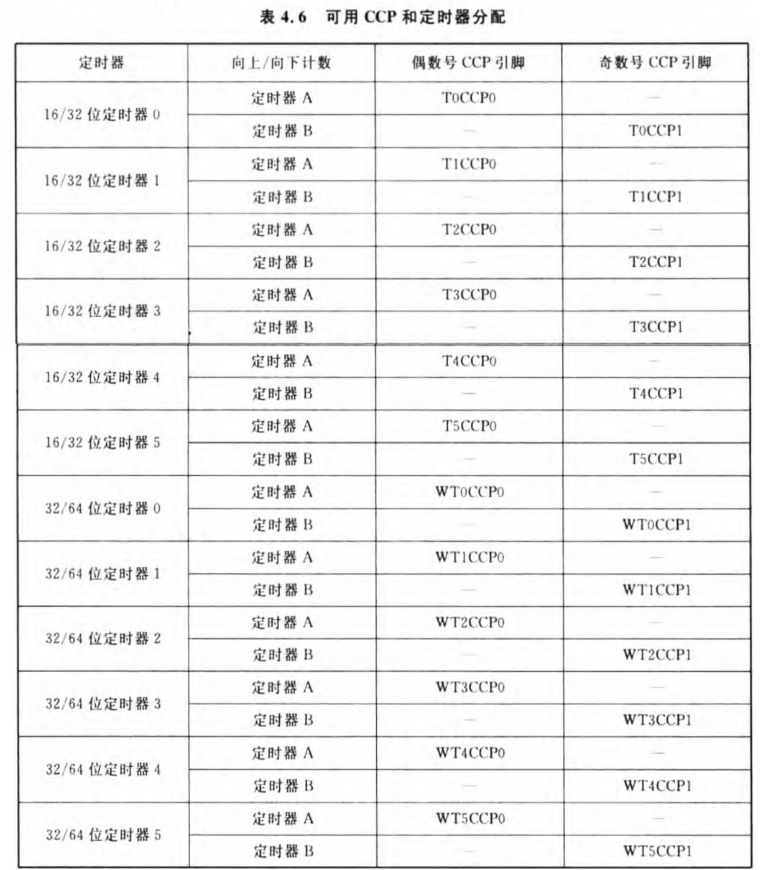

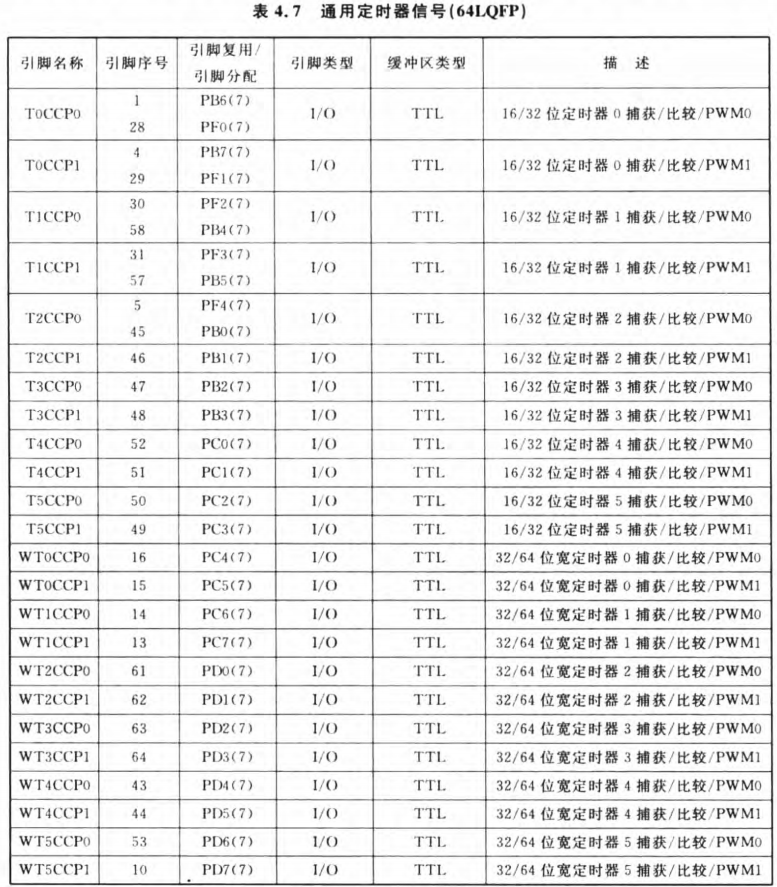

1、输入捕获引脚映射关系

2、两种输入捕获模式

以下内容提炼自TI Stellaris LM4F 定时器(Timer)指南,请务必先看这个,说的比较详细

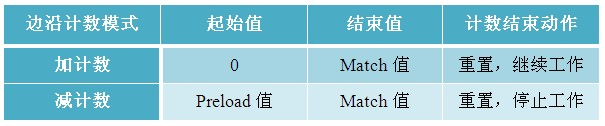

(1)边沿计数模式

-

简介:在该模式中,TimerA或TimerB被配置为能够捕获外部输入脉冲边沿事件的递增/减计数器。共有3种边沿事件类型:正边沿、负边沿、双边沿

-

工作过程是:

(1)减计数:设置装载值Preload,并预设一个匹配值Match(应当小于装载值);计数使能后,在特定的CCP管脚每输入1个脉冲(正边沿、负边沿或双边沿有效),计数值就减1;当计数值与匹配值Match相等时停止运行(若使能中断,这时会被触发)。定时器自动重装载Preload值,但如果需要再次捕获外部脉冲,则要重新进行配置。

(2)加计数:设置匹配值Match;计数使能后,在特定的CCP管脚每输入1个脉冲(正边沿、负边沿或双边沿有效),计数值就加1;当计数值与匹配值Match相等时停止运行(若使能中断,这时会被触发)。定时器自动清0并自动开始捕获外部脉冲计数,不需要重新进行配置

-

注意:

- 配置为边沿计数模式时,定时器必须配置为拆分模式,64-bit未拆分模式下不可以用Capture

- 此模式下,8bit的定时器预分频寄存器(Prescaler)不再作为分频器使用,定时器频率和系统时钟频率相同, 预分频寄存器的8bit空间作为计数范围的扩展,增加到定时器计数器的高位。也就是说32/64位定时器的输入捕获计数范围为24/48bit

-

配置过程:

GPIO设置:GPIOPinConfigure进行引脚到TnCCPm的信号映射GPIOPinTypeTimer配置引脚到定时器模式GPIOPadConfigSet配置其他引脚参数

配置定时器模块为捕捉-边沿计数模式

4.TimerConfigure配置定时器模式。注意第二个参数一定是TIMER_CFG_SPLIT_PAIR和一下之一相或

(1)TIMER_CFG_A_CAP_COUNT模块A捕捉-边沿减计数模式

(2)TIMER_CFG_A_CAP_COUNT_UP模块A捕捉-边沿加计数模式

(3)TIMER_CFG_B_CAP_COUNT模块B捕捉-边沿减计数模式

(4)TIMER_CFG_B_CAP_COUNT_UP模块B捕捉-边沿加计数模式设置要捕捉的边沿

5.TimerControlEvent设置计数范围

6.TimerMatchSet设置加/减计数结束值

7.TimerLoadSet设置减计数起始值中断设置

8.TimerIntRegister注册中断服务函数

9.TimerIntEnable源级中断使能,这里注意配置中断类型

(1)TIMER_CAPA_MATCH– 模块A计数到达预设值

(2)TIMER_CAPB_MATCH– 模块B计数到达预设值

10.IntEnable中断控制器级中断使能

11.IntMasterEnable处理器级中断使能启动定时器模块

12.TimerEnable

(2)边沿计时模式

-

简介:在该模式中,TimerA/B被配置为自由运行的16位递减计数器,允许在输入信号的上升沿或下降沿捕获事件。

-

工作过程是:设置装载值(默认为0xFFFF)、捕获边沿类型;计数器被使能后开始自由运行,从装载值开始递减计数(或从0开始递增计数),计数到0(或装载值)时重装(或清零),继续计数;如果从CCP管脚上出现有效的输入脉冲边沿事件,则当前计数值被自动复制到一个特定的寄存器里,该值会一直保存不变,直至遇到下一个有效输入边沿时被刷新。为了能够及时读取捕获到的计数值,应当使能边沿事件捕获中断,并在中断服务函数里读取。

-

注意:

- 配置为边沿计时模式时,定时器必须配置为拆分模式,64-bit未拆分模式下不可以用Capture

- 此模式下,8bit的定时器预分频寄存器(Prescaler)不再作为分频器使用,定时器频率和系统时钟频率相同, 预分频寄存器的8bit空间作为计数范围的扩展,增加到定时器计时器的高位。也就是说32/64位定时器的输入捕获计时范围为24/48bit

-

配置过程:和计数模式基本一样,仅有以下区别

需要配置定时器模块为捕捉-边沿计时模式TimerConfigure第二个参数是TIMER_CFG_SPLIT_PAIR和一下之一相或

(1)TIMER_CFG_A_CAP_TIME模块A捕捉-边沿减计时模式

(2)TIMER_CFG_A_CAP_TIME _UP模块A捕捉-边沿加计时模式

(3)TIMER_CFG_B_CAP_ TIME模块B捕捉-边沿减计时模式

(4)TIMER_CFG_B_CAP_ TIME _UP模块B捕捉-边沿加计时模式

设置计时范围

2.TimerLoadSet无论加计时还是减计时,都用这个函数设置Preload值中断设置

3.TimerIntEnable的中断类型参数变为以下二者之一

(1)TIMER_CAPA_EVENT模块A发生捕获事件

(2)TIMER_CAPB_EVENT模块B发生捕获事件

三、示例代码

以下为开头提出实验的输入捕获部分程序

//timer0A输入捕获,脉冲从PB6输入(PF0作T0CCP0)

int timer0A_cnt=0;

void Timer0Init()

{

// 启用Timer0模块

SysCtlPeripheralEnable(SYSCTL_PERIPH_TIMER0);

// 启用GPIO_F作为脉冲捕捉脚

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

// 配置GPIO脚为使用Timer4捕捉模式

GPIOPinConfigure(GPIO_PB6_T0CCP0);

GPIOPinTypeTimer(GPIO_PORTB_BASE, GPIO_PIN_6);

// 为管脚配置弱上拉模式(捕获下降沿,配置为上拉)

GPIOPadConfigSet(GPIO_PORTB_BASE, GPIO_PIN_6, GPIO_STRENGTH_2MA, GPIO_PIN_TYPE_STD_WPU);

// 配置使用Timer4的TimerA模块为边沿触发加计数模式

TimerConfigure(TIMER0_BASE, TIMER_CFG_SPLIT_PAIR | TIMER_CFG_A_CAP_COUNT_UP);

// 使用下降沿触发

TimerControlEvent(TIMER0_BASE, TIMER_A, TIMER_EVENT_NEG_EDGE);

// 设置计数范围为0~9

TimerMatchSet(TIMER0_BASE, TIMER_A, 10-1); //理论匹配周期10^-4*10=0.001s

// 注册中断处理函数以响应触发事件

TimerIntRegister(TIMER0_BASE, TIMER_A, Timer0AIntHandler);

// 系统总中断开

IntMasterEnable();

// 时钟中断允许,中断事件为Capture模式中边沿触发,计数到达预设值

TimerIntEnable(TIMER0_BASE, TIMER_CAPA_MATCH);

// NVIC中允许定时器A模块中断

IntEnable(INT_TIMER0A);

// 启动捕捉模块

TimerEnable(TIMER0_BASE, TIMER_A);

}

//中断服务函数 理论周期:0.001s

void Timer0AIntHandler(void)

{

TimerIntClear(TIMER0_BASE, TIMER_CAPA_MATCH);

timer0A_cnt++;

}

经测试,每秒钟记录捕获溢出次数1002次,误差为千分之二

最后

以上就是昏睡大山最近收集整理的关于TM4C123G学习记录(7)--输入捕获一、实验简介二、TM4C123输入捕获介绍三、示例代码的全部内容,更多相关TM4C123G学习记录(7)--输入捕获一、实验简介二、TM4C123输入捕获介绍三、示例代码内容请搜索靠谱客的其他文章。

发表评论 取消回复