本文主要介绍五种同步触发器,简单提及主从触发器和边沿触发器。

0,SR锁存器(基本RS触发器)重点

SR锁存器可以由与非门或者或非门构成。它是各种触发器电路形式最简单的一种,也是以后所有的基本组成部分。

或非门有1出0同时为0才出1.与非门有0出1,同时为1才出0.

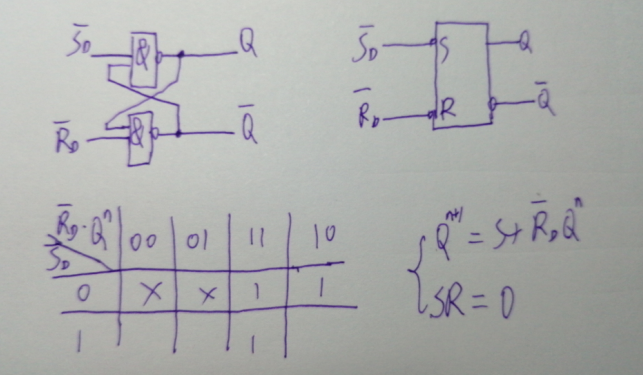

与非门构成的SR锁存器

次态不仅仅与当前的输入有关,还有与当前的状态有关。这里有一点,Sd和Rd不能同时为1。同时为1在电路中是一种错误的逻辑,不能满足两个输出互非。

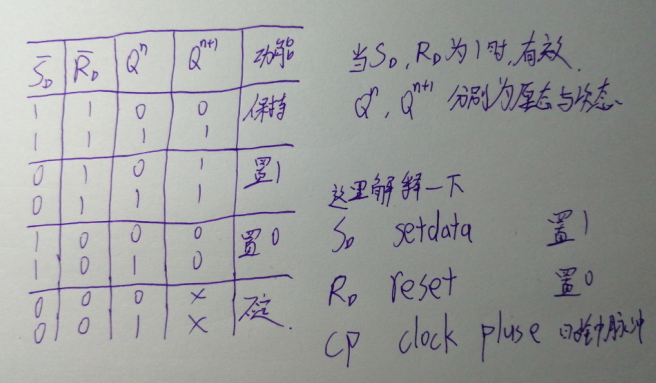

或非门构成SR锁存器

这里有没有发现,其实两个逻辑门不同,但是咱们的结果却时一样的!!!

这里解释下不定这个状态,在两个同时为1时,具体电路考虑上下两个门电路的时延,来决定具体的输出。

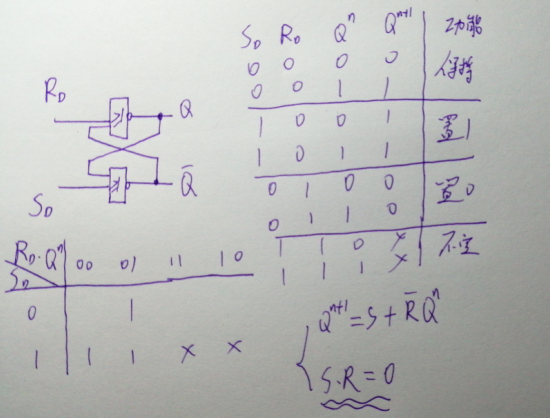

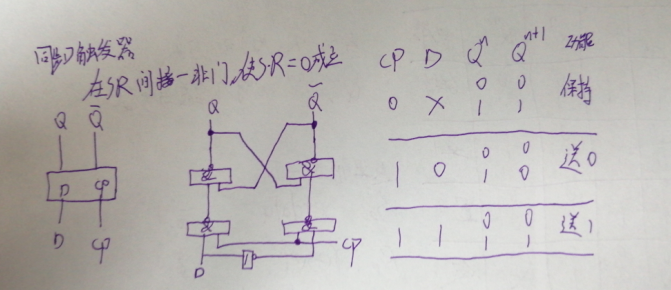

1,同步RS触发器

这里引入了CP。clock pulse。像心脏一样,脉搏,一下一下的跳动,控制触发器。这里同样没有解决输入不能全部为0这个问题,接下来的D触发器将会解决这个问题。

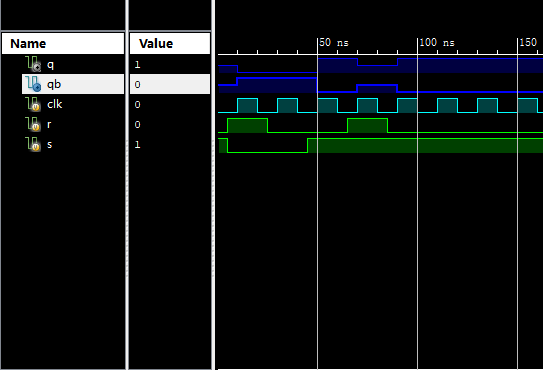

RS触发器的代码实现

module SY_RS_FF(clk,r,s,q,qb

);

input clk;

input r;

input s;

output q;

output qb;

reg q;

assign qb = ~q;

always@(posedge clk)

begin

case({r,s})

2'b00:q <= q;

2'b01:q <= 1'b1;

2'b10:q <= 1'b0;

2'b11:q <= 1'bx;

endcase

end

endmodule

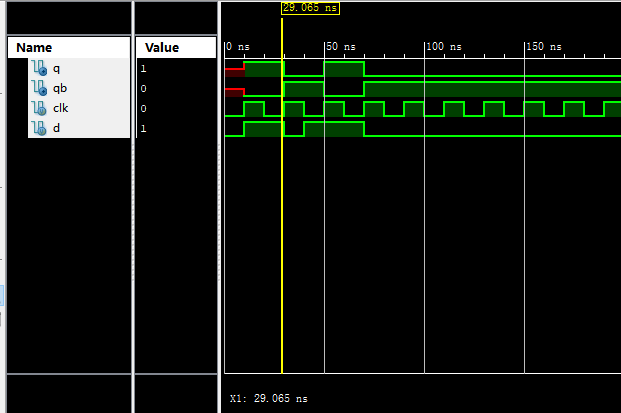

这里给一个仿真截图,激励可以自己随意给尽量每一个都取到。

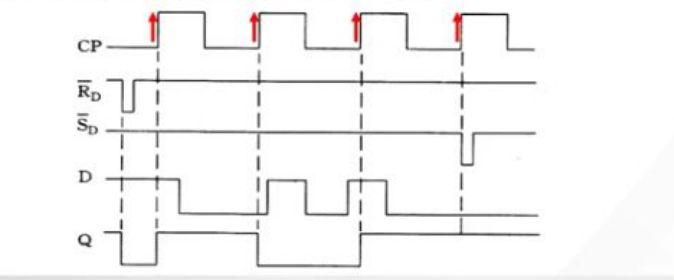

2,同步D触发器(D锁存器)

前面的问题还记得吗,两个输入不能同时为1,D触发器改变了这一问题。但也带来了新的问题。

从双端输入变为了单端输入。因此就又有了下面的触发器,既解决了双端输入,又解决了输入不能同时为1这种情况

代码实现

module SY_D_FF(clk,d,q,qb

);

input clk,d;

output q,qb;

reg q;

assign qb = ~q;

always@(posedge clk)

begin

q <= d;

end

endmodule

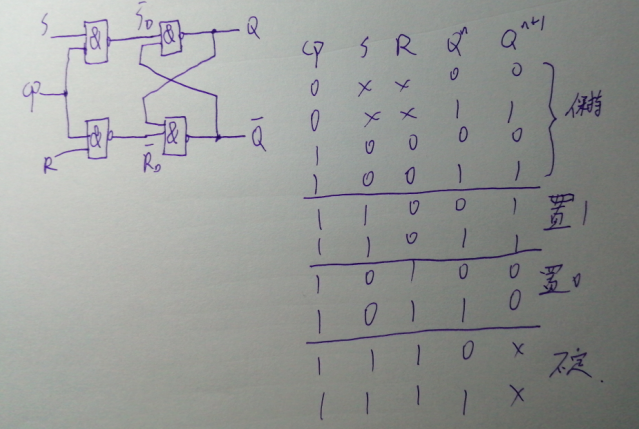

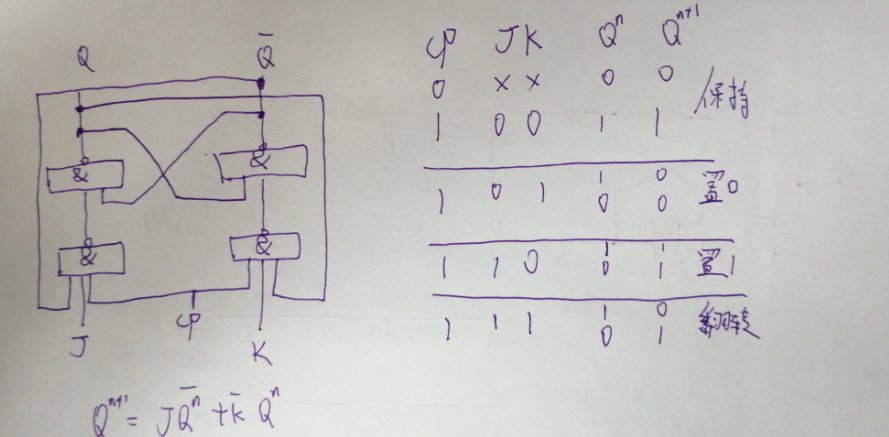

3,同步JK触发器

他是将最终的输出引回输入端解决不能同时为1这个问题的。

这里的翻转对时钟频率有一定的要求,否则会不停的翻转。

代码实现

module SY_JK_FF(clk,j,k,q,qb

);

input clk,j,k;

output q,qb;

reg q;

assign qb = ~q;

always@(posedge clk)

begin

case({j,k})

2'b00:q <= q;

2'b01:q <= 0;

2'b10:q <= 1;

2'b11:q <= ~q;

endcase

end

endmodule4,同步T触发器

5,同步T`触发器

这两个触发器是在同步JK下的特殊情况。jk相同,为T触发器。JK相同且仅为1是T`触发器

module SY_T_FF(clk,r,t,q,qb

);

input clk,r,t;

output q,qb;

reg q;

assign qb = ~q;

always@(posedge clk)

begin

if(r)

q <= 0;

else if (t)

q <= ~q;

else

q <= q;

end

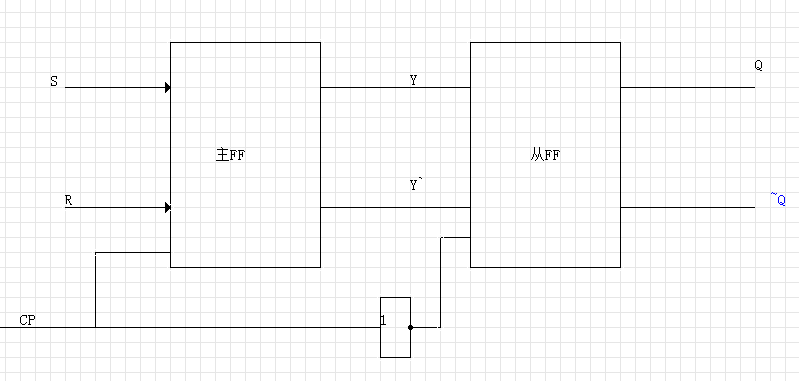

endmodule6,主从触发器

主从触发器是为了解决空翻现象。空翻是指在CP为高脉冲期间,输入信号的多次变化引起输出信号多次变化的现象,这里一般为外界的干扰。所以引入了主从触发器来解决这个问题。

主触发器是同步触发器,从触发器是边沿触发,将主触发器状态输出。(但主触发器依旧是无法抗干扰,于是出现了边沿触发)

7,边沿触发器

维持阻塞正边沿D触发器

最后

以上就是粗心小甜瓜最近收集整理的关于fpga数电基础之--------触发器的全部内容,更多相关fpga数电基础之--------触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复