简单的可乐贩卖机

- 1.状态机

- 2.时序图

- 3.代码

- 3.1 代码中的注意事项

- 4.vivado时序图

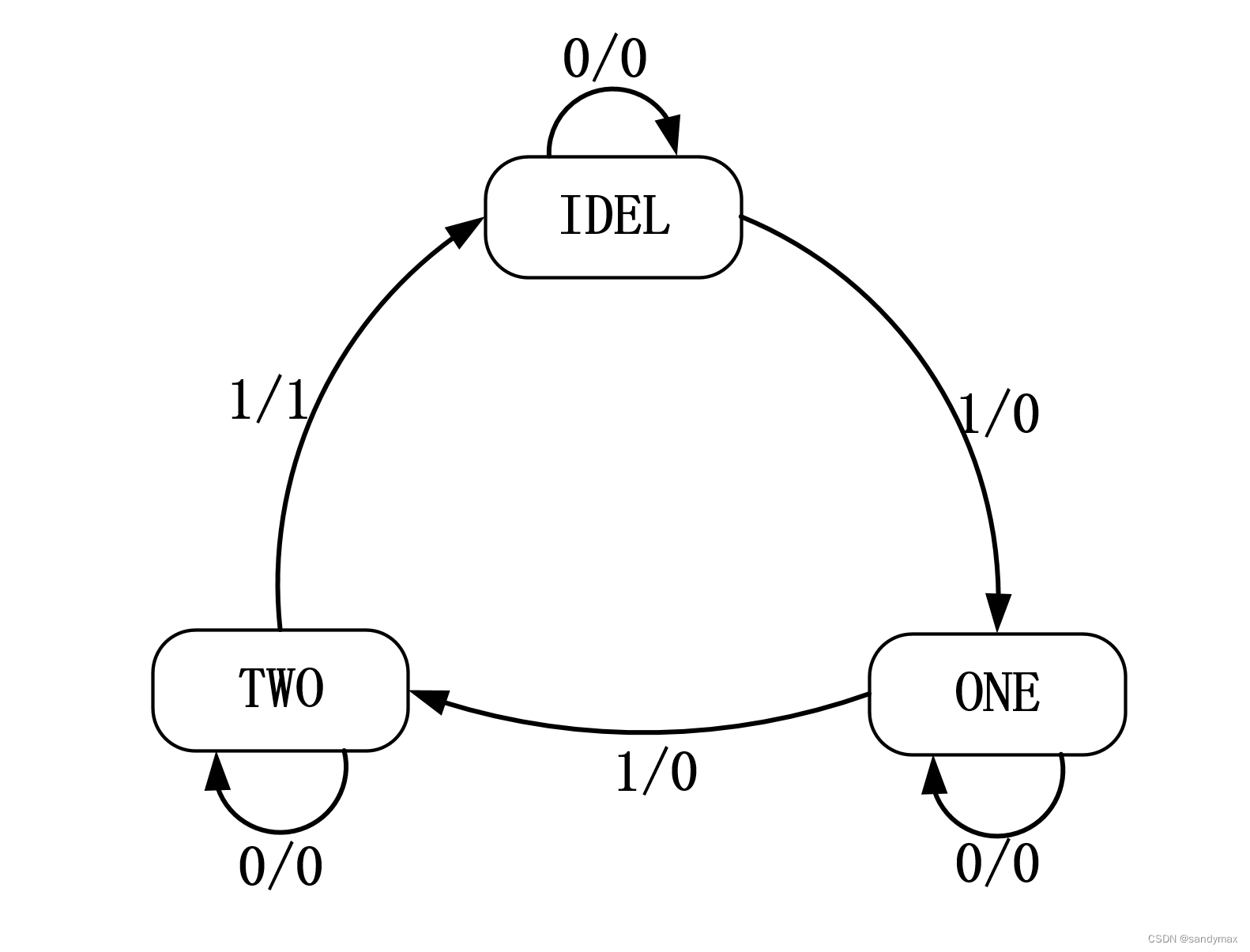

1.状态机

贩卖机中投入三块钱后就可以出1瓶可乐

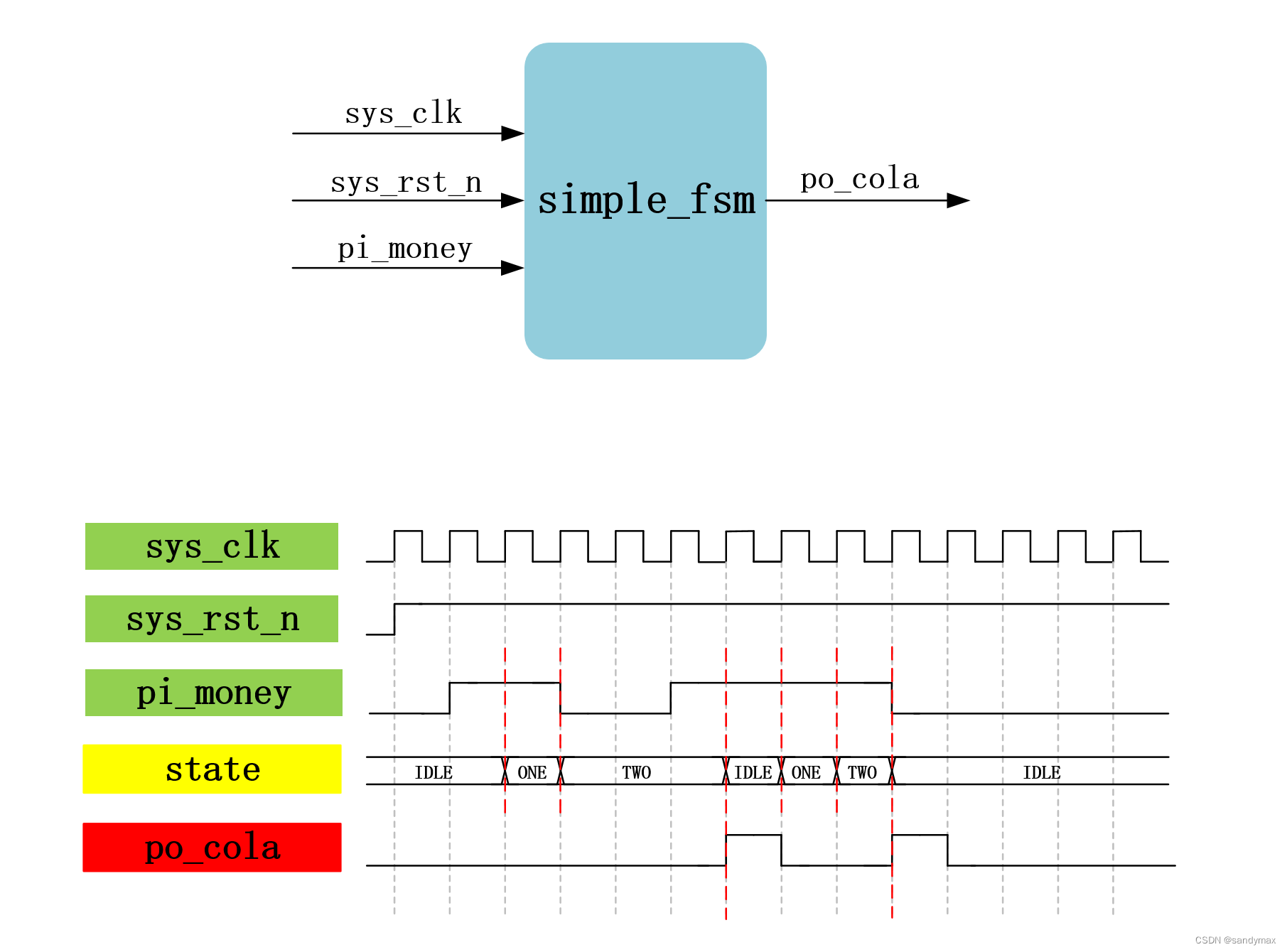

2.时序图

3.代码

simple_fsm.v文件

module simple_fsm

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire pi_money ,

output reg po_cola

);

parameter IDLE = 3'b001;

parameter ONE = 3'b010;

parameter TWO = 3'b100;

reg [2:0] state;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

state <= IDLE;

else case(state)

IDLE: if(pi_money == 1'b1)

state <= ONE;

else

state <= IDLE;

ONE: if(pi_money == 1'b1)

state <= TWO;

else

state <= ONE;

TWO: if(pi_money == 1'b1)

state <= IDLE;

else

state <= TWO;

default: state <= IDLE;

endcase

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

po_cola <= 1'b0;

else if((state == TWO) && (pi_money == 1'b1))

po_cola <= 1'b1;

else

po_cola <= 1'b0;

endmodule

tb_simple_fsm.v文件

`timescale 1ns/1ns

module tb_simple_fsm();

//声明变量

reg sys_clk;

reg sys_rst_n;

reg pi_money;

wire po_cola;

//初始化

initial

begin

sys_clk = 1'b0;

sys_rst_n <= 1'b0;

//pi_money <= 1'b0;

#20

sys_rst_n <= 1'b1;

/* #10

pi_money <= 1'b1;

#40

pi_money <= 1'b0;

#40

pi_money <= 1'b1;

#80

pi_money <= 1'b0; */

end

//系统时钟初始化,周期为20ns

always #10 sys_clk = ~sys_clk;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

pi_money <= 1'b0;

else

pi_money <= {$random} % 2;

wire [2:0] state = simple_fsm_inst.state;

//显示初始化

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t: pi_money=%b,state=%b,po_cola=%b",$time,pi_money,state,po_cola);

end

//实例化

simple_fsm simple_fsm_inst

(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.pi_money (pi_money),

.po_cola (po_cola)

);

endmodule

3.1 代码中的注意事项

显示 state 时的语句

$monitor("@time %t: pi_money=%b,state=%b,po_cola=%b",$time,pi_money,state,po_cola);

需要的赋值形式

wire [2:0] state = simple_fsm_inst.state;

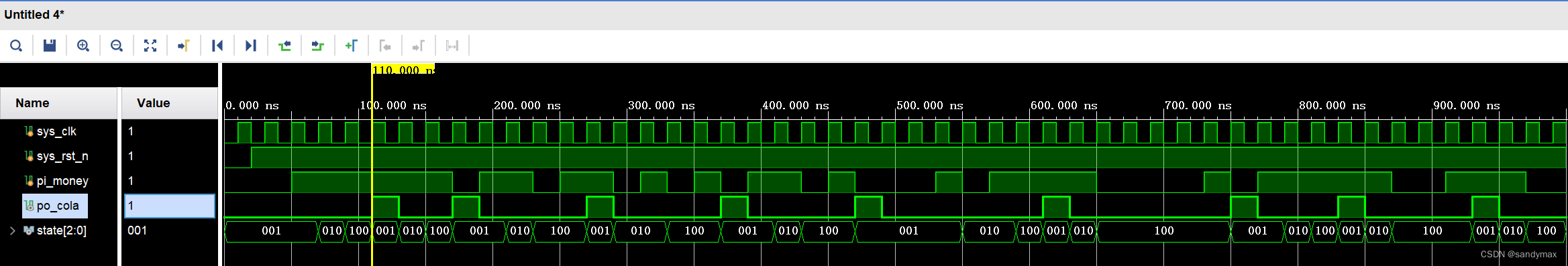

4.vivado时序图

最后

以上就是激昂巨人最近收集整理的关于Verilog中的状态机1.状态机2.时序图3.代码4.vivado时序图的全部内容,更多相关Verilog中内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复